金刚石光子学已使金刚石量子存储器的高效、高保真度接口成为可能,并预计将在模块化量子网络中发挥关键作用。然而,可扩展的网络架构需要对由量子存储器发射或指向的光子进行空间、时间和光谱控制,这反过来依赖于金刚石本身无法提供的非线性和电光功能。在此,我们展示了将具有强 χ-2 非线性和电光效应的薄膜铌酸锂(TFLN)平台与薄金刚石薄膜进行异质集成的实验。我们演示了高品质因数的金刚石光子晶体腔(在735纳米下Q因子超过5×10⁴),这些腔体通过光刻与TFLN光子骨干对准,并与其关键耦合。这使我们能够实现低损耗的金刚石-TFLN“电梯”(损耗约为1 dB/耦合器),支持金刚石和TFLN层之间的高效光传输。通过在低温(5K)下操作我们的平台,我们展示了通过TFLN光子电路收集嵌入金刚石结构中的硅空位(SiVs)发射的光子。通过将薄膜金刚石与TFLN结合,这种方法为集成光子电路的可扩展路径提供了基础,可用于实际的量子网络和其他技术。划重点--销售晶圆和加工#光子晶体腔电子束光刻刻蚀加工SOI晶圆:--220nm薄膜/ 3um厚膜-3umSIO2-675um

ALOOI晶圆;--氧化铝薄膜晶圆,键合工艺和镀膜工艺

TAOOI晶圆--氧化钽薄膜晶圆,镀膜工艺

SINOI晶圆--超低损耗氮化硅薄膜晶圆,210nm-300nm-400nm-800nm

SICOI晶圆;新型量子光学平台500nm-700nm-1um

8寸LTOI晶圆批量供应;铌酸锂的有力的竞争对手,薄膜钽酸锂晶300600

6寸X切Z切掺镁薄膜铌酸锂晶圆 ,厚膜 3um 5um 和 薄膜 100-600nm

8寸LNOI晶圆;8寸LNOI助力更大规模薄膜铌酸锂产品量产

LN/LT-SOI/Si/SIN W2W&D2W异质集成

流片: 6寸 氮化硅 铌酸锂 硅光 超高性价比流片, 1个BLOCK的价格买一整片晶圆

划重点--全国产-超高性价比-6 寸硅光-氮化硅-铌酸锂流片白皮书

我们为客户提供晶圆(硅晶圆,玻璃晶圆,SOI晶圆,GaAs,蓝宝石,碳化硅(导电,非绝缘),Ga2O3,金刚石,GaN(外延片/衬底)),镀膜(PVD,cvd,Ald,PLD)和材料(Au Cu Ag Pt Al Cr Ti Ni Sio2 Tio2 Ti3O5,Ta2O5,ZrO2,TiN,ALN,ZnO,HfO2。。更多材料),键合(石英石英键合,蓝宝石蓝宝石键合)光刻,高精度掩模版,外延,掺杂,电子束光刻等产品及加工服务(请找小编领取我们晶圆标品库存列表,为您的科学实验加速。

请联系小编免费获取原文

引言

引言

金刚石色心凭借其可光学调控且寿命长的自旋量子比特,已成为可扩展量子网络的领先候选者。最近,使用氮空位和硅空位中心演示的多模纠缠和长距离链接凸显了该平台的潜力。然而,实际的量子网络不仅仅需要自旋量子比特:它还需要开关、调制器、频率转换器和其他光子组件。金刚石本身缺乏执行这些操作所需的非线性和电光(EO)功能。因此,朝着大规模、高性能网络的进展不仅依赖于金刚石器件的进步,还依赖于通过低损耗接口与互补平台的集成。薄膜铌酸锂(TFLN),具有极低的光学损耗、强的光学非线性和大规模可制造性,最近已成为高性能非线性光子学和光电子学的领先平台。TFLN还具有与其他光子材料(如硅氮化物(SiN)和金刚石)进行异质集成的潜力。

先前将金刚石与其他光子平台集成的方法依赖于几种不同的转移和粘接方法。在“挑选和放置”方法中,金刚石器件(包括光子晶体腔和波导阵列)首先在金刚石上制造,然后被取出并转移到另一个光子平台上。转印法依赖于一个模具来拾取金刚石薄膜或已制造的结构,并将其压印到另一个光子平台上。最后,翻转芯片粘接方法使用芯片粘接机将金刚石薄膜粘接到另一个平面基板上,使用金属或其他粘接剂。根据选择的转移方法或转移结构,可能需要粘接剂。挑选和放置法以及翻转芯片粘接通常需要一些“胶水”,这可能会导致短波长下的损耗或发光。转印法可以在某些条件下实现直接粘接。为了最小化损耗,首选低损耗粘接剂或无需粘接剂。所实现的平台通常在金刚石发射器和光之间具有渐逝耦合或直接耦合,这取决于光主要是在金刚石内传播还是在周围材料中传播。后者通常具有更强的耦合和更好的从发射器收集光子的效率,因此更为理想。

TFLN器件通常依赖于一种肋状波导模式,其中包括一层未刻蚀的铌酸锂(“板”)并在其上方沉积金属电极,以确保高效的电光控制。该“板”与铌酸锂波导中常见的非垂直侧壁相结合,使得从芯片中高效地耦合光(通过光栅耦合器、边缘耦合器或锥形光纤耦合器)变得困难。这个限制进一步推动了TFLN与其他材料之间直接高效耦合的开发。

在集成TFLN和金刚石时,需要考虑几个关键方面以评估该方法的可行性。(1)可扩展性、可重复性和产量:该过程应理想地允许并行制造具有一致性能的器件,并具有稳健的制造过程,可以可靠地重复。(2)保持材料和器件质量:集成应保持金刚石腔体的高光学Q值和操作波长,以及嵌入的色心的光学和自旋相干性。它还应保持TFLN电路的完整性。(3)高耦合效率和金刚石纳米光子腔与铌酸锂波导之间的模式匹配:这需要在接口处对锥形过渡部分进行工程设计,并实现近乎完美的对准,这对于量子应用至关重要。

我们提出了一种异质集成方法,将最先进的金刚石光子晶体(PhC)腔体与TFLN电路结合,使用薄膜金刚石的转印法和光子结构的光刻对准。在我们的方法中,首先制造TFLN光学电路,包括光波导、Y型分路器和光栅耦合器(GC),所有组件都在约740 nm的波长下工作。在一侧,TFLN波导具有夹层过渡结构,夹层区域未刻蚀,用于金刚石安装。接着,使用直接粘接方法将薄膜金刚石转移到这些安装区域。然后,使用电子束光刻(EBL)和反应离子刻蚀(RIE)的组合制造金刚石光子晶体腔。重要的是,EBL写入的金刚石梁与耦合过渡部分对准到底下的TFLN电路,我们预期金刚石与TFLN耦合过渡部分之间有非常精确的对准。对准误差的技术限制约为25 nm,由使用的EBL工具(Elionix ELS-7000;标称重叠精度为25 nm)决定,从而使我们能够制造高效的TFLN-金刚石电梯。

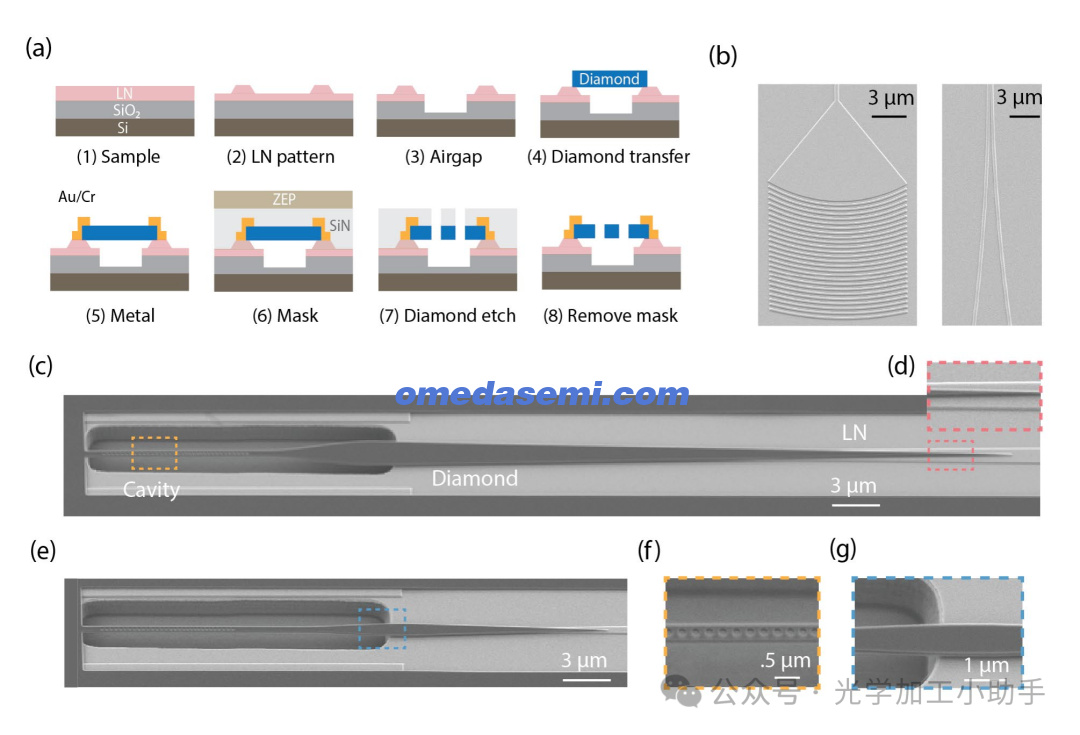

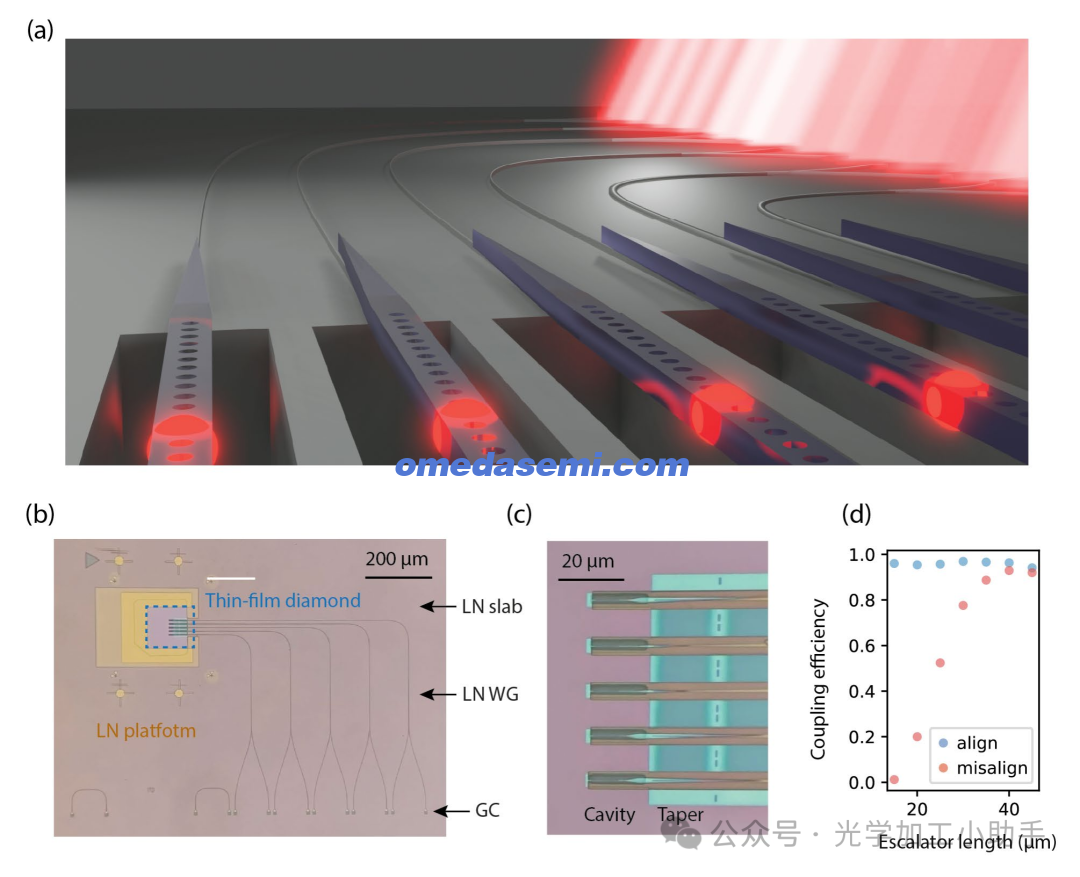

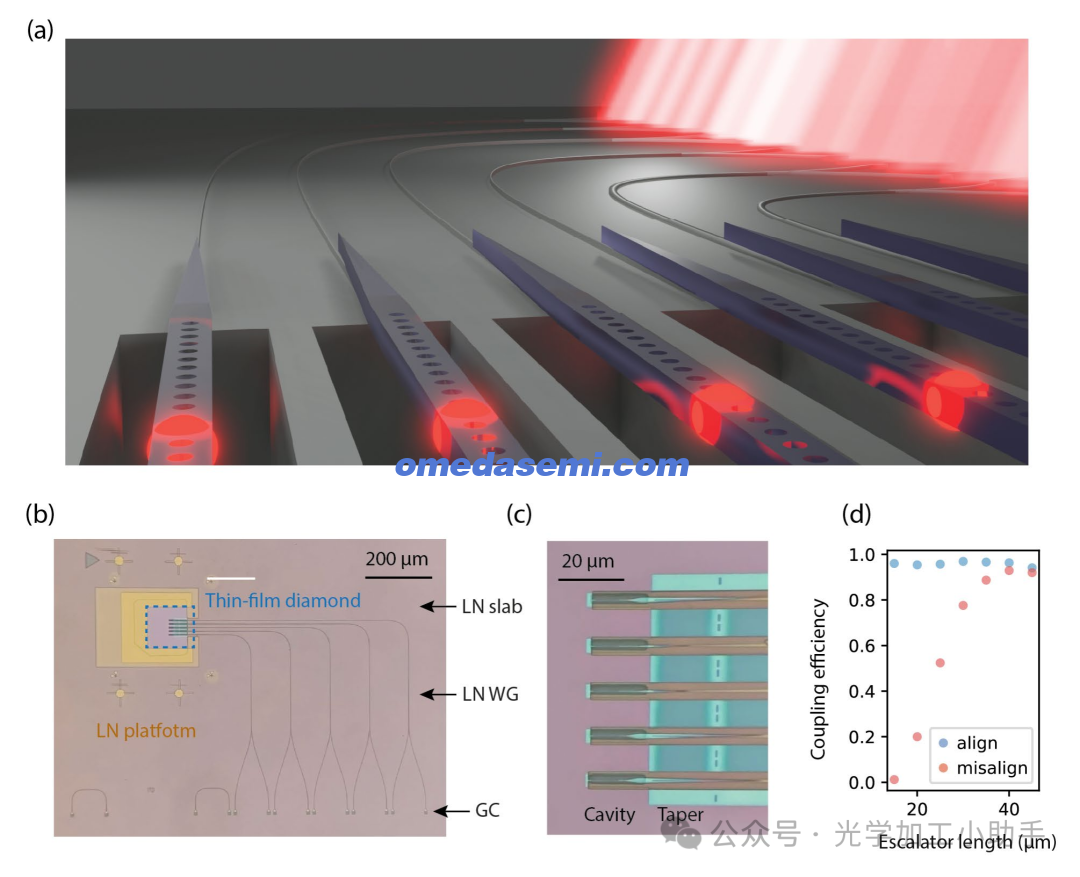

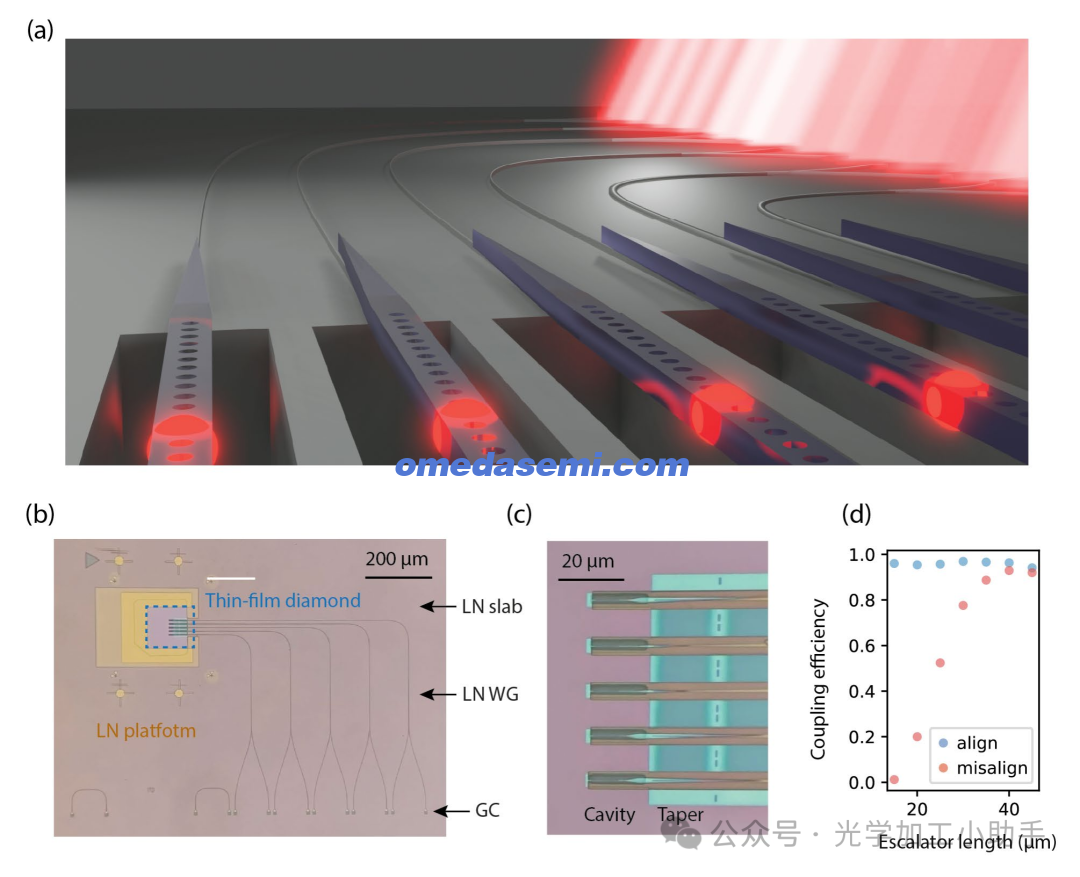

图1.

图1.

(a) LN-金刚石光子平台的示意图。由SiV发射的光子被自由悬挂的高Q金刚石光子晶体腔体或波导捕获,通过高效的LN-金刚石双渐变电梯传输到LN,并通过光栅耦合器耦合出去,光栅耦合器的中心波长约为740 nm。

(b) 制造的器件的显微镜图像。浅粉色区域是LN“板”,较深的线条是LN肋状波导。虚线框表示金刚石薄膜被转移到LN平台的区域。金刚石通过金属“贴纸”固定,如黄色所示。

(c) 不同长度的金刚石光子晶体腔体和金刚石-LN电梯的放大图像。腔体悬挂在一个凹槽上。

(d) 长金刚石过渡部分的电梯耦合效率的模拟图,假设完美对准和100 nm的横向错位。当没有错位时,耦合效率接近96±1%,但当有错位时,效率会随着过渡部分的缩短而迅速下降,从35 µm处的93%降到10 µm处的1%。

如图1(a)所示,最终制造的金刚石PhC腔体阵列悬挂在凹槽上,这些凹槽被刻蚀到TFLN和SiO2中。嵌入金刚石结构中的硅空位(SiVs)发射的光子通过电梯传输到TFLN芯片,并最终通过光栅耦合器耦合出去,经过Y型分路器。我们的方法还使得器件阵列的并行制造成为可能,主要受限于薄膜金刚石的尺寸。预计随着生长和转移技术的成熟,薄膜金刚石的尺寸将增大。

在本工作中,我们制造了五个金刚石PhC腔体,所有腔体都展示了目标共振(平均误差0.33%)并具有高质量因子(Q值),与先前在金刚石平台上的最先进结果一致。735 nm处的临界耦合腔体达到了5.3×10⁴的Q值(散射Q值约为1.1×10⁵)。金刚石-LN电梯的效率在775 nm时测得高达91%(-0.42 dB/电梯)。我们在低温(5K)下对平台进行了表征,并观察到通过LN光栅耦合器收集硅空位(SiV)发射的光子,以及高Q腔体模式反射凹槽。通过将金刚石和TFLN结合并实现低损耗,该平台提供了将量子材料与非线性和电光功能集成的路径,朝着量子网络及更广泛的应用迈进。

器件设计与概念

为了保持可见光TFLN和金刚石器件的性能,我们决定围绕用于可见波长的最先进TFLN调制器和高Q金刚石腔体所使用的材料堆栈来设计电梯。如图1(b)所示,我们制造了五组器件。在每组中,左端有一个金刚石PhC腔体,如图1(c)所示。右侧是由金刚石和铌酸锂波导宽度逐渐变窄形成的电梯,随后是一个LN单模波导段,接着是一个Y型分路器和两个光栅耦合器。所有组件都设计用于737 nm附近的波长,即SiV的零声子线(ZPL)。

金刚石PhC腔体是悬挂的并且是单面耦合的,仅与波导的一侧耦合。该反射型PhC腔体设计是基于SiV的量子存储节点的核心。腔体使用FDTD电磁仿真设计,具有与我们先前工作相同的设计参数:梁的宽度和厚度分别为370 nm和160 nm;孔半径为65 nm;晶格常数变化以针对730 nm、740 nm和740 nm处的基本TE模式;对于740 nm,单位单元长度为255 nm。

LN波导、光栅耦合器和Y型分路器的设计使用FDTD电磁仿真(Tidy3D)进行,波长约为740 nm。X切割LN层厚度为200 nm,位于3 μm的SiO2上,后者位于Si基片上。由于LN的刻蚀具有特征侧壁角度60°,这一点在仿真和后续设计中已考虑。波导宽度(顶部宽度330 nm)和厚度(100 nm刻蚀深度和100 nm“板”厚度)选择以确保单模操作并避免因材料的高双折射性而在LN波导弯曲处发生TE/TM耦合。这使得我们能够保持光在芯片上的偏振,这对于避免光栅耦合器/光纤接口的偏振相关损耗以及确保金刚石PhC腔体的正常操作至关重要。后者仅具有TE带隙,因此只能耦合或反射TE偏振光用于检测。我们注意到,在我们的设计中,任何剩余的TE/TM耦合都会降低电梯耦合效率并导致光子损失。最终,该几何形状与可见波长TFLN电光调制器平台兼容,因此适用于电极集成进行主动控制。

光栅耦合器的周期为465 nm,工作周期为31%,旨在实现740 nm附近的最大耦合效率,适用于角磨光纤(-8°)。光栅耦合器水平间距为127 μm(如图1(b)所示),以与用于耦合光进出芯片的光纤阵列兼容。电梯效率通过回切法进行测量,从而去除与光栅耦合器相关的损耗。电路故意设计为分离激发和收集端口,以避免在表征过程中来自芯片底部的背向反射噪声。为此,我们使用了渐变Y型分路器,确保两个臂之间的均匀分配,并尽量减少额外的损耗(参见附录)。

电梯通过渐变LN-金刚石波导实现。虽然两种材料的折射率相似(约2.2与2.4),这应简化设计,但由于LN肋波导中未刻蚀的LN板的存在,情况变得复杂。LN过渡波导通过在40 μm长度内将LN波导顶部宽度从330 nm线性减小到40 nm来形成。

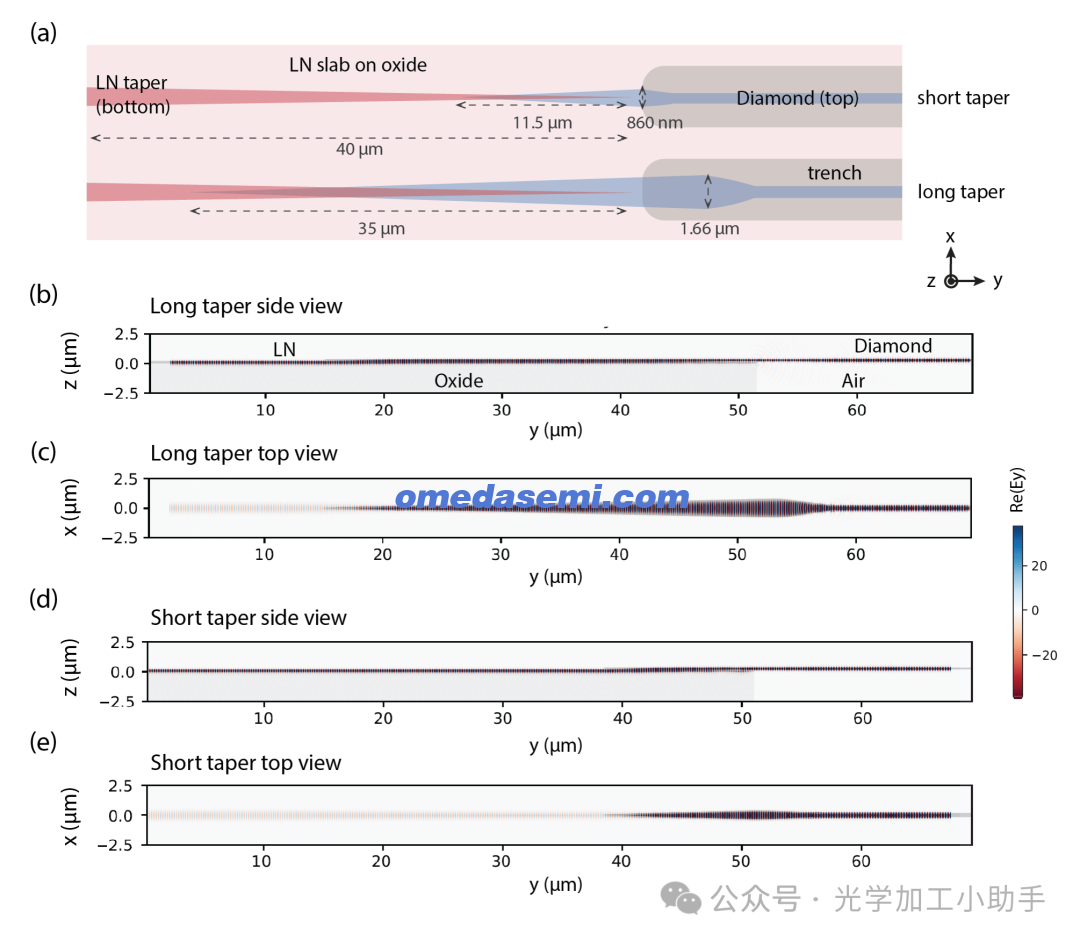

图2. LN和金刚石的异质集成:

图2. LN和金刚石的异质集成:

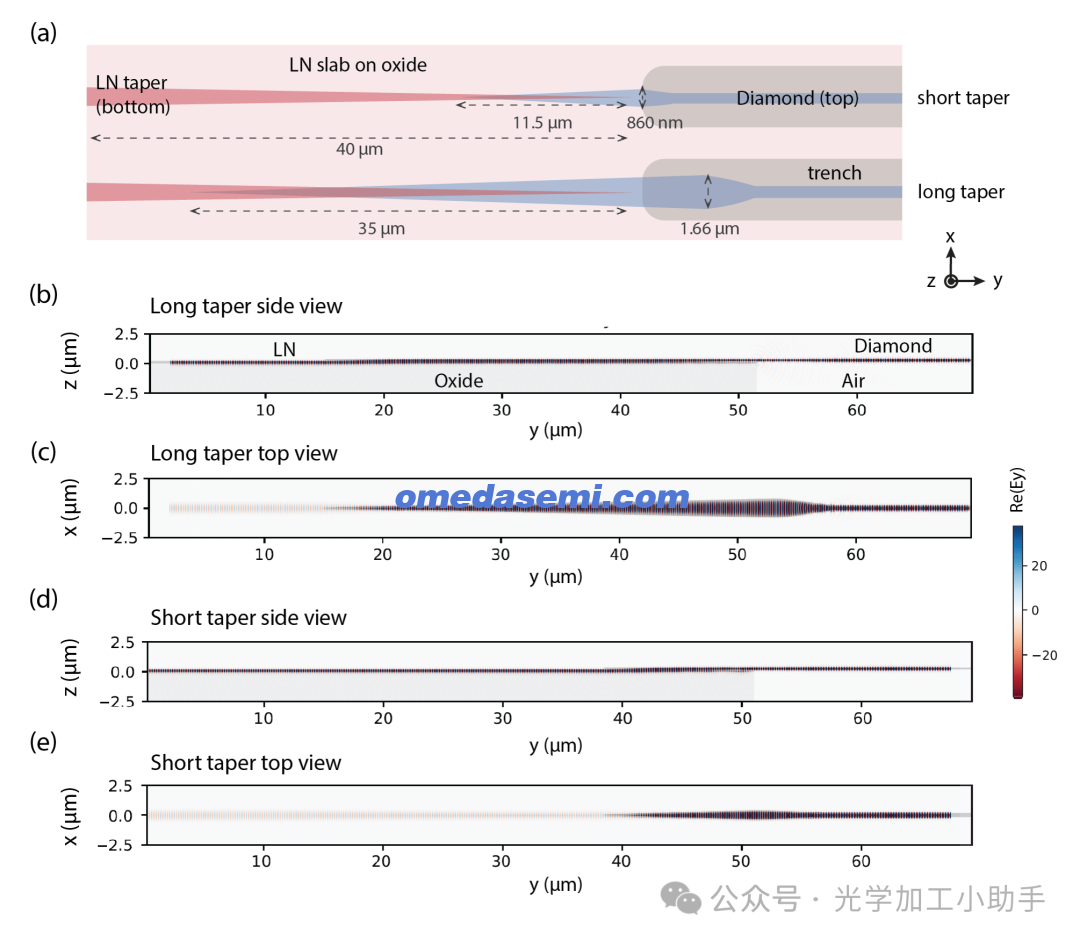

(a) 组成电梯的LN和金刚石过渡部分的几何示意图,包括长过渡和短过渡配置。

(b-e) 光在LN-金刚石界面上传播的场分布图,光在此过程中逐渐从LN模式转换为金刚石波导模式,分别展示长过渡和短过渡金刚石过渡的情况。长过渡(b, c)设计为能够容忍更多的错位,而短过渡(d, e)设计为减少长过渡中制造过程中引入的损耗。

在金刚石侧,我们采用了矛尖形状的过渡设计(如图2(a)所示)并考虑了两种不同的长度:长和短,长度分别为35 μm和11 μm。在长(短)过渡的情况下,金刚石波导宽度首先从60 nm增加到1.66 μm(860 nm),然后减少到370 nm。基于数值建模,两种设计都可以在770 nm时实现> 95%的耦合效率(参见附录中的其他波长)。矛尖形金刚石耦合器的选择也是为了增加对准容差。未对准时,长过渡的耦合效率更高,表明具有更大的对准容差。图1(d)展示了100 nm错位对不同长度过渡的模拟效果,这些过渡与LN过渡的重叠不同。长过渡设计如图2(b)和(c)所示,通过传播模式展示了金刚石和LN过渡之间的场分布。短过渡设计如图2(d)和(e)所示,当对准良好时,也可以实现高效率。测试两者的目的是了解对准容差与使用此方法时长过渡区域引入的额外散射损耗之间的权衡。

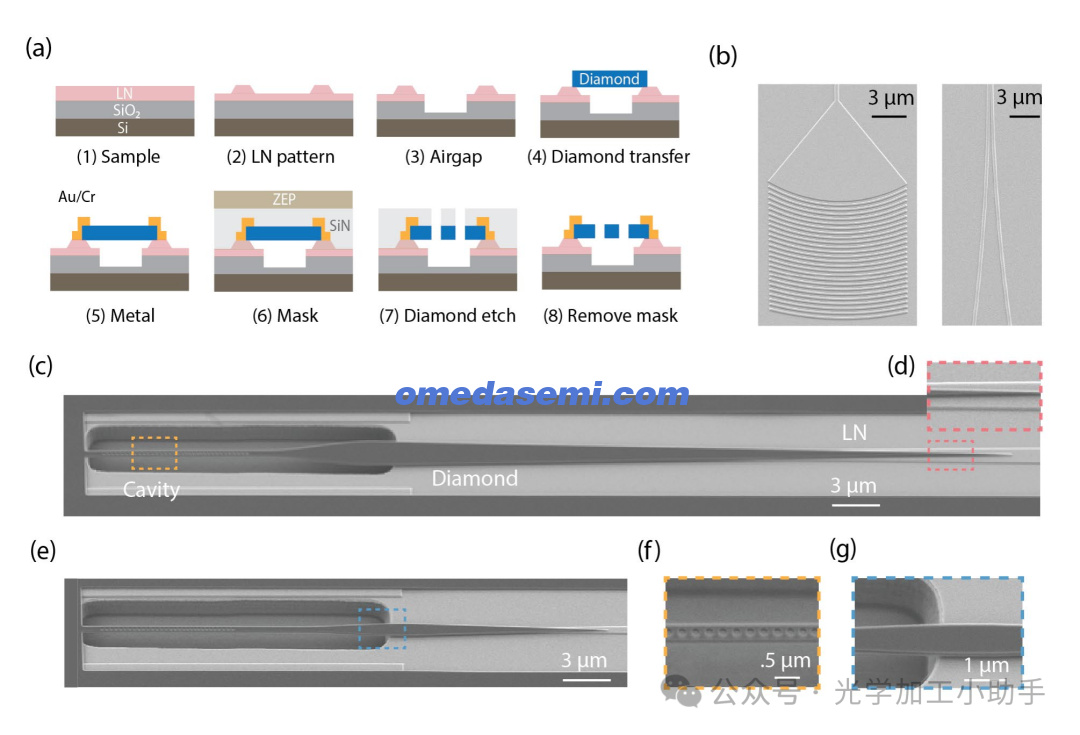

器件制造

器件制造从TFLN骨干电路开始。芯片首先在硅基片上沉积200 nm的铌酸锂(LN)薄膜,并覆盖3 μm的氧化硅层(图3(a)(1))。首先,使用电子束光刻(EBL)通过MAN电子束光刻胶定义LN电路,然后使用电感耦合等离子体(ICP)反应离子刻蚀(RIE)和氩气化学刻蚀。刻蚀深度为100 nm,留下100 nm厚的TFLN板(图3(a)(2))。

接下来,使用SPR220-3.0和光学光刻定义沟槽,并与先前通过EBL定义的结构对齐。随后使用氩气和C3F8进行RIE刻蚀,通过LN并刻蚀超过1 μm的SiO2(图3(a)(3))。

接着,200 μm x 200 μm的薄膜金刚石(厚度为160 nm)通过转印工艺转移到平台上,并且仅需最小的对准要求(图3(a)(4))【17】。转移后,样品使用丙酮清洗,以去除转移过程中残留的污染物。为了确保粘接并保持TFLN的完整性,样品在空气中于400°C退火(见附录)。作为制造异质芯片的第一步,沉积200 nm厚的Cr/Au层以固定膜结构,如图3(a)(5)所示。在未来应用中,LN调制器的电极也可以在此步骤中定义,而不会干扰后续步骤。然后,金刚石制造遵循已知的工艺【21】,其中腔体通过EBL和O2的RIE刻蚀来定义,如图3(a)(6)和(7)所示。最终步骤使用BOE 7:1去除SiN掩模,进一步切割金刚石梁下方的氧化物。所得的芯片具有悬挂的金刚石PhC腔体,并通过渐变耦合到带有100 nm板的LN光子电路中(图3(a)(8))。

制造的器件如图3(b)-(g)所示。LN上的组件看起来平滑,没有明显的缺陷(图3(b))。金刚石腔体与LN过渡结构对齐良好,无论是在长过渡(图3(c))还是短过渡(图3(e))设计中。对准误差与SEM图像中的测量误差在同一量级,符合标称的EBL重叠误差<30 nm。对金刚石过渡部分(图3(d))、腔体(图3(f))和沟槽(图3(g))的详细检查未发现明显的制造缺陷或未解释的设计偏差。然而,确实存在一些小但显眼的缺陷(SEM图像见附录)。在薄膜金刚石的边缘,有一条薄线(约50 nm),可能是转印剂的残留物,未完全清洗干净。金刚石的O2刻蚀也在暴露于写入步骤中的LN上产生了一个浅凹痕(约<10 nm)。这些缺陷会导致散射损耗,这将包含在电梯耦合效率的测量中。另一个缺陷出现在器件5上,显示了一个意外的错位实例:在这种情况下,湿法工艺(BOE)将写入并对准良好的过渡部分从尖端脱落,并略微倾斜,使得金刚石过渡部分略微旋转或弯曲,中心位于金刚石波导的某个位置。

电梯耦合效率和腔体表征

通过将超级连续白光通过一个光栅耦合器(GC)发送,并测量从金刚石腔体反射的光,来表征不同波长下的耦合效率。更具体地说,数据通过光纤阵列在光栅耦合器上采集,并使用光谱分析仪(OSA)进行分析,光纤阵列在每次波长扫描之间自动在器件之间移动并重新对准。

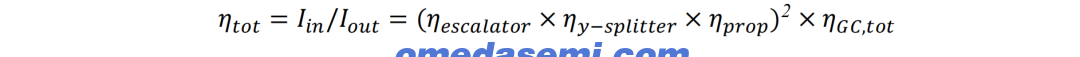

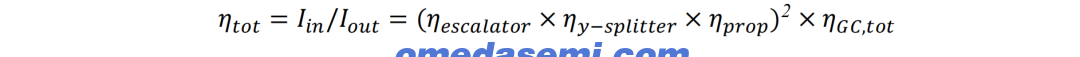

金刚石PhC被设计为具有700-800 nm范围内的TE带隙,在所有器件中都充当电路末端的反射器。我们可以通过测量光栅耦合器前后光强度来提取电梯的耦合效率,并减去光栅耦合器、Y型分路器和传播损耗。换句话说,作为波长的函数,总效率ηtot(λ)为:

损耗计算

损耗被计算了两次,因为光被反射回来并且遇到界面或损耗两次。ηescalator包括光子传输效率和金刚石PhC与LN波导之间的模式匹配。电路设计上将激发和收集端口分开,以避免来自回反射的噪声,因此使用了Y型分路器。它在这个波长范围内引入了模拟的ηy-splitter为每通过3.1 dB(见附录)。总光栅耦合器损耗ηGC,tot可以使用回切法进行校准,在该方法中,收集短光栅耦合器回路的光谱,并从测量中减去。传播损耗可以通过测量同一芯片上不同长度的参考器件来计算。LN传播损耗ηLN是通过在相关波长下的波导测量提取的,给出了0.3 dB/mm的损耗(见附录)。

图3. LN和金刚石光子晶体腔的制造:

图3. LN和金刚石光子晶体腔的制造:

(a) 制造流程的示意图。

(b) 制造的LN光栅耦合器(左)和Y型分路器(右)。光栅耦合器图像中的别名效应是显示伪影,并非实际器件上的。LN的刻蚀深度为100 nm,堆叠为100 nm。波导上没有可见的粗糙度。

(c)(e) 使用不同过渡设计制造的两个金刚石腔体-LN界面。SEM图像是在30度倾斜角度下拍摄的。由于金刚石尖端非常薄,几乎对电子透明(白色)。这可能会给人一种尖端错位的错觉,但放大图像显示,两个过渡部分都对准良好。

(d) 金刚石(深色)和LN(浅色)过渡部分重叠的放大图像。错位量最小。

(f) 金刚石光子晶体腔体悬挂在LN-SiO₂沟槽上的放大图像。

(g) 金刚石模式转换器悬挂在LN边缘上的放大图像。金刚石腔体或波导上没有可见的粗糙度。

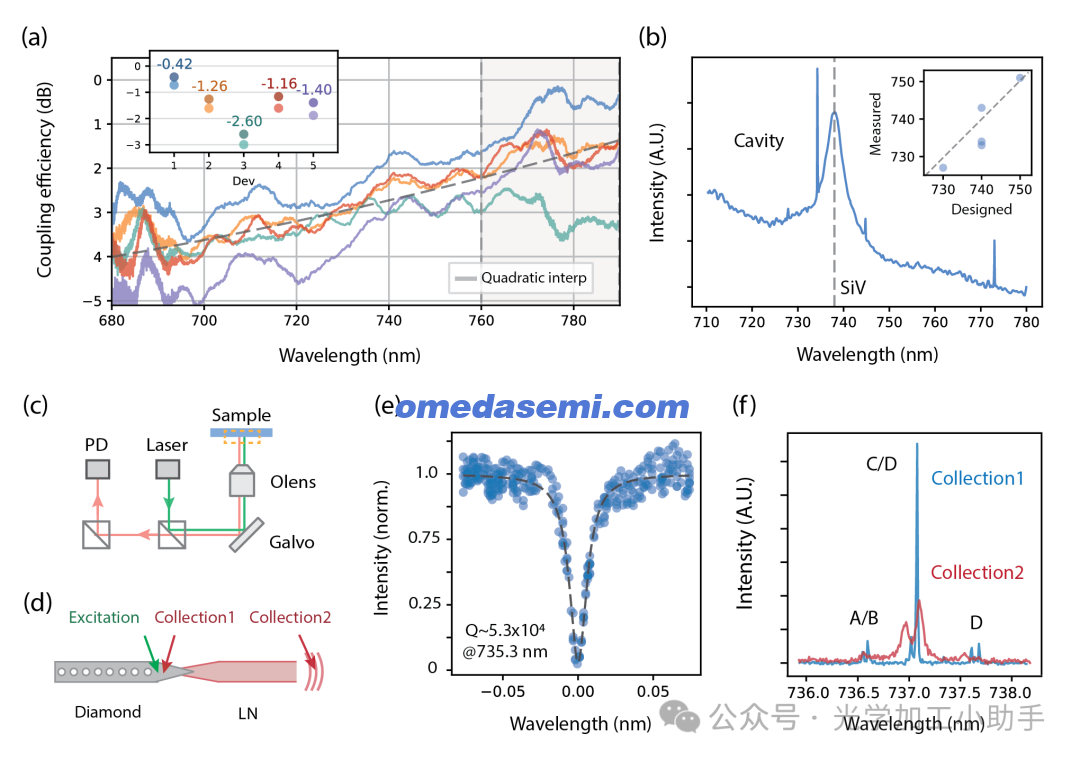

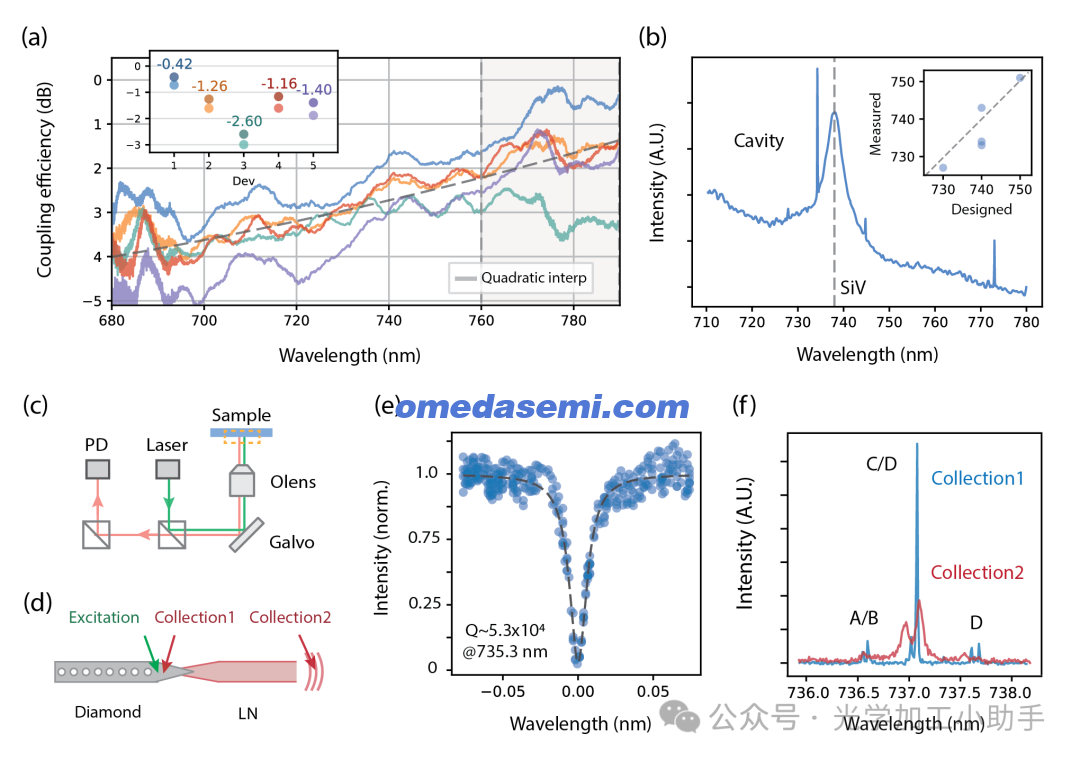

测量的耦合效率ηescalator + ηLN在680-800 nm范围内如图4(a)所示,适用于5组器件(原始数据见附录)。这些数据是两次连续扫描的平均值,用来考虑设置的功率和光学对准的漂移。由于光栅耦合器回切校准方法和测量设置会在测量光谱中引入振荡伪影,因此我们引用在适度波长窗口范围内平均的耦合效率作为更具代表性和有意义的性能指标。

我们注意到耦合效率随着波长的增加而增加的趋势。这表明电路或电梯中可能存在与散射相关的损耗机制。在建模中,这种电梯设计在该波长范围内显示出非常小的波长敏感性(长过渡或对准的短过渡)或相反的趋势(错位的短过渡),如附录所讨论。在LN波导传播损耗的测量中,波长的依赖性也不那么强,因此不是主导因素(更多细节见附录)。对于损耗α,单位为dB/长度,可能存在几种损耗通道:(1)瑞利散射:如果损耗由非常小的颗粒或缺陷主导,损耗为α~1/λ⁴;(2)侧壁粗糙度(Payne-Lacey):侧壁上的粗糙度贡献于损耗,和波长反比,通常在某些假设下会导致像α~1/λ²的标度【23】。因此,基于所有测量曲线的二次插值被叠加到图4(a)中的曲线中,作为视觉指导。

在我们的芯片中,器件3和4具有短过渡,而器件1、2和5具有长过渡。事实证明,器件1、2和4表现出相似的反射光谱特征和更高的耦合效率,表明当错位不是主导损耗机制时,短过渡和长过渡都很优秀,这与仿真结果一致。器件3有更平坦的光谱和更高的损耗。这可能表明短过渡部分存在轻微错位,除了先前识别的损耗机制之外。我们在SEM下未观察到明显的错位(<~50 nm),但较短的设计对小的错位更敏感,可能正是因此造成了问题。器件5是表现最差的长过渡器件。我们确实观察到该过渡有些倾斜,并且上面有一些碎屑(来自掩模的SiN薄膜)。

在峰值附近,即775 nm(760到790 nm),提取了芯片上的“原始”耦合效率ηescalator + ηLN和“修正”后的ηescalator,正如图4(a)插图所示。

图4. 制造样品的表征:

图4. 制造样品的表征:

(a) 五个过渡耦合器件的芯片内耦合效率(ηescalator + ηLN)光谱。效率以dB/面表示。所引用的耦合效率适用于760-790 nm范围,如虚线和阴影区域所示。插图:每个器件的提取耦合效率,分别显示考虑LN传播损耗(芯片内,深色)和不考虑(修正,浅色)的情况。标注的值为修正后的电梯效率,已考虑LN传播损耗。

(b) 器件1的金刚石腔体测量光谱。虚线表示SiV位置为737 nm,基频腔体模式是左侧的锐峰,位于735 nm。插图显示了测量的共振波长与设计值(单位:nm)进行对比,所有五个器件之间的匹配非常接近。

(c) 器件5K表征的光学设置。绿色(532 nm)用于激发。红色(737 nm)通过收集路径收集。Olens:物镜,20x或100x;Galvo:振镜;PD:光电二极管。

(d) 电路上激发和收集位置的示意图。

(e) 在735 nm处的腔体反射光谱,通过激光扫描共振并使用光栅耦合器(GC)或收集点2测量。

(f) 从收集点1和2收集的SiV零声子线(ZPL)信号的光谱。

最佳器件1显示ηescalator可达-0.42 dB,它具有长过渡。最佳短过渡器件的ηescalator = -1.26 dB。这意味着长过渡更为稳健,对制造缺陷不那么敏感,并且通常表现更好。

在检查了电梯特性后,我们还在室温下表征了金刚石腔体。腔体光谱是通过收集SiV和金刚石中其他无意缺陷(如NVs)的光致发光(PL)获得的,当腔体被垂直激发光照射时,类似于我们先前工作的测量方法【21】【24】。图4(b)显示了旨在针对737 nm的腔体的光谱。所测得的五个腔体的共振频率,分别设计为730、740(3个器件)和750 nm,与设计共振频率紧密匹配,如图4(b)插图所示。平均误差为0.33%,与未使用TFLN骨架的金刚石薄膜制造一致。腔体显示出高Q值(>20k),除非腔体设计上并不特别过耦合,并且受限于光谱仪的分辨率。为了完全解析金刚石光子晶体腔体的共振特征,并验证异质设备是否适用于低温操作,我们继续在5 K下对芯片进行测量。

通过电路的SiV表征(5K)

对于5K低温光学系统,我们使用100倍物镜,数值孔径为0.95,进行共焦观测SiVs,并使用20倍物镜,数值孔径为0.4,实现良好的耦合到光栅耦合器(GCs),并提供宽广的视场。两种配置的实验设置如图4(c)所示。这两种设置对应于两种不同的收集点:金刚石腔体/悬挂波导(高NA,收集点1)或相应的GC(低NA,收集点2),如图4(d)所示。

为了评估低温下腔体的性能,我们首先在LN光栅耦合器(收集点2)处表征了737 nm的器件共振频率。对腔体共振频率进行了精细激光扫描,并监测了反射信号。测得的光谱如图4(g)所示。该器件的质量因子为5.28×10⁴,已与LN电路关键耦合,并显示出98%的共振深度。从中提取的总散射限制Q约为1.1×10⁵,与未使用TFLN骨架的金刚石薄膜腔体的最先进值一致。这证实了集成过程即使在低温环境下也能保持金刚石腔体的优良性能。

随后,我们对植入金刚石器件中的SiV进行了光致发光(PL)表征。在此测量中,使用了两个收集点:我们用532 nm的连续波激光激发金刚石腔体/悬挂波导,并收集737 nm的SiV零声子线(ZPL),可以选择共焦方式(收集点1)或通过相应的GC(收集点2)收集,这样就远离了激发光,如图4(d)所示。

从SiV的群体发射可以通过收集点1和收集点2都观察到。图4(f)显示了两者的光谱,ABCD峰值对应SiV ZPLs。这些结果确认了SiV发射可以成功地通过电梯和LN电路传播。比较这些光谱,我们观察到通过LN光栅耦合器的收集点2显示出类似SiV特征的光谱,但线宽较宽。可能有两个解释:(1)收集点2可能包括沿金刚石波导和过渡部分分布的许多SiV的贡献,它们的发射耦合到相应的GC并未通过共焦方式检测;(2)我们注意到通过低NA透镜的绿色激发不那么有效,因此光谱的积累时间较长(180秒而不是30秒),并且使用了更高的功率(100 µW而不是~10 µW)。然而,根据C线波长,这一因素可能不那么显著【25】。

讨论与结论

我们展示了一个异质集成的金刚石-薄膜铌酸锂(TFLN)平台,该平台将最先进的包含金刚石色心的金刚石光子晶体腔与薄膜铌酸锂光子电路结合在一起。该集成通过转印工艺和光刻控制对准完成。这个方法解决了混合平台的关键性能指标:它是可扩展的,保持了金刚石和铌酸锂材料和器件的质量,并实现了高效的模式匹配接口。

我们的LN-金刚石电梯在775 nm处达到了高达-0.42 dB/电梯的传输效率。腔体在多个设计中显示出高产率,在与电路关键耦合时,达到了5.3 × 10⁴的Q值,散射限制的Q值约为1.1 × 10⁵,这与最好的独立金刚石腔体一致。在低温下,SiV群体通过共焦和芯片上的LN收集路径被检测到,确认该集成平台在5K下是功能性的,并能够传输SiV的发射。

除了展示集成TFLN和金刚石发射器的潜力,我们还指出了未来改进的几个方向:(1)通过使用更大的金刚石薄膜或多个转移的金刚石薄膜,我们可以在一次制造过程中实现更多的器件集;(2)可以改进金刚石与LN基板的附着力或转移过程,以防止过渡部分脱落并引入错位,并且避免电梯受到与转移残留物相关的散射损耗。这很可能填补最后1 dB的损耗差距,并提高产率;(3)正如SiV测量中所见,样品加热开始显现。对于我们测试芯片结构完整性来说,这不是问题;然而,对于涉及电极调节旋钮的未来应用来说,热管理变得更加关键。设计电路并优化安装策略以缓解这个问题对于量子应用至关重要;(4)基于已知的技术,如掩模植入法【1】,可以优化金刚石中SiV的位置和密度,以便将单一中心耦合到光子腔体中,具有高合作性,并且最小化波导/过渡区域中的浓度,以减少荧光背景。

总体而言,本文展示的结果确立了一条新的制造路径,解决了先前混合方法的局限性,并展示了一个高效、可扩展且兼容低温的薄膜金刚石和TFLN之间的接口。这为将金刚石自旋量子比特与铌酸锂的电光和非线性功能相结合的大规模集成电路开辟了道路,为先进的量子光子技术铺平了道路。

Heterogeneously Integrated Diamond–on-Lithium Niobate Quantum Photonic Platform

作者:Sophie W. Ding1,†, Chang Jin1, Zixi Li2, Nicholas Achuthan1, Kazuhiro Kuruma1,3, Xinghan Guo2, Brandon

Grinkemeyer4, David D. Awschalom2,5, Nazar Delegan5, F. Joseph Heremans2,5, Alexander A. High2,5,*,

and Marko Loncar1,*

单位:哈佛芝加哥东京大学mit

引言

引言 图

图 图

图