摘要

最近有报道称,热凝结工艺可以生产完全应变或放松的富锗(<50%)硅锗(SiGe)层,并将其嵌入氧化物层中。然而,为了提高量子效率并允许更薄的吸收层,同时保持与硅基技术的兼容性,要求更高的锗浓度。在这项工作中,我们报告了一种改进的热锗凝结工艺,能有效地在300 mm晶圆上大规模制备高质量的硅锗绝缘体(SGOI)层,且具有较高的关键锗含量(约85%)。该工艺从薄的外延SiGe层开始,通过在减少氧分压的条件下进行顺序高温氧化阶段,逐步增加锗浓度,同时保持结构完整性。研究了两种目标锗含量分别为约85%和约100%的样品。约85%锗含量的SGOI层表现出优异的晶体质量、均匀的锗深度分布,以及部分压缩应变,且未观察到位错。将凝结工艺扩展到近纯锗层时,出现形态不稳定,表现为凝结层的固态脱膜和单晶纯锗岛的形成。我们的研究结果表明,约85%的锗含量是通过热凝结法在大规模晶圆上获得连续无缺陷的SGOI薄膜的实际上限。超过此阈值后,通过脱膜释放应变限制了薄膜的均匀性和器件的适用性。这些结果为优化锗凝结工艺、实现高性能SGOI和锗绝缘体(GOI)基板在先进CMOS应用中的应用提供了关键见解。

SOI晶圆:--220nm薄膜/ 3um厚膜-3umSIO2-675umALOOI晶圆;--氧化铝薄膜晶圆,键合工艺和镀膜工艺

TAOOI晶圆--氧化钽薄膜晶圆,镀膜工艺

SINOI晶圆--超低损耗氮化硅薄膜晶圆,210nm-300nm-400nm-800nm

SICOI晶圆;新型量子光学平台500nm-700nm-1um

8寸LTOI晶圆批量供应;铌酸锂的有力的竞争对手,薄膜钽酸锂晶300600

6寸X切Z切掺镁薄膜铌酸锂晶圆 ,厚膜 3um 5um 和 薄膜 100-600nm

8寸LNOI晶圆;8寸LNOI助力更大规模薄膜铌酸锂产品量产

LN/LT-SOI/Si/SIN W2W&D2W异质集成

流片: 6寸 氮化硅 铌酸锂 硅光 超高性价比流片, 1个BLOCK的价格买一整片晶圆

划重点--全国产-超高性价比-6 寸硅光-氮化硅-铌酸锂流片白皮书

我们为客户提供晶圆(硅晶圆,玻璃晶圆,SOI晶圆,GaAs,蓝宝石,碳化硅(导电,非绝缘),Ga2O3,金刚石,GaN(外延片/衬底)),镀膜(PVD,cvd,Ald,PLD)和材料(Au Cu Ag Pt Al Cr Ti Ni Sio2 Tio2 Ti3O5,Ta2O5,ZrO2,TiN,ALN,ZnO,HfO2。。更多材料),键合(石英石英键合,蓝宝石蓝宝石键合)光刻,高精度掩模版,外延,掺杂,电子束光刻等产品及加工服务(请找小编领取我们晶圆标品库存列表,为您的科学实验加速。

请联系小编免费获取原文

文章名:Wafer-Scale integration of high-Ge content SGOI via hot condensation of Ge for Si-based applications作者:Adonis Steve Takala, Olivier Gourhant, Ismail Madaci, Christophe Duluard,Damien Monteil, Caroline Lacomme, Tony Printemps, Theo Levert, LucFavre, Isabelle Berbezier1. 引言

在半导体技术中,半导体器件的持续缩小是由摩尔定律驱动的,摩尔定律预测芯片上晶体管的密度大约每两年翻一番。在过去几十年里,这一发展促使了新策略的出现,以提升器件性能[1-4]。随着器件尺寸的缩小,为了应对短沟道效应并改善电静态控制,晶体管架构已经从平面二维结构发展到复杂的三维设计,如互补鳍式场效应晶体管(CFETs)[5,6]、全环门场效应晶体管(GAA FETs)[7,8]、鳍式场效应晶体管(FinFETs)[9]以及垂直场效应晶体管(Vertical FETs)[10]。在这些架构进展的同时,新的材料如高介电常数材料(high-k dielectrics)[11,12]和硅绝缘体(SOI)基板[13,14]在减少泄漏电流和提升器件效率方面发挥了关键作用。

与此同时,应变工程作为一种重要技术,通过调节材料的能带结构来提升电子和空穴的迁移率。自2000年代初引入以来,应变工程在弥补小尺度下载流子迁移率下降方面发挥了重要作用。特别是通过应变硅锗(SiGe)通道引入的压缩应变[15-17],显著提高了p型器件中的空穴迁移率,从而推动了低功耗、高性能计算集成电路的发展。对于n型器件,通常通过在放松的缓冲SiGe层上外延生长硅(Si)来诱导拉伸应变[15,18,19]。这一过程包括在大尺寸硅基片上沉积一层锗含量逐渐增加的梯度SiGe层,有效埋入位错并重新利用现有的位错来缓解应变。这导致了具有较大晶格常数、拉伸硅层的低缺陷密度表面,从而诱导了拉伸应变[20,21]。这种硅层中的拉伸应变提高了电子迁移率。据我们所知,已经证明通过在放松的SiGe缓冲层(RB)上生长的应变硅通道能够提高器件性能,且锗含量可达到60%[18,19,21-25]。然而,RB方法面临一些挑战,如精确控制SiGe层的厚度和锗含量、由于厚层(最大可达5微米)导致的晶圆翘曲、弯曲、开裂、长时间沉积和锗与硅之间的热膨胀不匹配。此外,在处理过程中,埋藏的位错可能迁移到表面,可能会影响器件的完整性[26]。

鉴于这些缺点,应用于外延生长在SOI基板上的SiGe层的锗凝结技术成为了一种有前景的替代方法。该方法首次由Tezuka等人于2001年提出,通过选择性热氧化硅将低锗含量(通常为10-25%)的SiGe层转化为富锗的SiGe绝缘体(SGOI)基板[27]。所谓“凝结”是指将锗含量从初始值x增加到更高值y(y>x),同时由于硅原子的优先氧化,SiGe层的厚度也会减少,锗原子被排斥并集中在剩余层中。使用SOI基板的这一技术具有多方面的优势。SOI晶圆中的埋氧层(BOX)提供了优异的电气隔离,并作为有效的扩散屏障,防止锗和硅原子的扩散,从而实现对氧化过程的精确控制。此外,BOX层有助于应变管理,这对于制造高质量、应变的SGOI层至关重要。

这种方法作为生产薄、应变、无缺陷的SGOI层的有前景的方法,兼容微电子制造工艺,已经引起了广泛关注。然而,由于持续的挑战,尤其是当目标锗含量超过60%时,仍未广泛应用于工业中,因为位错的形成导致的塑性应变释放成为了一个重要问题[28-33]。例如,Souriau等人报告称,通过优化凝结过程中的中间氩气退火,可以制造出高晶体质量、高空穴迁移率的基板(高达93%的SGOI)。然而,相反的趋势出现在电子迁移率上,电子迁移率大幅下降。此外,随着锗浓度的增加,界面陷阱密度和氧化物电荷密度也有所上升[34]。

高桥团队[35]提供了有关通过凝结工艺获得的富锗SGOI层中应变和缺陷演化的宝贵见解。他们研究了不同锗含量的SiGe层,具体为低于35%、介于35%和60%之间以及锗含量高于60%的SiGe层。研究结果表明,当锗浓度≥40%时,大的双轴应变导致通过位错成核的部分应变释放,这通过典型的交叉哈希表面形貌得到了证明。

Valenducq等人的近期研究[36]通过在氧化过程中降低氧分压,展示了在300毫米晶圆尺度上改善锗凝结工艺的方法。凝结SGOI层中的位错主要来源于锗浓度梯度陡峭,导致由于晶格不匹配产生显著的机械应变。最小化这些应力需要限制锗浓度的急剧变化。Valenducq等人采用了高温下的稀释N₂/O₂氧化气氛,以降低氧分压,从而减缓硅的氧化速率,而不改变氧化温度。这种控制氧化动力学的减少延长了氧化时间,为锗原子在SiGe和SOI层中的扩散和均匀化提供了足够的时间。因此,氧化界面处的锗浓度降低,缓解了由不匹配引起的应变。这一方法使得在300毫米晶圆上成功制造了高达49%锗含量的单晶、无位错SGOI层。然而,超过这个阈值后,表面粗糙度和交叉哈希图案重新出现,表明缺陷形成和塑性应变释放的开始。

Mallet等人[37]的进一步研究强调了严格控制初始SiGe层厚度和锗浓度对于抑制高锗含量SGOI层中的缺陷的重要性。电学表征证实了所制造SGOI结构的高电子质量。C–V和G–V测量显示常规的MOS响应,没有异常,表明BOX和SiGe/SiO₂界面具有良好的完整性,且内在SiGe薄膜中没有意外掺杂。温度依赖的I–V测量显示非常低的泄漏电流,与热电子输运通过势垒一致,排除了与缺陷相关的导电性。界面状态密度给出Dit ≈ 1.3 × 10¹¹ cm⁻²eV⁻¹,类似于初始SOI基板。然而,他们的工作主要针对锗含量约为54%的300毫米晶圆,且未出现缺陷生成。

本研究的目标是超越这个阈值(54%),通过研究优化的高温锗凝结工艺(称为“优化热凝结”)。目标是在300毫米晶圆上生产锗含量超过60%的优质晶体SGOI层,同时最小化塑性应变释放。我们系统地研究了氧化条件、锗浓度深度分布、应变演化、形貌变化和晶体质量在这些高锗含量层中的相互作用。工艺优化主要集中在根据锗含量调整凝结温度;随着锗含量超过50%,凝结温度逐渐降低。我们的结果为优化热凝结工艺提供了关键指导,以实现大规模制造高性能SGOI基板,适用于下一代CMOS应用。

2. 实验

为了准备图1-(a)所示的起始基板,使用了一块300毫米(001)硅绝缘体(SOI)晶圆,顶部硅层厚度为12纳米,埋氧层(BOX)厚度为25纳米。随后,通过在860°C下进行干燥炉氧化,将12纳米(001)SOI层厚度减少到8纳米,之后进行HF化学蚀刻处理。接下来,使用工业标准的减少压力化学气相沉积(RP-CVD)系统在SOI层上外延生长了20纳米Si1-xGex层(其中x=0.17)。在外延生长之前,进行了原位等离子体清洗,以确保SOI表面完全无SiO₂[38,39]。外延生长过程的参数,包括温度和前驱气体(DCS和GeH4)的流量比,经过优化,以确保SiGe层的无缺陷伪形长并具有良好的均匀性,覆盖整个300毫米晶圆。

为了评估晶圆级均匀性,通过光谱椭圆偏振(SE)映射对生长的外延SiGe层进行了表征,沿四条径向路径进行(见补充图1-(a)),使用了Nolot等人[40]提出的模型。测量结果显示,300毫米晶圆的厚度和锗含量具有出色的径向对称性(见补充图1-(b))。晶圆内的均匀性通过归一化范围量化,计算公式为(𝑚𝑎𝑥 ― 𝑚𝑖𝑛)∕ 𝑚𝑒𝑎𝑛,结果显示厚度变化约为7.25%,锗含量变化约为2.44%。这意味着厚度变化为0.05纳米/厘米,浓度变化为0.081%/厘米。据我们所知,这是当前最先进的均匀性。

基于这些结果,详细分析集中在两个代表性位置:晶圆中心和中半径位置。凝结后,锗浓度在晶圆中心最高[37],由于应变释放通常随着锗含量增加而增强,中心区域代表了维持晶体质量的最具挑战性的条件。因此,在中心区域展示良好的材料性能意味着晶圆其他区域具有可比或更好的质量。因此,研究重点放在了这个区域。

表面粗糙度通过原子力显微镜(AFM)表征,揭示了系统噪声限制内的均方根(RMS)粗糙度值(约0.1纳米),如补充图2-(a)所示,表明表面非常光滑。AFM图像中没有交叉哈希图案,表明没有错配位错,这一点通过补充图2-(b)中显示的局部透射电子显微镜(TEM)截面图得到了确认。

然后,锗凝结工艺通过在稀氧气氛中进行高温氧化来减少由于锗浓度梯度陡峭所导致的塑性应变释放,如引言中所述。在凝结过程中(图1-(b)),硅原子被选择性地氧化形成SiO₂,而锗原子则被排除在生长的氧化层之外。这一过程的独特之处在于它在非常高的温度下以非常低的氧气流量进行实施。温度升高期间发生的初步氧化防止了脱膜,而低氧气流量减缓了氧化动力学,允许SiGe和SOI之间发生相互扩散。结果,形成了更加稀释的SGOI合金,有效抑制了缺陷的生成。锗原子的扩散受到埋氧层(BOX)和顶氧化层(SiO2)的限制,从而在整个氧化过程中保持了SiGe层内的总锗量。因此,SGOI层中的锗含量增加,而其厚度减少(图1-(c))。该过程继续进行,直到SGOI层中的几乎所有硅原子都被氧化,最终产生了纯锗绝缘体(GOI)薄膜(Z=1)。

这种方法,称为“热凝结”,通过将0.5 slm O₂流量与16 slm N₂稀释,在工艺腔体内将氧分压保持在21托。为了避免超过硅₁₋ₓGeₓ合金的熔点,随着锗含量的增加,氧化温度会逐步降低,熔点会随之降低。具体而言,锗含量在17%至48%之间时,温度最初设置为1000°C;对于48%至80%的锗含量,温度降至950°C;对于80%至100%的锗含量,温度进一步降低到900°C,如图2所示。

为了全面评估热凝结工艺对SGOI层结构和成分特性的影响,采用了全面的表征技术。采用飞行时间二次离子质谱(TOF-SIMS)研究了元素组成和深度分布,精确绘制了层内锗分布。拉曼光谱被用来验证锗含量,并量化SGOI薄膜中的面内残余应变。测量使用532纳米激光激发源,在晶圆中心和中半径位置进行,激光功率较低(6 µW/µm²,x20物镜),以最小化热效应。拉曼光谱通过洛伦兹和高斯函数的组合进行拟合。通过考虑松弛的体锗虚拟基板作为参考,确定了拉曼位移。根据拉曼光谱,锗含量(x)通过Si-Ge和Ge-Ge模式的积分强度比值来确定,使用了公式[41,42]:

在我们的实验设置中,IGe-Ge和ISi-Ge分别是Ge-Ge模式和Si-Ge模式的强度。系数B在使用532纳米激光激发波长的情况下确定为1。

面内残余应变(𝜺//)通过以下公式计算[41,42]:

其中,𝜟𝝎𝑮𝒆是Ge-Ge模式相对于体材料的频率偏移,𝝎₀是体硅锗(SiGe)中的光学声子频率,p(x)和q(x)是变形势能,𝜸是泊松比。

SGOI层的表面粗糙度通过原子力显微镜(AFM)评估,揭示了纳米尺度的拓扑特征。高分辨率透射电子显微镜(HR-TEM)提供了晶体晶格和缺陷结构的详细局部成像,具有原子分辨率,同时,扫描透射电子显微镜结合能量色散X射线(STEM-EDX)则实现了化学分析。

3. 结果与讨论

设计了两个样品A和B,它们具有不同的目标锗浓度,以探讨该工艺在300毫米晶圆尺度下的能力和局限性。样品A的目标锗含量约为85%。选择该浓度是为了实现较高的锗富集度,同时保持结构完整性,并最小化塑性应变释放。以往的研究[25]表明,SiGe RB中锗含量约为这一水平(且缺陷形成有限)可以显著提高CMOS通道中的载流子迁移率,使其成为高性能器件应用的实际目标。样品B的目标是100%的锗含量,实际上生成纯锗绝缘体(GOI)层。这个目标将工艺推向其上限,以评估制造完全凝结的锗层的可行性,并理解与这种极端富集相关的结构和成分挑战。

热凝结工艺在三个连续的温度阶段(1000°C、950°C和900°C)下进行,氧化持续时间经过精确控制,逐步增加锗含量,同时避免熔化或层的降解。每个阶段的持续时间通过初步实验反复优化,并借鉴文献中报告的硅锗氧化速率模型[43,44]。表1总结了两个样品的初始外延层参数(厚度和锗含量)以及氧化条件。

表1:样品A和B的SiGe初始层参数和氧化条件。 锗浓度和层厚度分别给出了300毫米晶圆的中心和中半径位置。

凝结后,锗浓度的剖面通过TOF-SIMS、EDX和拉曼光谱进行了表征。样品A在晶圆中心(实线)和中半径(虚线)的锗浓度剖面如图3所示。

TOF-SIMS分析(图3-(a))显示,晶圆中心的锗含量达到约85%,接近目标值。然而,沿径向向中半径方向观察到显著的横向变化,锗含量下降至约75%,导致总成分变化接近10个百分点。在晶圆中心和中半径之间的距离(约7.5厘米)上,这对应于大约1.3%/厘米的径向锗成分梯度,当在整个晶圆直径上进行归一化时,平均梯度约为0.3%/厘米。这些横向成分梯度的放大,已经在初始外延SiGe层中存在,在锗凝结过程中进一步放大,与之前的报告一致[37],并突出了在300毫米晶圆尺度上实现横向均匀的高锗含量SGOI层的关键挑战[32]。

EDX测量证实了这些发现,显示晶圆中心和中半径位置的锗含量值相似(图3-(c)),反映了相同的横向锗成分梯度。

值得注意的是,EDX显示锗的面外分布均匀,未见锗在氧化界面处积聚或堆积的证据。这确认了在减少氧分压条件下进行的热凝结工艺促进了SiGe和SOI层内锗的充分混合,确保了薄膜中锗深度分布的均匀性[36]。

图3:(a)TOF-SIMS分析,描绘了样品A在晶圆中心(实线)和中半径(虚线)的锗浓度剖面;(b)在样品A的晶圆中心(实线)和中半径(虚线)获取的拉曼光谱;(c)样品A晶圆中心的EDX线扫描深度剖面(绿色线)。

对于样品A,拉曼光谱(图3-(b))显示SiGe薄膜中不存在Si-Si模式(约500 cm⁻¹ [46]),表明没有残余的纯硅。光谱中Ge-Ge峰相对于Si-Ge峰强烈,确认锗含量超过50%,与TOF-SIMS和EDX结果一致。表2总结了结果,并将拉曼光谱获得的锗含量与TOF-SIMS分析和EDX数据进行了比较。

表2:通过TOF-SIMS、EDX和拉曼光谱确定的锗含量。残余应变是通过拉曼光谱推断的;(SSD代表固态脱膜)。

表2中的数据表明,TOF-SIMS、EDX和拉曼光谱在样品A中的锗含量结果一致。表中报告的完全应变层的理论应变值是通过拉曼光谱获得的锗浓度计算得出的。具体而言,首先通过拉曼光谱使用Si-Ge和Ge-Ge模式的强度比来确定锗含量,如前所述。然后,使用从拉曼光谱获得的锗浓度来计算假设完全应变的SiGe层的理论晶格不匹配应变。

测量的残余应变值表明部分压缩应变,晶圆中心为-0.68%,中半径为-0.88%。这些测量值相较于理论完全应变值(分别为-3.3%和-2.9%)显示出部分释放。中心测量到的较低残余应变与观察到的较高锗含量相一致。这一趋势与文献中报告的钟形曲线一致[28–30,36,47–49],表明随着锗的富集,应变释放增加。测量到的释放可能受到BOX中的粘性流动以及当SGOI中的锗浓度超过硅时,SGOI/BOX界面的滑移行为的帮助,因为锗-O键较弱。然而,我们注意到,尽管拉曼光谱表明样品A在晶圆中心的锗含量较低,样品B在晶圆中半径处的实验应变值大于样品A在中心处的应变值。这个差异的原因尚不完全清楚,但我们认为它可能是由于样品B中存在固态脱膜(SSD)特征,这可能在局部影响测量的准确性,导致计算出的应变和锗浓度有所变化。

为了验证SGOI层中应变释放的来源,在去除凝结氧化物后,通过AFM检查了样品的表面形貌。尽管[32]中报告的结果在锗含量超过28%时,富锗SGOI层显示出明显的交叉哈希表面图案,但我们的样品即使在约85%的较高锗浓度下,也未显示出这样的交叉哈希形貌(通过SEM和AFM)。AFM图像上测得的低RMS表面粗糙度(约0.2纳米)表明,我们的样品中的应变释放并非主要通过线程位错形成,而更可能是通过物质的缓慢重新分布实现的。

这一改进主要归因于优化的热凝结工艺,该工艺在低氧分压的稀释氧气气氛中进行,且随着锗分数的增加,氧化温度逐渐降低。这样的条件促进了更强的锗相互扩散和更平滑的成分剖面,从而抑制了缺陷的生成,并有利于通过物质重新分布实现渐进的应变释放机制。

初始SiGe层(约20纳米)具有较低的锗含量(约17%),预计也会减少塑性应变释放的驱动力。这种方法与[37,50]的研究结果一致,后者表明,较薄的初始层会导致较低的缺陷密度。这些因素的结合避免了导致交叉哈希图案形成的急剧塑性释放。

图4:(a)去除凝结氧化物后的SGOI层10x10 µm² AFM表面扫描;(b-c)85%锗SGOI层的横截面TEM图像,低倍放大(b)和高分辨率(c),显示出优异的晶体质量。

补充的横截面高分辨率透射电子显微镜(TEM)分析(图4-(b, c))确认了约5纳米厚的连续单晶SGOI薄膜,并且晶圆中心具有平滑的界面。在中半径位置(未显示),该薄膜仍保持单晶,并具有平滑的SGOI/SiO₂界面。在视野范围内未观察到平面缺陷,如堆垛故障、错配位错、微双晶或60°完美位错。因此,埋氧层(BOX)中的粘性流动和SGOI/BOX界面处的滑移行为,可能是由于锗-O键较弱,是该层应变释放的主要来源。然而,在TEM分析过程中,观察到SGOI厚度在暴露于电子束时出现局部变化,表现为层的起伏(图4-(b, c))。这些起伏之前已经在[51]中报告,并归因于SGOI/BOX双层的滑移行为,这可能有助于应变释放机制。

为了研究凝结技术的极限,样品B被设计用于生成纯锗层。凝结后,样品的性质因所考虑的区域而异。在中半径位置,SGOI薄膜保持均匀且连续,TOF-SIMS测量(图5-(d))显示锗浓度约为82%,比样品A在相同位置的锗浓度增加了约7个百分点(见表2)。该位置的EDX分析与TOF-SIMS数据相符,显示出明确定义的锗剖面,因此确认了该区域相比样品A成功富集。通过拉曼光谱测得的残余压缩应变为-0.92%(见图5-(f))。

相反,在晶圆中心,光学显微镜图像(图5-(a))显示出粗糙且不连续的表面,表明存在固态脱膜现象,这通常在Si和SiGe外延层在SiO₂上的情况下观察到[52–54]。这一现象的特征是连续薄膜破裂成离散的岛状结构。该过程发生在材料的熔点以下,通常是由表面和界面原子的扩散引起的,发生在固态中。这种重排减少了系统的总自由能。这种不稳定性与薄膜厚度呈反比,尤其在高锗含量的情况下表现得更加明显。

图5-(b)中的µ-拉曼映射显示Ge-Ge模式(红色),突出了不均匀的锗分布。图5-(c)中的µ-拉曼光谱确认在某些区域(位置1)存在纯锗,而在其他区域(位置2)存在纯硅,展示了薄膜的破裂。在这些条件下,TOF-SIMS(图5-(d))给出了这些区域的平均成分,因为薄膜是不连续的。拉曼光谱(图5-(e))进一步支持了在中心形成纯锗的现象,显示只有Ge-Ge模式。由于脱膜层的非连续性,无法可靠地测量残余应变。我们认为,晶圆中心的脱膜不稳定性是由高锗浓度(>85%)、残余应变、薄膜厚度减小(<5纳米)以及氧化过程中的高温(900°C)共同作用所引起的。

图5:(a)光学图像,突出显示样品B中心的锗脱膜;(b)µ-拉曼映射,选定区域(图(a)中的虚线框)揭示不均匀的锗分布;(c)在两个位置(1和2)的µ-拉曼光谱,位置1为纯锗,位置2为纯硅;(d)TOF-SIMS分析,描绘了中心(实线)和中半径(虚线)的平均锗含量;(e)在晶圆中心(实线)和中半径(虚线)获得的拉曼光谱。

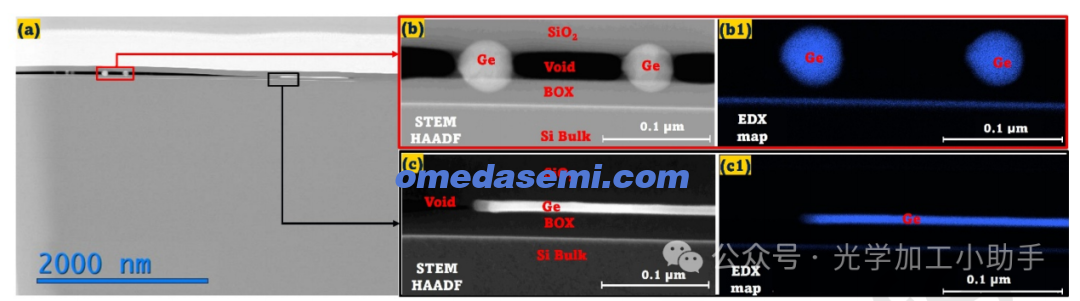

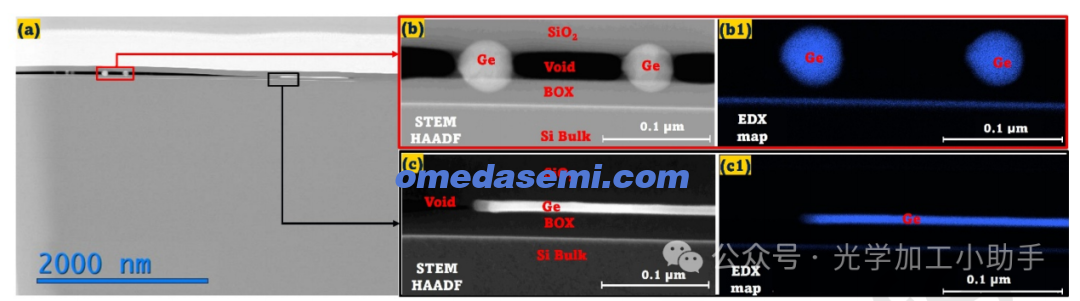

高角环形暗场(HAADF)TEM和STEM-EDX分析确认了晶圆中心的脱膜单晶锗岛(图6-(b))和不连续薄膜(图6-(c)),且没有位错。补充图3对应于区域(b)和(c)的EDX图,显示锗结构的增厚。脱膜驱动了纯锗纳米晶体的形成,这些纳米晶体的大小超过了初始富锗SGOI层,因为它们是由锗的聚集形成的,呈现近乎球形的点状结构。这种形态反映了锗在SiO₂基质内向其平衡形状演变的自然路径。纳米晶体的大小可以通过线扫描锗深度剖面评估,约为52纳米。结构之间的空隙均为TEM薄片准备过程中产生的。元素映射(图6-(b1, c1))揭示,脱膜过程还导致锗原子通过BOX扩散,并在BOX/硅基板界面形成新的SiGe层。

4. 结论

本研究展示了使用优化的高温锗凝结工艺,在300毫米(12英寸)晶圆上大规模制备薄且无缺陷的SiGe绝缘体(SGOI)薄膜,锗含量高达85%。与之前的研究不同,我们的方法解决了在工业相关晶圆尺寸下的关键挑战,推动了锗富集SGOI层在CMOS应用中的实际集成。高分辨率TEM观察确认了连续单晶薄膜的形成,具有原子级完美的晶格结构,并且在分析区域内没有检测到位错。

本研究的一个关键发现是确定约85%的锗含量是生产连续高质量SGOI薄膜的实际上限。在这一阈值之外,发生固态脱膜,导致单晶锗岛的形成和不连续的GOI薄膜,这代表了一个根本性的限制,与通常报道的位错介导的应变释放机制不同。

为了克服这一限制,我们提出了进一步的工艺优化,包括在高锗含量下降低氧化温度,并探索后续图案化的三维凝结方法。这些策略可能为实现纯锗层同时保持薄膜完整性提供有前景的路径。

总体而言,我们在12英寸SOI晶圆上获得的结果不仅加深了对锗富集SGOI薄膜中应变释放和材料稳定性的理解,而且为将其大规模集成到下一代CMOS器件中铺平了道路,在这些器件中,高锗含量层对提升载流子迁移率和实现高性能晶体管架构至关重要。