摘要

随着人工智能(AI)和机器学习(ML)应用的快速发展,晶圆级光学输入/输出(I/O)正变得越来越有吸引力,用于未来晶圆级多处理单元(多XPU)计算集群中大规模、高效的数据互联,具备无与伦比的数据带宽、能效和低延迟。在本文中,我们展示了一种300毫米尺寸的晶圆光刻拼接低压化学气相沉积(LPCVD)硅氮化物(SiN)波导技术,并演示了一个跨越20个光刻版的约56厘米长波导,具有0.13~0.15 dB/cm的传播损耗(在1310 nm波长下),以及<0.001~0.002 dB的SiN波导拼接损耗,这主要是由于<5 nm高精度光刻版偏移造成的。这些低损耗拼接的SiN波导的优异特性,有可能显著提升未来光学互连的晶圆级多芯片计算系统。

#2:a向 bto外延片

2寸 外延 a-向 bto(300nm或者500nm,或者定制)-sto 8nm(可定制)- 2um Sio2(可定制) -Si(可定制)

#3:C向 bto外延片

2寸 外延 c-向 bto(150nm或者300nm,或者定制)-sto 8nm(可定制)- 2um Sio2(可定制) -Si(可定制)

#离子注入铒代工

#6寸DUV步进式光刻代工,最小线宽180nm,超高性价比,可以只曝光

#快速氮化硅硅光铌酸锂流片 #高性价比 #低成本

#提供8寸 8umSiO2热氧片,6寸15um热氧片 10um热氧片 8寸10um热氧片

SOI晶圆:--220nm薄膜/ 3um厚膜-3umSIO2-675umALOOI晶圆;--氧化铝薄膜晶圆,键合工艺和镀膜工艺

TAOOI晶圆--氧化钽薄膜晶圆,镀膜工艺

SINOI晶圆--超低损耗氮化硅薄膜晶圆,160nm-180nm-200nm-300nm-350nm-400nm-800nm

SICOI晶圆;新型量子光学平台500nm-700nm-1um

8寸LTOI晶圆批量供应;铌酸锂的有力的竞争对手,薄膜钽酸锂晶300600

8寸LNOI晶圆;8寸LNOI助力更大规模薄膜铌酸锂产品量产

LN/LT-SOI/Si/SIN W2W&D2W异质集成

流片: 6寸 氮化硅 铌酸锂 硅光 超高性价比流片, 1个BLOCK的价格买一整片晶圆

划重点--全国产-超高性价比-6 寸硅光-氮化硅-铌酸锂流片白皮书

我们为客户提供晶圆(硅晶圆,玻璃晶圆,SOI晶圆,GaAs,蓝宝石,碳化硅(导电,非绝缘),Ga2O3,金刚石,GaN(外延片/衬底)),镀膜(PVD,cvd,Ald,PLD)和材料(Au Cu Ag Pt Al Cr Ti Ni Sio2 Tio2 Ti3O5,Ta2O5,ZrO2,TiN,ALN,ZnO,HfO2。。更多材料),键合(石英石英键合,蓝宝石蓝宝石键合)光刻,高精度掩模版,外延,掺杂,电子束光刻等产品及加工服务(请找小编领取我们晶圆标品库存列表,为您的科学实验加速。

请联系小编免费获取原文

文章名:Low-Loss, Multi-Reticle-Stitched SiN Waveguides for 300 mm Wafer-Level Optical Interconnects

作者:Pengfei Xu * , Chiara Marchese, Guy Lepage, Negin Golshani, Ruben Van Eenaeme, Andrea Mingardi,Joost Van Ongeval, Rafal Magdziak, Luc Halipre, Darko Trivkovic, Peter Verheyen, Maumita Chakrabarti ,Dimitrios Velenis , Andy Miller, Filippo Ferraro, Yoojin Ban and Joris Van Campenhout引言

人工智能(AI)和机器学习(ML)日益普及,推动了对高带宽、低延迟和能效高的计算芯片(如CPU、GPU、XPU等)与高带宽内存(HBM)之间的互连需求,特别是在AI/ML计算集群中【1–4】。晶圆级光学互连(WL-OIs)是一项新兴技术,旨在将多个XPU或HBM互连在单一的300毫米晶圆上【5,6】。与光纤耦合的链路相比,这项技术在芯片边缘带宽密度、能效和延迟方面具有优越性,同时提供比晶圆上的铜互连更长的传输距离【7,8】。鉴于在设想中的WL-OIs计算集群(见图1)中,

图1. 设想中的光学互连计算系统,位于300毫米尺寸的光学互连晶圆上。与光纤阵列或铜线不同,使用高密度、低损耗的光刻拼接SiN波导(绿色),实现极高的边缘带宽密度和高能效的晶圆级光学输入/输出。CPU:中央处理单元。GPU:图形处理单元。HBM:高带宽内存。Tx:光学发射器。Rx:光学接收器。TSV:硅穿透通孔。

互连距离预计将达到数十厘米,因此亟需开发低损耗、高约束、低串扰和高密度的波导阵列,这些波导阵列能够跨越整个300毫米晶圆,超越当前边缘带宽密度的限制。

与硅基(折射率 n ~ 3.5)波导相比【9】,硅光刻拼接波导提供了更高的光学约束,但也伴随着更高的成本、更大的传播损耗和更强的光刻偏移敏感性。由于其适中的折射率(折射率 n ~ 2.0),SiN光刻拼接波导因其较低的侧壁散射引起的传播损耗和较低的模式失配引起的拼接损耗而被更为偏好【10,11】。SiN还被认为在硅光子集成中更为便捷。因此,在本文中,我们展示了一种300毫米晶圆级低压化学气相沉积(LPCVD)SiN波导,采用高精度光刻拼接技术。我们演示了跨晶圆拼接(最多20个光刻版)波导,长度可达56厘米,波导传播损耗为0.12~0.15 dB/cm(在1310 nm波长下)。

2. 高精度光刻拼接的前景

光刻拼接技术对于大多数200毫米平台上的硅光子应用已经成熟并商业化,通常具有100~200 nm的光刻偏移。然而,对于未来带宽需求巨大的晶圆级光学I/O,约10 nm或更高精度的光刻拼接对于针对> Tbit/s/mm芯片边缘带宽密度的带宽密集型晶圆级光学I/O至关重要。下表1详细讨论了未来晶圆级光学I/O对~10 nm级高精度的需求。

表1. 高精度光刻拼接的前景

3. 多光刻版拼接SiN波导

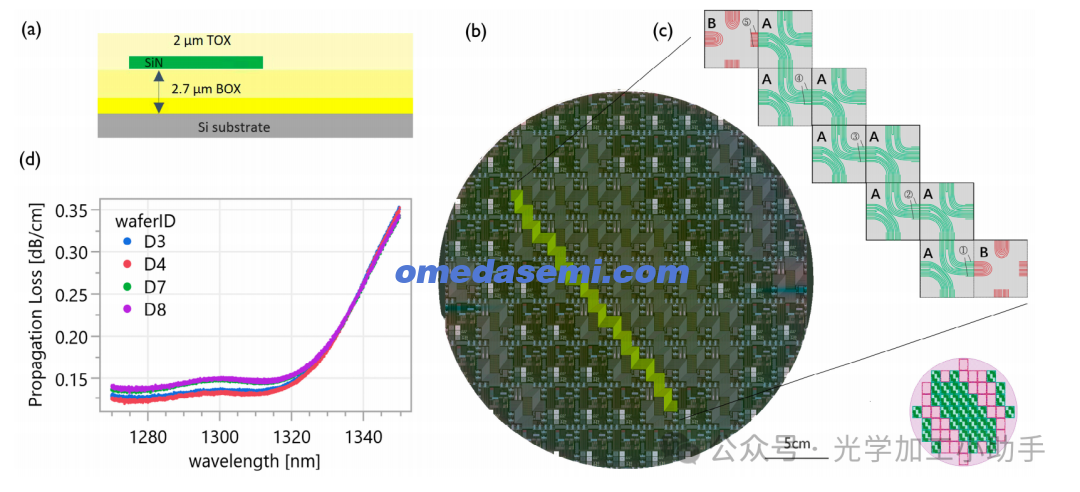

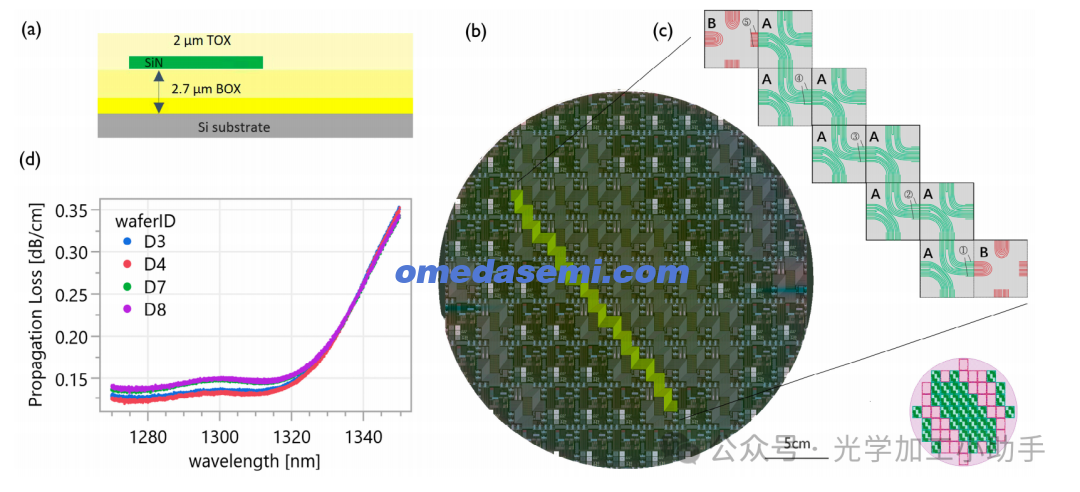

为了实验性地展示多光刻版拼接波导,测试用晶圆(共八个晶圆用于统计,其中晶圆D1~D4为300 nm厚SiN,晶圆D5~D8为400 nm厚SiN)在imec的300毫米CMOS试点线上实施【12】。

图2. 多光刻版拼接SiN波导。

(a) 测试用晶圆(共8个晶圆用于统计,D1~D4晶圆为300 nm厚SiN,D5~D8晶圆为400 nm厚SiN)用于展示光刻拼接SiN波导。

(b) 采用专用的全晶圆曝光来形成多光刻版拼接回路波导(黄色部分突出显示),通过安排使用掩模A和掩模B的光刻作业。

(c) 回路波导束的设计原理。

(d) 通过削减技术提取的多光刻版拼接波导传播损耗,在1310 nm波长下为0.13~0.15 dB/cm。

测试用晶圆(见图2a)仅有一层刻蚀的SiN层。300毫米晶圆加工从2.7 µm厚的埋氧化物(BOX)沉积开始。接下来,沉积300 nm或400 nm厚的LPCVD SiN层。300 nm和400 nm厚度都常用于具有高光学约束的硅光子集成。预计300 nm厚的SiN波导表现出较少的侧壁散射和较低的传播损耗,而400 nm厚的SiN波导具有更高的有效折射率,允许更大的弯曲半径和更密集的波导阵列【13】。在光刻和SiN图案化后,沉积氧化物顶面包覆层并随后进行平面化,目标是在SiN上得到超过2 µm厚的顶氧化物(TOX)。LPCVD SiN层通过先进的193 nm浸没式光刻进行图案化,利用高对准精度进行光刻拼接。使用两种不同的光刻版(如图2c所示),每个覆盖一个完整的26 × 33 mm² SiN掩模,用于形成晶圆级光刻拼接波导。每个掩模通过专用的光刻作业进行曝光,最终形成图2b所示的完整晶圆曝光图。

几条跨晶圆回路波导(最长可达56厘米)通过将长波导束图案化在第一个SiN掩模(掩模A)上,并将波导弯曲/终止(如光栅耦合器和波导U型转弯)图案化在第二个SiN掩模(掩模B)上进行。由于输入和输出光栅耦合器端口之间的晶圆级大距离,在晶圆探针站测量跨晶圆波导损耗具有挑战性。为了简化光学测量过程,采用了回路波导。多光刻版拼接回路波导的设计原理如图2c所示。通过在图2c中的不同晶圆位置(1⃝~ 5⃝)处的不同晶圆上探测光纤,可以测量8.3厘米、20.2厘米、32.1厘米、44.1厘米和56.0厘米多光刻版拼接回路波导的相应光学损耗。通过使用削减技术提取拼接波导的传播损耗(图2d显示了光学O波段的光损失读取)。提取的SiN波导传播损耗为0.13~0.15 dB/cm(在1310 nm波长下)。此外,由于沉积的SiN中存在杂质和化学键吸收(Si–H和N–H),传播损耗在较长的1350 nm波长下略有增加【14–16】。尽管传播损耗略高于当前的先进水平(即SiN波导的<0.1 dB/cm),但本研究中使用的LPCVD SiN波导具有集成友好、成本效益高且商业可得的优点,无需复杂的制造步骤,如极高温退火。

4. SiN波导拼接损耗分析

在步进光刻中,光刻偏移通常在10 nm或100 nm级别上是技术上不可避免的,突变的拼接接口和光学模式失配会导致额外的波导拼接损耗和不必要的界面反射。首先,使用高分辨率扫描电子显微镜(SEM)检查拼接SiN波导的刻蚀接口。SEM图像(见图3)显示,

图3. 拼接SiN波导光刻版间接口的SEM检查。(拼接宽度可选为0.71、1.8和2.5 µm,预期拼接损耗< 0.01 dB;见附录A 图A1)。

在光刻版间的接口处,界面没有缺陷且视觉上光滑。然后,采用专用的双重曝光重叠(OVL)结构(检查方法见图4)分析光刻偏移,

图4. 为了表征光刻版间的光刻偏移,每个光刻版包含6个OVL检查结构,用于测量x和y方向的光刻偏移。光刻版偏移的读取值(4个晶圆 × 53个光刻版 × 6个OVL检查标记)均小于5 nm。

使用SEM图像处理和检查功能。对四个晶圆进行了全面的OVL测量(每个晶圆有53个光刻版,每个光刻版在掩模划线的不同位置有六个OVL结构),测得的x或y方向的光刻偏移小于5 nm。

由于光刻偏移已经在5 nm以下进行了检查,为了分析SiN波导拼接损耗,提出了图5a中的加减环谐振器对。环谐振器因其占用非常小的芯片面积且不受SiN光栅耦合器损耗变化的影响,因而被广泛用于监测SiN损耗。

图5. 使用紧凑型环形谐振器提取SiN波导拼接损耗(在垂直拼接情况下,水平拼接类似)。

(a) 加减环形谐振器对,具有相同的参考环和拼接环谐振器。拼接环具有12个额外的拼接,用于精确测量波导拼接损耗。

(b) 加减环形谐振器对的示意图。环的往返长度约为6 mm,弯曲半径为50 µm,总线到环的距离为1.6 µm。环形谐振器设计为欠耦合状态,因此加减环的内部损耗将与环的固有损耗接近;见附录A 图A2。(虚线表示光刻版划线)。

图5a展示了加减环谐振器对的设计布局,包括一个参考环谐振器(参考环,绿色)和一个拼接环谐振器(拼接环,部分为红色)。图5b为示意图,展示了设计参数,如输入、通过、输出端口、自耦合系数r1、r2、总线到环的距离和SiN波导宽度,所有参数均在图中标注。所有环谐振器长约6 mm,波导弯曲半径为50 µm。更重要的是,拼接环有12个额外的光刻版间波导拼接,用于累积和放大弱拼接损耗信号。然后,通过比较拼接环和参考环之间的内部损耗差异,可以确定平均波导拼接损耗。

图6. 加减环形谐振器对的环内损耗(测量了8个晶圆 × 6个晶片)。红色和绿色标记分别表示拼接环和参考环的内部损耗。损耗差异来源于12个额外的波导拼接。由于50 µm半径的尖锐波导弯曲,300 nm厚的环形谐振器测得具有较高的内部损耗。

图6显示了在八个晶圆上,分别对六个随机测量的晶片进行测试后,拼接环和参考环的内部损耗计算结果。如预期的那样,拼接环的计算内部损耗通常高于参考环(即,红色标记的值通常高于绿色标记,少数例外情况可归因于测量偏差)。拼接环中增加的损耗归因于12个额外的波导拼接。接下来,SiN波导的平均拼接损耗可以通过计算得出。

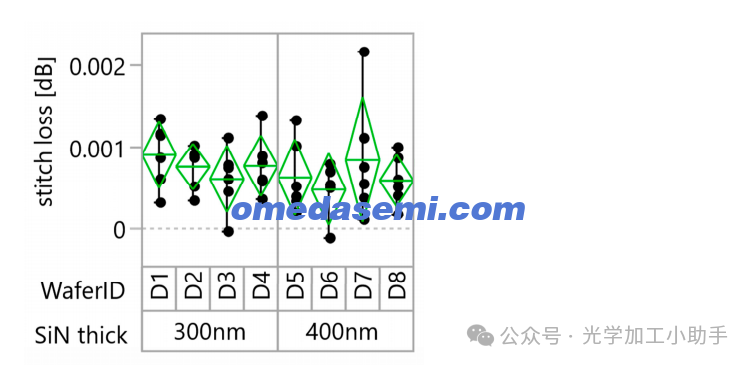

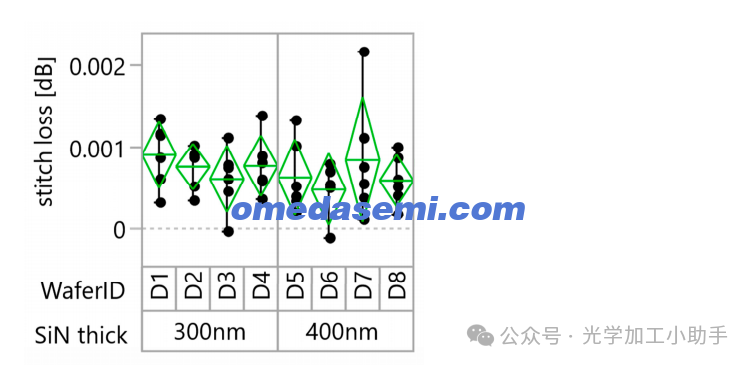

提取的拼接损耗如图7所示。

图7. SiN波导拼接损耗分析,结果为<0.001~0.002 dB, comparable to 约50 µm SiN波导段的传播损耗。(8个晶圆 × 6个晶片统计;钻石图展示了默认95%置信区间内的平均拼接损耗范围)。

由于光刻版偏移小于5 nm,计算得出的拼接损耗为<0.001~0.002 dB,这与约50 µm SiN波导段的传播损耗相当。这一结果对于未来晶圆级光学互连的开发和应用具有良好的前景。

5. 更大20 nm光刻偏移下的拼接损耗

为了验证图7中的0.001~0.002 dB拼接损耗,20 nm y方向的光刻偏移被施加到D4和D8晶圆上,通过轻微偏移整个掩模B的光刻作业。这是为了预期在特定位置(图8a中的紫色接口)看到更高的波导拼接损耗。

图8. 由于施加20 nm光刻偏移导致的波导拼接损耗增加。

(a) 通过轻微偏移整个掩模B光刻作业,在掩模A到掩模B的拼接接口处的特定位置(标记为紫色)施加了20 nm的y偏移。紫色箭头表示施加的光刻偏移方向。

(b) 在紫色接口处通过扫描电子显微镜(SEM)检查得到20 ± 4 nm的y偏移。

(c) 红色和绿色标记分别表示拼接环和参考环的内部损耗。D4和D8晶圆在紫色接口处的拼接环内部损耗明显高于D3和D7参考晶圆。

(d) 由于施加的20 nm偏移,SiN波导拼接损耗增加至0.002~0.005 dB。同时,2.5 µm宽的渐变上升拼接比1.8 µm宽的渐变上升拼接的光学损耗低0.001~0.002 dB。(钻石图展示了平均拼接损耗,并具有默认的95%置信区间)。

重叠(OVL)检查揭示,在紫色接口处,光刻版y偏移增加至20 ± 4 nm(均值±3σ)。然后,测量了D4和D8晶圆中拼接环和参考环的内部损耗。为进行对比,还对D3和D7晶圆(没有施加20 nm y偏移)进行了测量。每个晶圆在紫色接口处测量了超过10个随机晶片。加减环谐振器对的环内损耗结果如图8c所示。红色标记为拼接环的内部损耗,绿色标记为参考环的内部损耗,黑色条表示拼接环与参考环之间的内部损耗差异。显然,D4和D8晶圆的拼接环内部损耗高于D3和D7晶圆。然后,可以计算出图8d中的增加的SiN波导拼接损耗;由于更差的20 nm y偏移,拼接损耗增加至0.002~0.005 dB。值得注意的是,2.5 µm宽的渐变上升拼接与1.8 µm宽的渐变上升拼接相比,显示出约0.001 dB较低的损耗。这表明,在光刻偏移较大的情况下,较宽的拼接宽度效果更好。

6. 结论

本文展示了300毫米晶圆光刻拼接SiN波导。通过安排专用的晶圆曝光,展示了最长达56厘米的多光刻拼接回路波导,跨越20个光刻版接口,传播损耗为0.12~0.15 dB/cm(在1310 nm波长下)。尽管SiN波导的传播损耗略高于当前的先进研究水平,但这些跨晶圆波导表现出非常小的光刻版间偏移(<5 nm)和可忽略的拼接损耗(<0.001~0.002 dB)。通过利用已展示的光刻拼接低损耗SiN波导,未来的晶圆级多XPU计算系统可以实现无与伦比的互连带宽、能效和延迟,这对于推动晶圆级光学互连技术在AI/ML计算集群中的发展超越当前技术具有重要意义。

表A1. LPCVD SiN技术总结

图A1. SiN波导拼接结构。

(a) 光刻版间接口处拼接SiN波导的示意图。显示了关键参数,如光刻重叠(假设为10~50 nm,以便对抗10纳米级光刻偏移,精确图案化波导)、光刻偏移(由于位移通常为10纳米级偏移)和拼接宽度(SiN波导通过使用绝热渐变器可选择性地从平面0.71 µm宽的SiN波导逐渐加宽至1.8 µm或2.5 µm宽)。

(b) 在最坏情况下20 nm光刻偏移(y方向)的模拟光场。

(c) 平面拼接和1.8 µm宽渐变上升拼接的模拟插入损耗和回波损耗。

在本文中,提出了平面拼接和渐变上升拼接(见图A1)来演示光刻拼接波导并研究波导拼接损耗。作为参考设计,平面拼接结构简单,风险较低,SiN波导拼接采用单模波导宽度(通常为710 nm),没有波导渐变或多模部分。因此,由于意外的制造缺陷,不存在高阶模激发损耗的风险。另一方面,渐变上升拼接是一种有前景的替代方案,通过将波导宽度逐渐增加,从而减小光刻版间接口的模式失配。

图A1为3D-FDTD模拟,其中考虑了最坏情况的20 nm光刻偏移(在y方向),图A1b显示了模拟的光场(电磁波的电场y分量),图A1c显示了模拟的插入损耗和回波损耗,即来自光刻版间拼接接口的波导反射损耗。对于平面拼接,接口的波导拼接损耗小于0.01 dB,回波损耗大于50 dB,而对于渐变上升拼接(例如,SiN波导逐渐加宽至1.8 µm的多模部分),模拟的接口预计具有更好的光学损耗(约0.006 dB插入损耗和大于60 dB回波损耗),因为增大的模式场直径和较少的模式失配。

图A2. 加减环形谐振器的典型光谱,光谱范围为10 nm,通过该光谱可以数值分析环形谐振器的平均内部损耗。共振波长的下陷处已被标记并进行分析。

表A2. 环形内部损耗分析与讨论(拼接环 vs 参考环)

附录A.3. 拼接损耗提取方法

环形谐振器被广泛使用来监测SiN损耗,因为它们占用的芯片面积非常小。这些环形谐振器通常处于欠耦合状态,即总线到环的距离相对较大,以确保加减环的内部损耗接近环的固有损耗(见图5)。在这项工作中,使用了1.6 µm的总线到环距离的拼接环和参考环谐振器来数值分析SiN波导的拼接损耗。尽管环形谐振器的设计参数——例如约6 mm的往返长度、50 µm的弯曲半径等——会影响测量的环内损耗,例如较长的往返传播、较尖锐的波导弯曲和较小的总线到环的距离会导致更高的内部损耗读取。然而,拼接环和参考环具有相同的布局;拼接损耗是拼接环和参考环之间的内部损耗差异,这完全与加减环的设计参数无关(详细信息见表A2)。

加减环谐振器的典型测量光谱(输入到通过和输入到输出)如图A1所示。在本研究中,使用可调激光源和1皮米分辨率的仪器测量了跨越10 nm的光谱(以1310 nm光学O波段为中心)。环形谐振器的平均内部损耗是从该10 nm范围内的所有共振波长计算得出的,因为该方法在1皮米光谱分辨率限制下提供了更准确的环内损耗结果。通过这些光谱,可以提取自由光谱范围(FSR)、半高宽(FWHM)、最大功率百分比(Tmax,输入到输出传输的最大功率百分比)和最小功率百分比(Rmin,输入到通过传输的最小功率百分比)。然后,环形谐振器的往返内部损耗可以通过以下公式数值计算【17,18】:

其中,a是环形谐振器的往返内部损耗系数。参数r1和r2是总线到环耦合的自耦合系数。