摘要——在本研究中,通过对不同无源元件(即CPW和TFMS线路)的微小信号测量,评估了标准和各种高电阻(HR)基板的射频性能,包括PN钝化基板,分别在常温和低温下的表现。提取了传输线的有效电阻率和传播损耗。结果表明,基板损耗的退化以及低温下金属损耗的改善得到了体现。最后,PN界面钝化方案首次在低温下进行评估,作者最初的研究表明,与没有任何钝化方案的HR基板相比,钝化后有效电阻率至少提高了7倍。#全国产SOI晶圆定制加工 #468寸50nm-15um热氧片

库存片:

220nmSI高阻-3umSIO2-675umSI 6寸8寸 用于薄硅硅光

3000nmSI高阻-3umSIO2-675umSI 6寸8寸 用于厚硅硅光

#尺寸4-8寸

#最小起订量1片

#热氧层厚度范围50nm-15um

#膜厚精度最高精度+-5nm

#厚膜SOI-减薄抛光工艺600nm到微米级,加离子束精修,超级高精度膜厚均匀性

#CavitySOI-带空腔SOI晶圆,光刻显影刻蚀键合制作SOI一条龙

#FDSOI -最薄顶层10nm,特殊工艺精修,粗糙度小,膜厚精度高

普通超薄:SMARTCUT+离子束精修

超级超薄:EPI+SMARTCUT+离子束精修

#超平硅片-TTV500nm

我们为客户提供晶圆(硅晶圆,玻璃晶圆,SOI晶圆,GaAs,蓝宝石,碳化硅(导电,非绝缘),Ga2O3,金刚石,GaN(外延片/衬底)),镀膜(PVD,cvd,Ald,PLD)和材料(Au Cu Ag Pt Al Cr Ti Ni Sio2 Tio2 Ti3O5,Ta2O5,ZrO2,TiN,ALN,ZnO,HfO2。。更多材料),键合(石英石英键合,蓝宝石蓝宝石键合)光刻,高精度掩模版,外延,掺杂,6寸DUVKRF电子束光刻等产品及加工服务(请找小编领取我们晶圆标品库存列表,为您的科学实验加速。

请联系小编免费获取原文

文章名:Various RF Substrate Solutions for 22 nm FD-SOI Technology Targeting Cryogenic Applications作者:Martin Vanbrabant, Martin Rack, Dimitri Lederer, Valeriya Kilchytska, Jean-Pierre Raskin单位:Université catholique de Louvain, BelgiumI. 引言

如今,硅CMOS技术及其先进工艺节点为射频(RF)和毫米波(mm-wave)应用提供了竞争力的性能。近期的CMOS技术,如全耗尽硅绝缘体(FD-SOI),通常提供具有300-400 GHz范围内的截止频率(ft)和最大振荡频率(fmax)的有源器件【1】。此外,丰富的后端工艺(BEOL)选项【2】以及基板的电磁性能在毫米波无源元件(即电感器和电容器)及互连的品质因数方面发挥了重要作用。因此,硅基板如果电阻率较低,可能会导致显著的损耗、耦合和非线性【3】。

从标准电阻率基板(标称电阻率ρnom ≈ 10 Ωcm)过渡到高电阻(HR)基板(ρnom > 1 kΩcm)有助于缓解这些效应,尽管这一改善会受到寄生表面导电(PSC)效应的阻碍【4】。该效应源于在Si/SiO2界面形成薄的高导电层,该层由正电荷固定的氧化物电荷吸引自由电子【4】【5】,从而导致由硅基板上的共面电路感知的有效电阻率ρeff下降【6】。

为了应对PSC层,已经开发了几种界面钝化解决方案。在部分耗尽硅绝缘体(PD-SOI)技术中,Trap-Rich(TR)层是一个广为人知的解决方案,通过在埋氧化物下方引入一层薄的多晶硅,使界面变得具备电阻性【5】。在FD-SOI技术中,一个兼容的钝化解决方案是PN钝化技术,依赖于交替区域的P型和N型掺杂物的植入。以前的导电界面现在变成了一系列由低电阻(N型和P型掺杂)和高电阻(耗尽结)区域组合而成的结构,从而提高了有效电阻率【7】【8】。特别地,CPW线路的基板引起的损耗和非线性得到了显著改善,同时射频电感器的品质因数也得到了显著提高【9】【10】。

如今,电子元件和系统的低温操作吸引了大量关注,主要是由空间【11】和量子应用【12】推动的。在这些极端条件下对有源和无源元件的表征对于低温下的电路设计至关重要【13】。在以往的工作中,研究了低温对HR基板上CPW线路【14】、在标准、HR和TR基板上制造的电感器【15】以及金属氧化物金属(MoM)电容器、变压器和共振器的影响【16】。

本文研究了低温对不同电阻率基板上传输线传播损耗的影响。我们在常温和液氮温度下对两种类型的CPW和一种TFMS测试结构进行了片上射频(RF)测量。PN界面钝化方案在液氮温度下的有效性是首次评估的(据作者所知)。

II. 制造的结构和测量设置

在GlobalFoundries的22FDX®技术的后端工艺上,我们设计并制造了几种传输线,这些传输线位于具有不同基板电阻率的晶圆上。

A. 线路几何结构

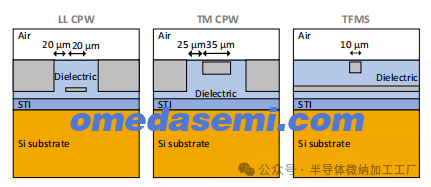

图1. 制造和表征的线路的示意横截面及其主要尺寸:LL 和 TM CPW 线路以及 TFMS 线路。

设计了两种类型的共面波导(CPW)线和一种TFMS线,旨在实现接近50 Ω的特性阻抗(Zc),如图1所示。每条线路的长度为760 µm,并配有专用的开放(Open)和通(Thru)结构。第一种CPW结构(LL CPW)由堆叠的下层(LL)金属层构成,信号线宽度(W)为20 µm,信号到地的间距(S)为20 µm。第二种CPW结构(TM CPW)由上层和更厚的金属(TM)层实现,信号线宽度(W)为35 µm,信号到地的间距(S)为25 µm。此外,还设计了一种TFMS线,信号线宽度为10 µm,采用与TM CPW相同的厚金属层,并且地面平面位于中等厚度的金属层堆叠中。

B. 基板变体

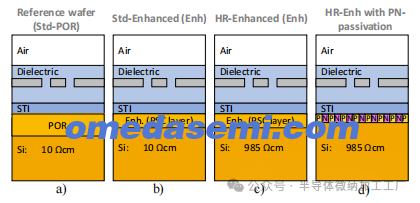

图2. 研究的基板变体的示意横截面:(a)Std-POR,(b)Std-Enh,(c)HR-Enh 和(d)HR-Enh 与 PN-钝化。

每种结构都在四个不同基板电阻率的晶圆上进行复制,如图2所示:(a) 参考工艺(POR)在标准电阻率(约10 Ωcm)晶圆上,标记为Std-POR,(b) 另一种标准电阻率(约10 Ωcm)晶圆,优化了较低导电性界面,标记为Std-Enh(PSC效应仍然存在),(c) 高电阻率(985 Ωcm)晶圆,优化了较低导电性界面,标记为HR-Enh,以及(d) 使用PN线界面钝化的相同HR-Enh基板。这些PN结用于通过阻碍信号线与接地线之间的E场路径,在它们之间形成多个高电阻的耗尽区域,从而增加CPW的阻抗。通过芯片上的高值电阻元件,它们还可以反向偏置,以扩大耗尽区域,进一步增加基板的界面阻抗。

C. 测量设置

使用一对接地-信号-接地(GSG)Picoprobe® 探针,通过 Keysight PNA N5291A 矢量网络分析仪(VNA)在 100 kHz 到 40 GHz 范围内测量不同传输线的 S 参数。测量在常温(295 K)和液氮温度(77 K)下进行,使用 LakeShore CPX 低温探针站。

III. RF 性能结果

传输线的测量首先通过每个温度下的线-反射-反射-匹配(LRRM)校准进行修正。从 S 参数数据中,提取了底层材料的有效电阻率 ρeff 和线路损耗 α【17】经过线-线去嵌入处理后。

A. LL CPW 线路

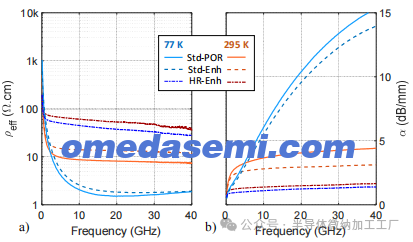

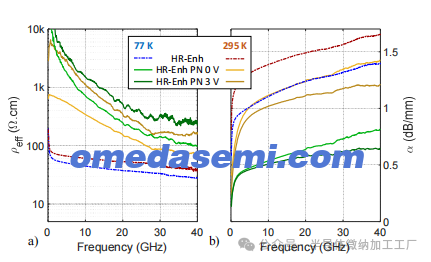

图3. 从不同基材(Std-POR、Std-Enh 和 HR-Enh)提取的 LL CPW 线路的有效电阻率 (a) 和传播损耗 (b),在 77 K 和 295 K 下的测量结果。

从不同基材上的 LL CPW 线路在 77 K 和 295 K 下获得的 RF 性能结果如图 3 所示。如预期的那样,在 295 K 下,标准电阻率基材的有效电阻率分别为 Std-POR 和 Std-Enh 在 20 GHz 时分别达到 ρeff(20 GHz) = 8 和 13 Ωcm。转向高电阻率基材(HR-Enh)时,ρeff(20 GHz) 提高到 53 Ωcm,远低于其标称电阻率值(985 Ωcm),因为它受到了 PSC 效应的影响。如图 3.b 所示,转移到 HR-Enh 后,线路损耗在 20 GHz 时减少了 2.5 dB/mm(Std-POR)和 1.5 dB/mm(Std-Enh)。

在 77 K 下,所有基材的有效电阻率相较于常温下的对应值都有所下降。这是由于低温下载流子迁移率的增加【18】。Std-POR 和 HR-Enh 基材的 ρeff(20 GHz) 分别从 295 K 时的 8 和 53 Ωcm 降到 1.5 和 37 Ωcm。有趣的是,在 77 K 下,标准电阻率基材的线路损耗 α(20 GHz) 增加了大约 6.5 dB/mm,而 HR-Enh 基材的线路损耗则减少了 0.3 dB/mm。其原因是,尽管所有基材的 ρeff 都下降(基材损耗),但金属损耗在 77 K 下较低。因此,在 HR-Enh 基材中,金属损耗的减少效果由于温度降低而优于较高的基材损耗,而标准电阻率基材则不同,因为它们的损耗主要由基材损耗主导,而非金属损耗。

图4. 在77 K和295 K下,提取自HR-Enh上的LL CPW线的有效电阻率(a)和传播损耗(b),分别为有无PN钝化的情况。

先前的研究【7】已经证明了PN界面钝化解决方案在室温下的有效性。在图4中可以看到,这种解决方案在77 K下仍然具有优势。实际上,当PN钝化存在且没有施加结偏置电压时,有效电阻率(在20 GHz下测量)在295 K时增加到150 Ωcm,在77 K时增加到250 Ωcm。当施加3 V反向PN偏置时,它扩大了PN结的耗尽区【19】,因此,ρeff(20 GHz)在295 K时进一步增加到350 Ωcm,在77 K时增加到510 Ωcm。传播损耗在VNP = 3 V时相应地改善,与没有钝化的HR-Enh基材相比,295 K时改善了0.39 dB/mm,77 K时改善了0.63 dB/mm。

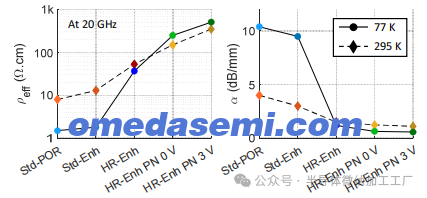

图5. 在77 K和295 K下,从不同基材上提取的LL CPW线路的有效电阻率ρeff(20 GHz)和传播损耗α(20 GHz)。

在图5中,可以看到PN钝化在低温下更为有效,因此ρeff更高(在77 K下从HR-Enh到HR-Enh PN 3V的改进为700%,而在295 K下为230%),与其他所有基材情况相反。这是因为随着温度降低,耗尽区变宽(因此它的作用类似于反向PN偏置)。

B. TM CPW 和 TFMS 线路

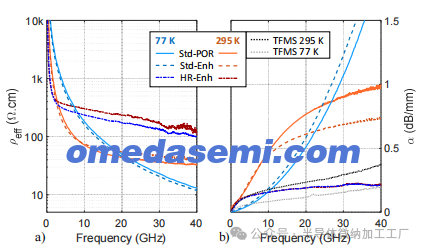

图6. 从不同基板(Std-POR、Std-Enh 和 HR-Enh)上的 TM CPW 线路提取的有效电阻率 (a) 和传播损耗 (b),在77 K 和295 K下的测量结果。为比较添加了TFMS线路的传播损耗。

在77 K和295 K下对不同基材上的TM CPW线路进行了类似的基准测试,如图6所示。除了TM CPW传播损耗外,还增加了TFMS传播损耗以供比较。

由于CPW线和基材之间的距离较大,TM CPW线路的有效电阻率相比LL CPW线路的值较大。在室温下,Std-POR/Enh基材的ρeff在20 GHz时分别为44 Ω·cm和55 Ω·cm,而HR-Enh基材为230 Ω·cm。在77 K时,所有基材的提取有效电阻率在~20 GHz以上都低于室温,类似于LL CPW线路。值得注意的是,尽管HR-Enh的ρeff在295 K时为230 Ω·cm,在77 K时降至170 Ω·cm,但在相同频率下的线路损耗保持不变(图6.b),金属和基材损耗的变化相互补偿。

如图6.b所示,TFMS线路在20 GHz下的α改善了0.11 dB/mm,由295 K变为77 K。这主要归因于金属损耗的改善,因为屏蔽地平面防止了任何基材损耗。

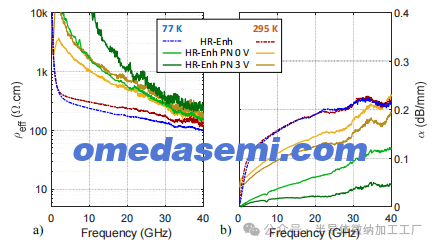

图7. 在77 K和295 K下,从HR-Enh基板上的TM CPW线路提取的有效电阻率(a)和传播损耗(b),分别为有无PN钝化的情况。

与LL CPW线类似,HR-Enh基板上的TM CPW线也从PN钝化解决方案中获得了极大的好处,如有效电阻率(图7.a)和传播损耗(图7.b)所示。

表1. 在77 K和295 K下,不同基板选项上CPW和TFMS线路的RF性能指标(FoMs @ 20 GHz)

所有研究的传输线在20 GHz下提取的RF指标汇总在表1中。

IV. 结论

本文评估了标准和高电阻基板在室温和低温条件下的射频性能,通过测量几种无源结构,如CPW和TFMS线路。在低温下,总传播损耗可能比室温下高或低,这取决于线路几何结构(特别是与基板的距离)以及主要的贡献是金属损耗还是基板损耗。事实上,如TFMS线路所示,金属损耗随着温度降低而减少,20 GHz时在α上测得了0.11 dB/mm的改善。

对于没有PN界面钝化的基板(Std-POR、Std-Enh和HR-Enh),在液氮温度下,观察到有效电阻率发生了退化。然而,与所有其他基板相比,HR-Enh PN基板在低温下更为高效,因为有效电阻率(在20 GHz下)相比未钝化的HR-Enh基板至少提高了7倍(PN 3 V)。由于PN耗尽结的宽度在低温下增加,PN钝化基板在低温下表现出更好的射频性能,特别是在强反向偏置条件下。总体而言,PN界面钝化解决方案提供了优秀的基板性能指标,并且在低温下仍然有效。