作者:Liang Zhang,∗,†,‡ Yanan Guo,∗,†,‡ Junxi Wang,†,‡ Jinmin Li,† and Jianchang Yan∗,†,‡ 单位:†Research and Development Center for Wide Bandgap Semiconductors, Institute of Semiconductors, Chinese Academy of Sciences, Beijing 100083, China ‡College of Materials Science and Opto-Electronic Technology, University of Chinese Academy of Sciences, Beijing 100049, China摘要

将二维光子集成电路 (PIC) 扩展至三维 (3D) 结构,有望在扩大集成度、增强功能和提升 PIC 性能方面展现出巨大潜力。由于与 CMOS 兼容,硅基 3D PIC 取得了长足的进步。然而,硅的窄带隙 (1.1 eV) 限制了其在短波长应用(例如化学和生物传感、水下光通信和光学原子钟)中的应用。在本研究中,我们通过在蓝宝石 (Al2O3) 上异质集成氮化硅 (SiN) 和氮化铝 (AlN) PIC,开发了一个 3D 光子学平台。这些材料的宽带透明性使我们的平台能够在从紫外到红外的多个倍频程波长范围内工作。利用该平台,我们展示了AlN微腔中的高效光学非线性、低损耗、可调谐的SiN波导基光学元件,以及可见光和近红外光谱中AlN和SiN PIC层之间的光学连接,这暗示了其在集成量子系统中的潜在应用。我们的工作提出了一个超宽带3D PIC平台,为PIC的宽带和短波长应用提供了新的机遇。

#6英寸蓝宝石晶圆,高品质,可以直接用于膜层生长和键合

#离子注入铒代工

#6寸DUV步进式光刻代工,最小线宽180nm,超高性价比,可以只曝光

#提供8寸 8umSiO2热氧片

室温低损伤@GCIB抛光代工@束斑小(4-5mm)更均匀

#降低硬质材料化合物晶圆等绝大多数材料的表面粗糙度,比如金刚石 ,磷化铟,砷化镓,碳化硅

#提高复合衬底和镀膜膜层的器件层膜厚均匀性,

比如SOI LNOI LTOI SICOI 等 SMARTCUT得到的薄膜

或者镀膜所得到的膜层 ,比如镀了一层氮化硅,但是由于是cvd镀膜所得到的,表面的膜厚精度很差,粗糙度很差,可以通过粗糙度初步降低粗糙度,然后通过GCIB团簇离子束抛光来修整整面的膜厚均匀性 到0.5%以下举例:

未经过Trimming 工艺的 6寸LN/LTOI晶圆 数据:

Range:100-200A

经过Trimming 工艺的 6寸LN/LTOI晶圆 数据:

Range:60A以内

ALOOI晶圆;--氧化铝薄膜晶圆,键合工艺和镀膜工艺

TAOOI晶圆--氧化钽薄膜晶圆,镀膜工艺

SINOI晶圆;--超低损耗氮化硅薄膜晶圆,

SICOI晶圆;新型量子光学平台

6寸LTOI晶圆批量供应;铌酸锂的有力的竞争对手,薄膜钽酸锂晶圆

8寸LNOI晶圆;8寸LNOI助力更大规模薄膜铌酸锂产品量产

LN/LT-SOI/Si/SIN W2W&D2W异质集成

流片: 6寸 氮化硅 铌酸锂 硅光 超高性价比流片, 1个BLOCK的价格买一整片晶圆

划重点--全国产-超高性价比-6 寸硅光-氮化硅-铌酸锂流片白皮书

我们为客户提供晶圆(硅晶圆,玻璃晶圆,SOI晶圆,GaAs,蓝宝石,碳化硅(导电,非绝缘),Ga2O3,金刚石,GaN(外延片/衬底)),镀膜(PVD,cvd,Ald,PLD)和材料(Au Cu Ag Pt Al Cr Ti Ni Sio2 Tio2 Ti3O5,Ta2O5,ZrO2,TiN,ALN,ZnO,HfO2。。更多材料),键合(石英石英键合,蓝宝石蓝宝石键合)光刻,高精度掩模版,外延,掺杂,电子束光刻等产品及加工服务(请找小编领取我们晶圆标品库存列表,为您的科学实验加速。

请联系小编免费获取原文

引言

光子集成电路 (PIC) 已得到广泛的开发和部署,为电信、计算、检测和传感器等各种应用提供了集成解决方案。1–5 日益增长的数据处理能力需求推动了对具有更复杂和更多组件的大规模 PIC 的需求。6–9 对于传统的二维 (2D) 平面 PIC,在有限的芯片面积上集成大量光子器件通常需要许多光波导交叉。6–8 这反过来会导致严重的平面交叉损耗,10 限制了 PIC 的可扩展性。受利用多层金属互连实现片上连接的 3D 电子集成电路 (IC) 的启发,11,12 通过垂直堆叠和耦合将 2D PIC 扩展为 3D 结构,为紧凑且高密度的大规模 PIC 提供了可行的解决方案。 13–15

利用成熟的CMOS制造技术,硅基3D PIC取得了显著进展,实现了大规模光学相控阵、16高效光收发器、17高密度光开关18以及集成片上激光器19等演示。然而,硅固有的窄带隙限制了其在电信频段以外的应用,尤其是在需要更短波长的领域,例如原子物理、增强现实和虚拟现实以及生物传感。20与宽带材料进行异质集成是绕过这一限制的一种直接方法。 21 到目前为止,已通过垂直集成氮化硅 (SiN)、22,23 氧化铝 (Al2O3)24–26 和溅射氮化铝 (AlN)27,28,在硅衬底上开发了紫外和可见光波段的 3D PIC。这些 PIC 已应用于离子捕获、29 光检测、30压电驱动调制器 31 等。

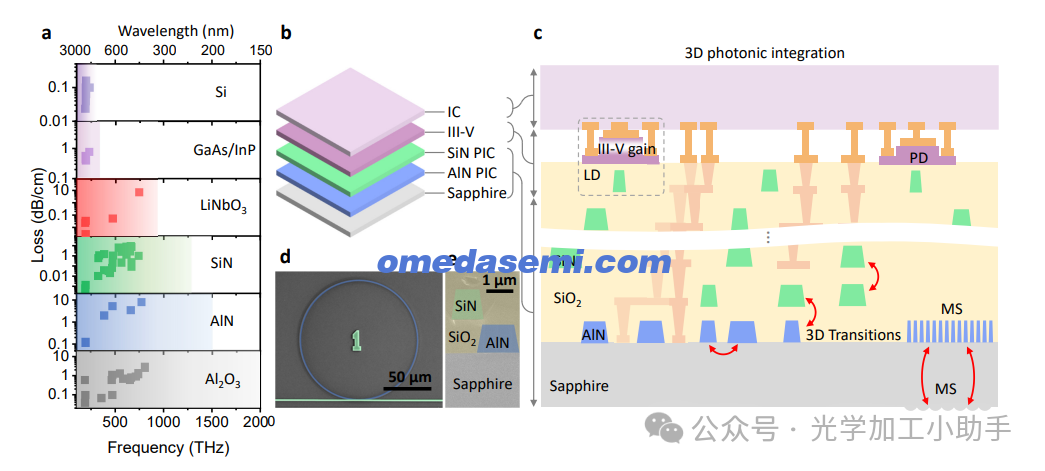

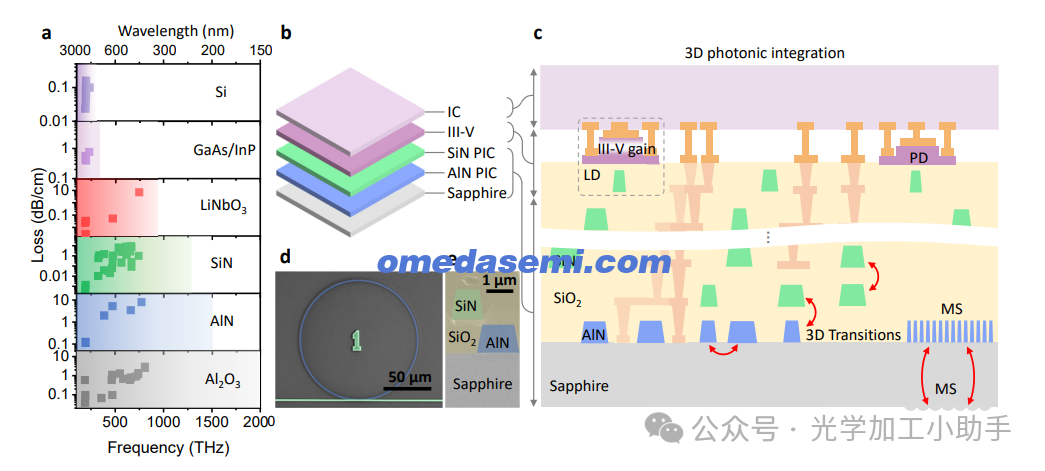

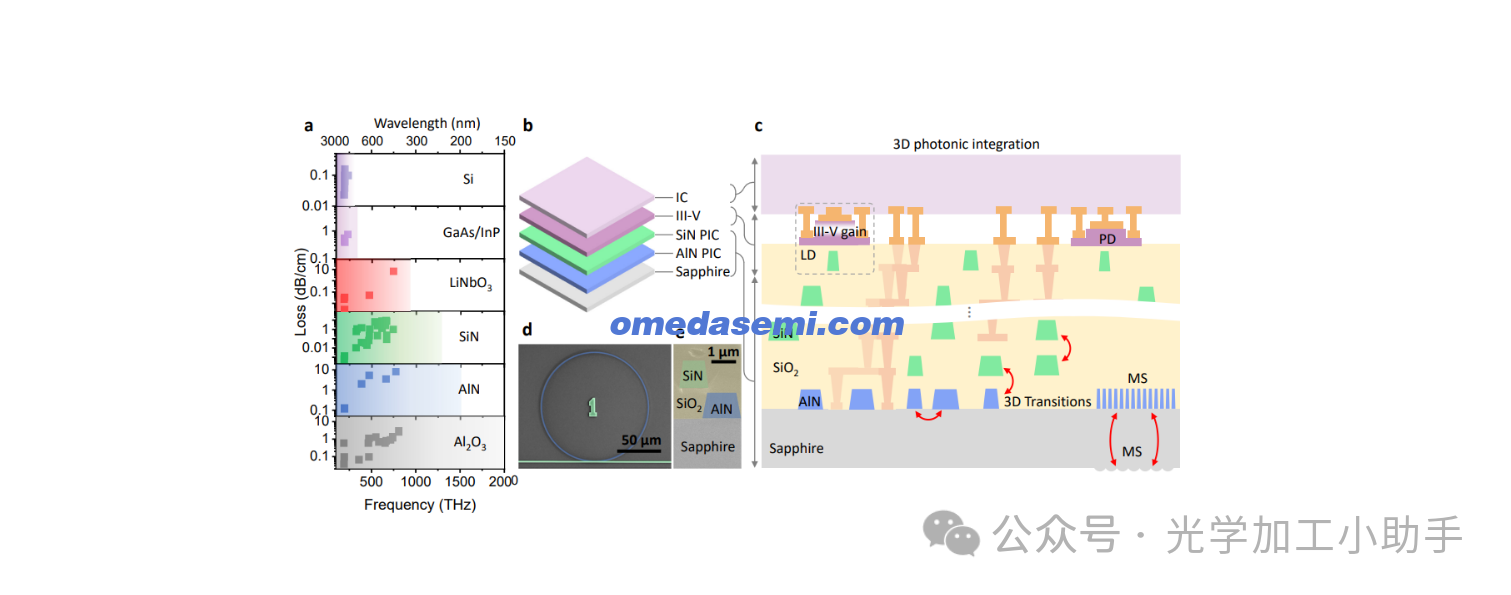

图 1:3D 异质 PIC。a,常见集成平台与本研究所用材料的光学损耗和透明窗口(颜色遮光区域)比较。b,3D 异质 PIC 的概念图。c,b 中 3D PIC 的横截面图。图中展示了未来 PIC 的功能扩展,例如控制 IC、III-V 族激光二极管 (LD) 和光子探测器 (PD)、放大多层异质 SiN-AlN PIC 以及其他光学微结构。d,垂直集成 AlN 微环和 SiN 波导的伪彩色扫描电子显微镜 (SEM) 图像。e,蓝宝石衬底上堆叠光子波导的伪彩色 SEM 横截面图像。

与硅 (Si)、砷化镓/磷化铟 (GaAs/InP) 和铌酸锂 (LiNbO3) 等常用集成材料相比,SiN、Al2O3 和 AlN 具有更宽的光学窗口,涵盖从紫外到红外波长。值得注意的是,它们在紫外光谱(波长低于 400 nm)内透明,而大多数广泛使用的集成材料无法进入该区域。这一特性对于当前的短波长集成光子学至关重要。32 此外,它们表现出较低的光传播损耗,与相应光谱带内的其他材料相当。为清晰起见,我们在图 1a 中总结了这些材料波导在其透明光谱窗口中的已报道光传播损耗。24,29,33–41,41–65 由于波导表面粗糙度和材料固有吸收引起的散射更强,光损耗在较高频率下趋于增加。材料制备和纳米制造工艺的进步有望大幅降低这些损耗,甚至有可能接近红外波段观测到的低损耗水平。由于其宽带和低损耗特性,SiN、AlN 和 Al2O3 是超宽带 3D 异质 PIC 系统的理想候选材料。

在本研究中,我们通过在蓝宝石衬底上垂直集成 SiN 和 AlN PIC,开发了一个 3D PIC 平台,该平台可提供从紫外到红外光谱的超宽光学透明性。为了评估该平台的稳健性,我们利用该平台的基本组件演示了可见光 (VI) 和近红外 (IR) 光谱区域的非线性和线性光学过程。我们制作了一个与 SiN 波导垂直耦合的低损耗 AlN 微环,其在近红外和 VI 波段的固有品质因数分别达到 2.36×106 和 3.35×105。这使得高效的二次谐波产生(SHG)效率达到12598%/W,并实现了单光子产生率达到24MHz/mW的自发参量下转换(SPDC)。我们还构建了该平台的关键SiN光学元件,工作在红外(IR)和紫外(VI)波段,包括高Q值微腔、低损耗波导螺旋、波分复用器和可调马赫-曾德尔干涉仪。此外,我们还演示了AlN和SiN PIC之间的垂直耦合。我们的工作提出了一种具有高性能线性度和非线性度的3D SiN-AlN PIC,展现出在集成量子光子学方面的巨大潜力。

结果

超宽带3D PIC

设想的3D PIC具有如图1b所示的分层架构,包括IC、III-V族增益层、SiN和AlN PIC层以及带有集成微结构(MS)的蓝宝石衬底。图1c展示了典型的横截面。IC用作驱动和控制单元,通过晶圆键合连接到PIC。11,17,66 III-V族材料提供有源光学元件,例如激光增益介质和光电探测器。67,68 SiN波导具有低光损耗,涵盖从红外到紫外的宽光谱。同时,它们的垂直堆叠与标准COMOS制造工艺高度兼容,使其成为3D PIC中光子路由的理想平台。然而,SiN 的中心对称结构固有地限制了 3D PIC 的关键功能,例如高效的二阶光学非线性和高速电光调制。AlN 具有高折射率 (2.2) 和大带隙 (6.2 eV),可在超宽带域内支持紧密限制、低损耗的波导。69 此外,AlN 具有强大的 χ(2) 非线性、电光效应和本征压电效应,可在 3D PIC 内实现重要的光子操作,包括通过 χ(2) 非线性进行波长转换和高速光调制。69

具有大带隙 (7.6 eV) 的蓝宝石衬底可提供超宽透明窗口,广泛应用于光学微结构。70 层间光学跃迁可以通过相邻层之间的倏逝耦合或通过微结构实现。

光调制和控制电路通过层间金属连接,类似于集成电路中的互连。

我们超宽带3D PIC概念的基础是SiN和AlN的异质集成。该方法充分利用了SiN的制造兼容性和AlN的非线性特性,从而支持开发具有先进光子功能的高密度、大规模3D PIC。在本研究中,我们重点研究了在蓝宝石衬底上集成AlN和SiN PIC,并使用SiO2作为包覆层。详细的制造工艺将在下一节中描述。图1d(制造过程中捕获)所示的典型3D PIC结构展示了蓝宝石衬底上的AlN微环(蓝色),周围环绕着SiO2,其上方是SiN总线波导(绿色)。图1e展示了垂直集成的SiN和AlN波导的横截面。

3D PIC 的制作

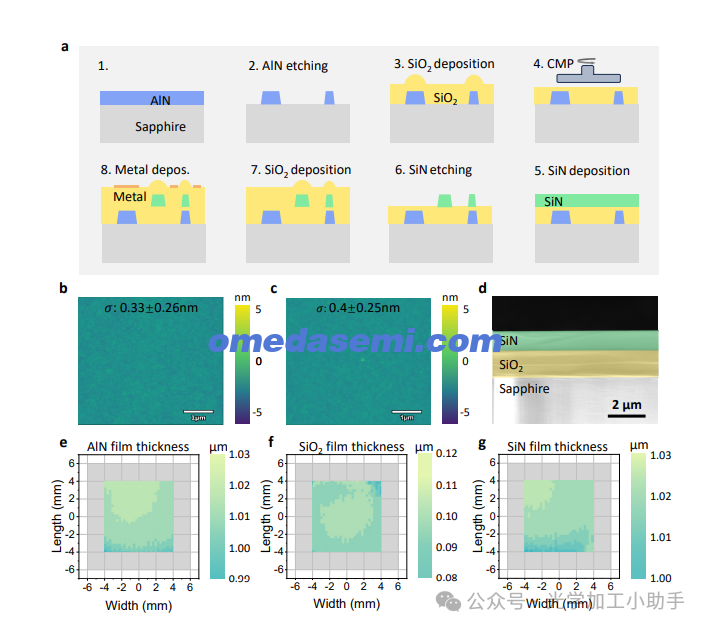

图 2:3D PIC 的制备。a,AlN 和 SiN PIC 垂直异质集成的制备工艺流程。b,抛光 SiO2 表面的二维 (2D) 原子力显微镜 (AFM) 照片,其均方根粗糙度 (σ) 为 0.33 ± 0.26nm。c,SiN 表面的二维 AFM 照片,其 σ 为 0.4 ± 0.25 nm。d,蓝宝石上集成多层膜横截面的伪彩色扫描电子显微镜 (SEM) 图像。

AlN 薄膜厚度图 (e)、扣除 AlN 厚度的 SiO2 薄膜图 (f) 以及SiN 薄膜图 (g)。

3D PIC 的制作流程如图 2a 所示。首先,使用 Fox16 光刻胶,采用电子束光刻 (EBL) 对 AlN 波导结构进行图案化。在 TMAH 显影液中显影后,采用 Cl2/BCl3/Ar 气体进行 ICP 干法刻蚀,蚀刻 AlN,将图案转移到 AlN 层中。然后,采用 PECVD 沉积 1.5 µm 厚的 SiO2 覆盖 AlN 波导。在氮气氛围中,在 1000°C 下进行 3 小时退火,以最大限度地降低 SiO2 包覆层的光吸收。采用 Fujmi PL-4217 抛光液和 IC-1000 抛光垫,通过化学机械抛光 (CMP) 对 SiO2 表面进行平坦化。抛光后的SiO2表面粗糙度(σ)为0.33±0.26nm(图2b)。随后,采用低压化学气相沉积(LPCVD)技术在平坦化的SiO2表面沉积一层厚度为1µm的SiN层(图2d),表面粗糙度σ为0.4±0.25nm(图2c)。我们使用MaN2410光刻胶,通过电子束刻蚀(EBL)工艺定义SiN PIC图案。在MIF319显影液中显影后,采用HCF3/O2溶液蚀刻SiN。之后,将SiN PIC在氮气环境中以1000℃退火,以降低SiN波导的光吸收。按照上述工艺,沉积并退火另一层厚度为1.5µm的SiO2包层。最后,沉积 Ti/Au 金属堆叠层作为移相器,用于控制 SiN 和 AlN PIC。我们在制备过程中监测了 AlN、SiO2 和 SiN 薄膜的厚度。如图 2e、f 和 g 所示,这些薄膜的厚度变化在约 ± 10 nm 以内,显示出良好的均匀性。

AlN PIC 的光学非线性

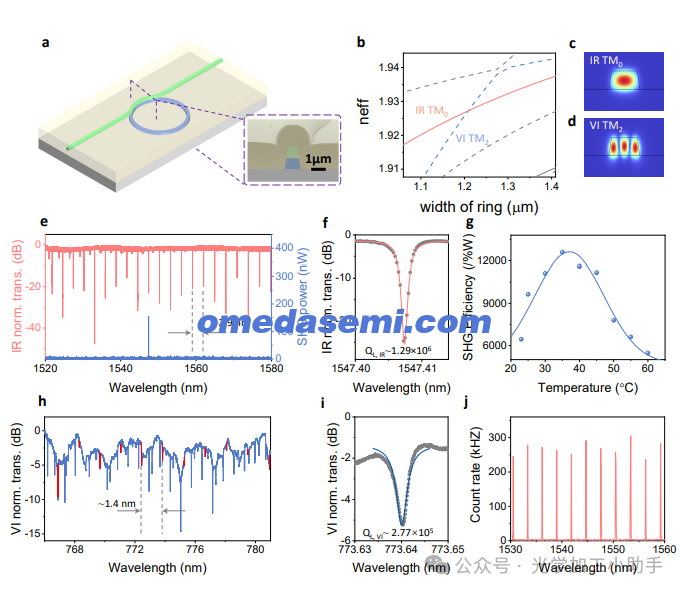

图 3:AlN PIC 的二次谐波产生 (SHG) 和单次谐波产生 (SPDC)。a,异质集成 AlN 微环与 SiN 波导。插图为耦合区域横截面的假彩色 SEM 图像。b,AlN 环形波导在红外 (IR,红色) 和可见光 (VI,蓝色) 模式下的光学有效折射率 (nef f) 模拟值。c 和 d,AlN 环形波导中的光学红外 TM0 和可见光 TM2。e,AlN 环的红外透射光谱(红色)和产生的二次谐波 (SHG) 光谱(蓝色)。f,e 中红外谐振的放大视图,与 SHG 峰值对齐。通过洛伦兹拟合,估计该谐振的负载品质因数 (QL,IR) 约为 1.29×106。g,SHG 效率随温度变化。h,AlN 环的可见光透射光谱。TM2 模式谐振以红色突出显示。 i,放大图:h 方向上 VI 共振与 SHG 峰对齐。其负载质量 (QL,VI)约为 2.77×105。j,通过 AlN 环的 SPDC 产生的单光子谱。

片上光学非线性在经典和量子光子学信息处理中都起着至关重要的作用。单晶 AlN 是电信红外、可见光和紫外波长范围内非线性现象的突出材料。58,71–74 为了展示我们 3D PIC 的非线性特性,我们制作了一个 AlN 微环腔,并在可见光和近红外光谱中展示了高效的二次谐波产生 (SHG) 和单次谐波直流 (SPDC)。如图 3a 所示,该微环器件包含一个位于蓝宝石衬底上的半径为 60 µm (Rr) 的 AlN 环,环上带有一个滑轮 SiN 波导。AlN 环和 SiN 层的厚度均为约 1 µm,间隙为 100 nm,并包裹在厚的 SiO2 包层中(图 3a 插图)。利用有限元模拟优化了环与波导之间的耦合(补充部分:高效的SHG和SPDC需要相位匹配,这可以通过基横磁红外模式(TM0)和高阶VI模式(TM2)来实现(图3c和d)。

它们的角频率(ωvi,ir)和动量(mvi,ir)的关系分别为ωvi = ωir,1 + ωir,2和mvi = mir,1 + mir,2,这需要两个模式的有效折射率匹配,nef f = mvi,irc/ωvi,irRr(其中c是真空光速)。对AlN环形波导中的模式色散进行了数值模拟,以获得nef f。通过设计AlN微环波导宽度,1550 nm TM0和775 nm TM2在∼1.2 µm的宽度处达到有效折射率匹配(图 3b)。

首先通过透射光谱表征了 AlN 微环的线性光学特性(补充材料第四部分)。红外光谱(红色)显示 TM0 模式的自由光谱范围 (FSR) 为 2.9 nm(图 3e)。1547.66 nm 处的相位匹配红外谐振与 VI 光谱(蓝色)中的 SHG 峰对齐,表明存在近临界耦合。图 3f 进一步显示了其放大视图。其负载品质因数 (QL,IR) 和本征品质因数 (Qin,IR) 分别为 1.29×106 和 2.36×106,对应的红外光传播损耗为 0.165 dB/cm。图 3h 显示了 AlN 微环的可见透射光谱,其中 FSR 约为 1.45 nm,具有多个模式系列。这些谐振主要包括 TM0、TE0 和 TM2 模式,其中 TM2 模式谐振以红色突出显示。

图 3i 显示了 773.82 nm 处 TM2 模式对准的 SHG 峰值,表明加载的品质因数 (QL,VI) 为 2.77×105,本征品质因数 (Qin,VI) 为 3.35×105,对应 VI 光传播损耗为 1.2 dB/cm。

如图 3a 所示,在 1547.41 nm 波长处,输入泵浦功率为 0.63 mW,观测到 200 nW 的 SHG 功率。考虑到 SiN 波导对红外 (IR) 和六方 (VI) 模式的边缘耦合效率分别为 20% 和 10%,估计片上 SHG 效率约为 6450%/W。为了最大限度地提高这一效率,我们通过热光效应精确对准红外 (IR) 和六方 (VI) 谐振腔,以实现完美的相位匹配(补充部分 IV)。在 38 ◦C时,SHG效率达到最大值12598 %/W(图3g),与理论值14878 %/W(补充材料第二部分)大致一致。

高效的二次谐波产生证实了AlN微环中光学模式的相位匹配,也表明了其实现高效单光子激发(SPDC)的潜力。接下来,我们进一步演示了SPDC的单光子产生(补充材料第四部分)。5 mW的泵浦功率在约773.8 nm的可见TM2模式谐振点处发射。产生的单光子由超导单光子探测器(SSPD)探测到。图3j是测得的单光子光谱,其有13个峰值,与AlN微环的13个红外谐振点一致,带宽超过30 nm。考虑到泵浦/单光子输入/输出耦合效率,以及测量系统的光子损耗(约6 dB),单光子产生效率约为24 MHz/mW,与理论值26 MHz/mW(补充材料第三部分)非常接近。 SiN PIC 的光学元件

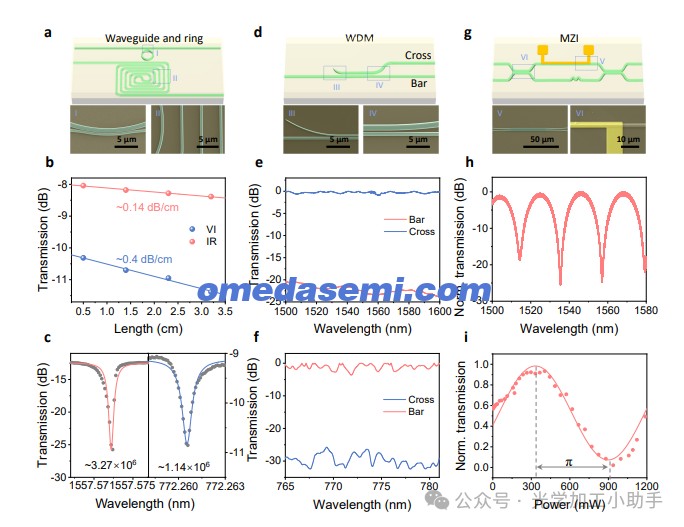

在我们的 3D PIC 中,SiN 波导在光子引导和操控方面发挥着关键作用,而这通常要求基于 SiN 波导的光学元件具有较低的光传播损耗。为了评估这些损耗,我们在 SiO2/蓝宝石上制作了 SiN 螺旋波导(横截面积为 1 µm × 1.2 µm),如图 4a 所示。

图 4:SiN PIC 的光学元件。a,SiO2/蓝宝石衬底上 SiN 微环和螺旋波导的示意图。环 (I) 和波导 (II) 的假彩色 SEM 图像。b,分别测量了不同长度 SiN 螺旋波导在红外 (IR) 和六方 (VI) 光波段的透射强度。c,SiN 光学微环谐振器,其固有品质因数分别为 3.27×106 和 1.14×106,分别适用于红外和六方 TM0 模式。 d,WDM 示意图及其放大区域(假彩色 SEM 图像 (III) 和 (IV)。e 和 f,红外和六波段条形端口(蓝色)和十字端口(红色)的 WDM 透射光谱。g,单臂上带有热移相器的马赫-曾德尔干涉仪 (MZI) 示意图。MMI (V) 和电极 (VI) 的假彩色 SEM 图像。h,MZI 的归一化透射光谱。i,输入波长为 1550 nm,通过热功率调谐的 MZI 的归一化透射强度。

图 4b 中以点的形式绘制了不同长度波导的 TM0 模式的透射强度。通过对这些数据点进行线性拟合,我们分别提取了红外 (IR) 和紫外 (VI) 波段的传播损耗,分别为 0.14 dB/cm 和 0.4 dB/cm。此外,我们还制作了一个 SiN 微环,如图 4a 所示,其半径为 60 µm,横截面积为 1 µm × 1.2 µm。

该微环表现出典型的固有品质因数:TM0 模式的 3.27×106(波长 ∼ 1550 nm)和1.14×106(波长 ∼ 775 nm)(图 4c),对应的损耗分别为 0.12 dB/cm和 0.33 dB/cm,这与螺旋波导的估计值一致波分复用 (WDM) 是集成光学器件的关键组件。在我们的 3D PIC 中,SiN WDM 用于合并和分离红外 (IR) 光分支。如图 4d 所示,SiN WDM 由两个闭合的平行锥形波导组成,耦合间隙为 600 nm,耦合长度为 1 mm。该器件针对红外 (IR) 波段的光学 TM0 模式进行了优化,设计细节可在补充材料第五部分中找到。

图 4e 是红外波段校准后的 WDM 传输光谱。红外光几乎全部耦合到交叉端口,只有一小部分(< -20 dB)穿过条形端口。同时,插入损耗仅为 0.3 dB 左右。相反,对于红外波段,条形端口具有近乎单一的传输特性,而交叉端口的传输特性极小(< -25 dB),相应的插入损耗为 1.1 dB。

马赫-曾德尔干涉仪 (MZI) 是用于控制 PIC 中光子路由的典型组件。为了在我们的 3D PIC 中演示此功能,我们制作了一个 SiN 非平衡 MZI,其设计如图 4g 所示。该 MZI 包含两个 50/50 多模干涉 (MMI) 耦合器,并在一个耦合器臂上放置一个移相器。由于 SiN 的材料结构对称,它没有电光系数。因此,我们使用加热器作为移相器,通过热光效应来调节光模式的相位。SiN 的热光系数为 4.7×10−5/K,小于 Si 的热光系数(1.84×10−4/K)。我们进行了数值模拟以优化 MMI 的结构参数(补充材料第五部分)。非平衡MZI的红外透射光谱如图4h所示,呈现出典型的正弦振荡,消光比超过25 dB。此外,我们将输入光波长固定在1550 nm,并通过加热器微调MZI相位来控制光输出路径和输出功率。图4i显示了单个MZI端口的归一化输出功率,该功率取决于加热器的驱动功率。在约600 mW的功率下实现了π相移。

跨AlN和SiN层的光链路

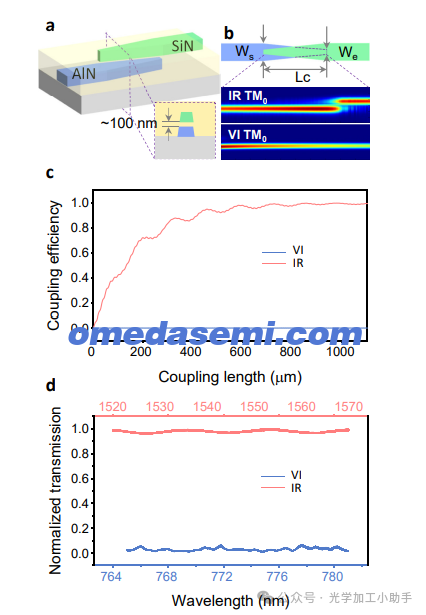

图 5:AlN 和 SiN PIC 之间的光学链路。a,垂直耦合器示意图由 AlN 和 SiN 锥形波导组成,波导在垂直方向上由间隙隔开。b,沿定向耦合器模拟的红外和红外 TM0 模式的模式分布。c,模拟的 AlN 到 SiN 的耦合效率与耦合器长度 (Lc) 的关系。d,测得的耦合器透射光谱。

除了高性能器件外,堆叠光子层之间可靠的光互连对于3D PIC至关重要。本文,我们提出了一种绝热锥形耦合器来连接SiN和AlN PIC层,如图5a所示。该耦合器的设计耦合间隙为100 nm,尖端宽度(We)为100 nm,波导宽度(Ws)为1.2 µm,耦合长度为Lc(图5b)。我们进行了数值模拟,以优化Lc,从而最大限度地提高耦合器的耦合效率。基于我们之前设计的3D PIC组件,我们选择了1550 nm的红外TM0模式和775 nm的紫外TM0模式作为工作光模式。模拟耦合效率随耦合长度Lc的变化如图5c所示。对于红外 (IR) 模式,耦合效率随 Lc 的增加而增加,并在 Lc > 1000 µm 时达到接近 1 的饱和。而六方 (VI) 模式在 AlN 和 SiN 锥形波导之间耦合较弱,

从而阻碍了有效的光交叉。耦合器波导内两种光模式的模式分布如图 5b 所示。图 5d 绘制了耦合器器件在红外 (IR) 和六方 (VI) 波段的校准光透射光谱,分别显示了红外 (IR) 和六方 (VI) 模式的接近 1 和接近零的耦合效率。为了实现较短波段的高效垂直耦合,需要进一步优化耦合器结构。此外,垂直多模干涉 (MMI) 75、中间定向耦合器 76 和光栅耦合器 77 等替代方法为实现高效的宽带耦合提供了可行的解决方案。

讨论

AlN、SiN 和 Al2O3 具有从紫外到红外的超宽带光学透明性,

远远超过硅。29,56,65,69,74 这使得它们成为短波长 PIC 新兴应用的理想候选材料。20 利用这三种材料,

我们通过异质集成开发了 3D PIC,并展示了高效的 SHG 和 SPDC,以及低损耗和可调的光学元件。此外,我们还探索了跨垂直堆叠层的光学连接。我们还通过数值模拟评估了相邻语音层之间的超低交叉损耗(补充材料第六部分)。

尽管3D PIC 在光学非线性和线性方面都表现出良好的性能,但仍有很大的改进空间。首先,需要优化器件制造工艺,以进一步降低光学损耗。例如,SiN PIC 在紫外和红外波段的光损耗已分别低至 1 dB/m 和 0.1 dB/m,45,46,53,54,远优于我们目前的研究结果。其次,应进一步优化 3D PIC 的结构,以实现宽带光学垂直耦合。这可能涉及用 Al2O3 替代 SiO2 包层材料,降低 AlN 和 SiN 波导的厚度,以及探索其他耦合结构,例如垂直多模干涉仪和光栅耦合器。14,23,26,30 最后,其他工作于紫外至可见光波段的光学元件仍有待探索。

结论

综上所述,我们开发了一个基于 AlN 和 SiN 层垂直异质集成的 3D PIC 平台,实现了从紫外到红外波段的宽带工作。该平台的高效光学非线性已通过在 AlN 微环中进行的 SHG 和 SPDC 实验得到验证。此外,我们还制备了高性能SiN光学元件,例如低损耗微环和波导、WDM器件和可调MZI,展示了其在3D PIC中巨大的应用潜力。

通过紧密间隔波导之间的衰减场耦合,实现了AlN和SiN PIC之间的光学层间跃迁。通过垂直堆叠额外的SiN波导层,我们的3D PIC的可扩展性和集成密度可以进一步提升。

此外,能够在紫外至可见光波长范围内产生和探测光子的III族氮化物薄膜78可以直接集成到PIC上,从而将众多片外光学器件集成到单个芯片中。基于III族氮化物的集成电路的集成也为共同开发3D电子-光子集成电路生态系统提供了途径,15,79 有望为经典信息处理和量子信息处理开辟新的可能性。