#钽酸锂电光调制器 #薄膜钽酸锂晶圆 #钽酸锂光波导

在现代网络中,电气和光学系统的接口是一个普遍的需求。随着数据流量的增加和微电子设备之间更大连接性的需求,要求能够在这两种系统之间传递信息的器件具备越来越严格的要求。竞争性的占地面积、效率和带宽指标推动了基于Pockels材料的集成电光调制器在这些任务中的应用。由于其在传统大块电光调制器中的广泛使用,并且受“在绝缘体”晶片的可用性推动,基于铌酸锂的器件取得了重大进展。最近,基于钽酸锂的器件展现出了更有利的特性,具有类似的Pockels效应,但表现出较低的偏置漂移和较低的双折射,同时同样受益于在无线射频滤波器中的现有体积使用。尽管集成调制器取得了重大进展,但这些新出现的铁电调制器仍无法通过标准化工艺(如倒装芯片键合)与电子设备紧密集成。后者对于确保低射频损耗和获得紧密的电子-光子集成至关重要。事实上,这种芯片对芯片或芯片对晶片(CoW)的混合键合已经在微电子学中用于先进的GPU或CPU,并且在很大程度上依赖于如铜Damascene工艺等标准化的制造流程。在这里,我们通过在集成钽酸锂调制器的制造中引入铜Damascene工艺,克服了这一瓶颈。铜Damascene工艺不仅提供了平坦的表面,还能提供低损耗电极,从而实现直接的芯片对晶圆键合,用于创建堆叠的芯片单元。我们展示了采用铜Damascene工艺的调制器,其微波损耗比依赖传统金电极的设计低约10%。我们的结果使得我们能够达到与其他低电阻但较不常见的金属(如银)制造的电光调制器相当的数据传输速率。具体来说,我们制造的调制器在PAM4和PAM8传输方案中分别能够实现416和540 Gbit/s的数据传输速率,同时保持比特错误率低于25%的SD-FEC阈值。结合钽酸锂作为Pockels材料的商业可用性,我们的结果为将电光调制器与微电子集成电路直接集成到可扩展的芯片对晶片嵌入提供了一条可行的道路。

集成电光(EO)调制器为电信号与光信号之间交换信息提供了可扩展的平台,从而为高速光通信提供了替代的构建模块[1, 2],并支持芯片到芯片互连等新技术[3, 4]。基于Pockels材料(如铌酸锂和钽酸锂)[5, 6]的集成EO调制器的进展,推动了该架构在器件紧凑性、调制效率和带宽方面的突破[7, 8]。对传统马赫-曾德调制器(MZM)架构的进一步改进可以通过修改光子或电极设计来实现。例如,基于谐振腔的结构[9–11]可以提高调制效率并减小占地面积,但这通常以电压-带宽的权衡为代价。另一方面,采用微结构电极设计,如电容负载同轴波导(CPW)电极,可以进一步减少微波损耗并增加带宽[12, 13]。带宽的进一步提高可以依赖于新的电极材料,这些材料能为与下层光波相互作用的微波信号提供更低的传播损耗。例如,使用低电阻材料如银制造CPW电极,可以使调制器达到数百Gbit/s的数据传输速率[14]。

大规模部署这种高性能的集成Pockels EO调制器将需要适用于光子集成电路(PIC)的体积制造方法,这些方法同时具备高质量的光子组件和微波电极。尽管这些Pockels PIC的光子组件已经达到此级别的制造[5, 6, 15],但它们的电极仍然无法与商业硅PIC代工厂现在提供的相比[16]。具体而言,在Pockels PIC中实现低损耗电极,并确保与行业采用的标准化制造流程兼容,仍然是一个未解决的挑战。在这些过程中,铜Damascene图形化技术通过实现更高层次的组件互连,提供了独特的机会,能够在半导体电路中增加如晶体管和电子路由层之间的多层连接。进一步的工艺发展还可以通过退火激活热膨胀,形成平整芯片和晶片之间的紧密铜互连[17–19]。这些技术有效地克服了凸点键合中普遍存在的寄生效应,并已在混合键合系统的组装中发挥了重要作用,如芯片堆叠的GPU和CPU[20]。

在这里,我们通过在钽酸锂PIC的制造中引入铜Damascene工艺,解决了这一挑战。我们的工艺利用了成熟、低成本且广泛应用的方法来制造微电子学和硅光子学中的电子结构[16]。通过这种方法,我们展示了集成的EO调制器,其微波损耗比依赖传统金电极的器件低约10%,同时保持了Pockels效应在调制效率(VπL)方面的优势。同样重要的是,铜Damascene工艺产生的平坦表面有可能直接应用芯片对芯片或芯片对晶片键合技术。接着,我们展示了这些器件在高速脉冲幅度调制(PAM)数据传输中的实用性,其中我们的器件的性能与依赖其他低电阻但较不常见材料(如银)制造的调制器相当[14]。

#离子注入铒代工

#6寸DUV步进式光刻代工,最小线宽180nm,超高性价比,可以只曝光

#提供8寸 8umSiO2热氧片

室温低损伤@GCIB抛光代工@束斑小(4-5mm)更均匀

#降低硬质材料化合物晶圆等绝大多数材料的表面粗糙度,比如金刚石 ,磷化铟,砷化镓,碳化硅

#提高复合衬底和镀膜膜层的器件层膜厚均匀性,

比如SOI LNOI LTOI SICOI 等 SMARTCUT得到的薄膜

或者镀膜所得到的膜层 ,比如镀了一层氮化硅,但是由于是cvd镀膜所得到的,表面的膜厚精度很差,粗糙度很差,可以通过粗糙度初步降低粗糙度,然后通过GCIB团簇离子束抛光来修整整面的膜厚均匀性 到0.5%以下举例:

未经过Trimming 工艺的 6寸LN/LTOI晶圆 数据:

Range:100-200A

经过Trimming 工艺的 6寸LN/LTOI晶圆 数据:

Range:60A以内

ALOOI晶圆;--氧化铝薄膜晶圆,键合工艺和镀膜工艺

TAOOI晶圆--氧化钽薄膜晶圆,镀膜工艺

SINOI晶圆;--超低损耗氮化硅薄膜晶圆,

SICOI晶圆;新型量子光学平台

6寸LTOI晶圆批量供应;铌酸锂的有力的竞争对手,薄膜钽酸锂晶圆

8寸LNOI晶圆;8寸LNOI助力更大规模薄膜铌酸锂产品量产

LN/LT-SOI/Si/SIN W2W&D2W异质集成

流片: 6寸 氮化硅 铌酸锂 硅光 超高性价比流片, 1个BLOCK的价格买一整片晶圆

划重点--全国产-超高性价比-6 寸硅光-氮化硅-铌酸锂流片白皮书

制造过程。

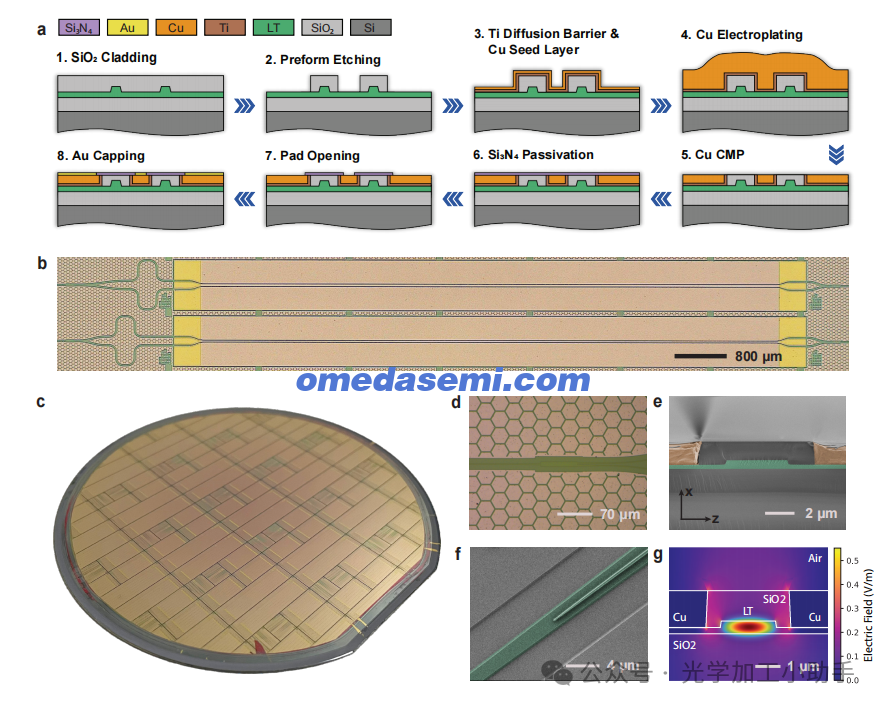

器件是从商业上可用的X切割薄膜钽酸锂(TFLT)晶片(NANOLN)制造的,该晶片由600 nm的钽酸锂(LiTaO3,LT)、4.7 µm的SiO2和525 µm厚的高电阻硅基板组成。TFLT PICs是使用基于类金刚石碳硬掩膜的蚀刻技术制造的,该技术可以可靠地生产钽酸锂和铌酸锂的PIC[5, 6]。钽酸锂的蚀刻深度为320 nm,留下了280 nm厚的薄层,以实现高效的电光调制和微波与光信号之间的适当相位匹配。更多关于制造流程的详细信息可以在补充材料中找到。

图1. 基于铜Damascene工艺的薄膜钽酸锂(Cu-TFLT)马赫-曾德调制器(MZM)。

a. 使用Damascene工艺在图案化的TFLT晶片上制造铜电极的工艺流程。

b. 两个Cu-TFLT MZM的显微镜图像,每个MZM由两个1x2多模干涉(MMI)耦合器、一个不平衡臂和一对推挽相位调制器组成。黄色表示金色封顶垫,用于稳定和高效的电极探针。

c. 制造的4英寸晶片的照片,包含数百个Cu-TFLT MZM。

d. 显微镜图像,显示一个MMI耦合器,周围是蜂窝状铜填充物,用于确保均匀平面化。

e. 彩色扫描电子显微镜(SEM)图像,显示钽酸锂波导(绿色)和铜电极(橙色)的横截面。波导的肋高为320 nm,薄层厚度为280 nm。铜电极厚度为1.8 µm,表面覆盖了100 nm的氮化硅钝化层以防止氧化。

f. 彩色SEM图像,显示一个双层锥形结构,用于实现芯片与单模光纤之间的高效宽带边缘耦合(每个面耦合损耗约为3 dB)。最小的图案化特征尺寸为200 nm。

g. 数值模拟的Cu-TFLT MZM横截面中的微波和光场分布。

接下来,图1(a)所示的铜Damascene工艺被引入,用于制造低损耗的行波电极。该工艺依赖于在硅氧化物包层中蚀刻电极嵌入物,随后进行铜电镀和化学机械平坦化(CMP)。该工艺生产出定义良好的电极,并且表面光滑,可能适用于芯片对晶片的键合。更多关于制造的信息可以在方法部分找到。图1(b)显示了两种制造的铜TFLT MZM,其有效调制长度为6 mm。图1(c)展示了制造的4英寸晶片,包含数百个铜TFLT MZM,突显了其在下一代光子系统可扩展集成的潜力。为了提高晶片在CMP工艺后的均匀性,非活跃区域使用了填充铜图案,这在图1(b-d)中可见。如图1(d-f)所示,每个调制器由50:50的1×2多模干涉(MMI)耦合器、电光相位调制器(以推挽配置工作)和双层锥形结构组成,用于增强PIC与光纤的耦合效率[21]。如图1(g)所示,调制器的微波和光模式的紧密限制确保了两种场的强重叠,从而提高了调制效率。

电气传输。正如补充材料中所述,基于硅晶片制造的铜Damascene CPW测试结构为制造的TFLT调制器提供了理想的器件参数。

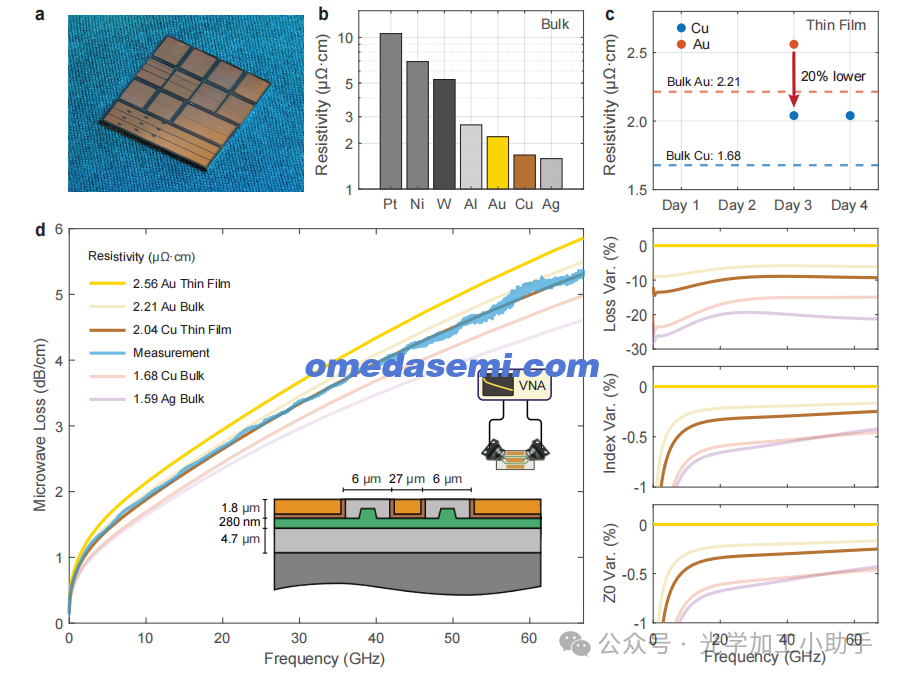

图2. Cu-TFLT MZM的电气表征

a. 在硅上制造的铜Damascene共面波导(CPW)电极测试结构的照片。

b. 7种最具导电性的元素金属的电阻率,按从大到小的常温体积电阻率排序。

c. 测量的薄膜金和铜的电阻率,以及它们随时间的变化。金薄膜(796 nm)通过电子束蒸发沉积,铜薄膜(1170 nm)通过电镀沉积。两种金属薄膜均沉积在具有2 µm二氧化硅的硅载体晶片上,并使用四点探针和机械轮廓测量相结合进行测量。电镀铜的电阻率在室温下48小时内发生了24%的下降,原因是自退火效应,并稳定在2.04 µΩ·cm,比测得的金薄膜电阻率低20%。

d. 测量的铜CPW的微波损耗以及数值模拟的不同电阻率材料组成的电极的损耗,这些材料共享与制造的器件相同的几何结构。插图:微波传播损耗测试装置及所使用的主要尺寸,与图1(a)中定义的材料堆栈一致。侧面面板:与薄膜金相比,模拟的CPW的微波损耗、微波指数和特征阻抗(Z0)的相应变化。

图2(a)提供了这些测试结构的照片。通过测量,确认了铜CPW的微波传输特性得到改善,这是由于铜较低的电阻率。作为参考,图2(b)显示了这一电阻率,并与其他常用于微电子学和光子学中的元素金属进行比较。图2(c)所示的从片阻抗测量中提取的电阻率值确认了使用铜代替金的优势,尤其是在经过48小时的自退火效应后[22]。为了评估制造的CPW的性能,使用其S矩阵参数的电气表征来推导诸如微波损耗和有效折射率等特性。在本研究中,S矩阵使用67 GHz向量网络分析仪(Rohde & Schwarz ZNA67)进行测量。一对高速度微波探针(GGB)通过使用穿通开短匹配(TOSM)标准进行校准,用于将微波信号输入CPW的输入端口并从输出端口收集信号。图2(d)显示了16 mm长CPW的微波损耗测量结果,间隙为6 µm,中心信号电极宽度为27 µm。作为参考,图中还提供了与制造的器件几何特征相同的不同电阻率的CPW的模拟数据。该数据表明,使用铜代替金可以实现约10%的微波损耗减少。这种较低的电阻率还导致稍微低的微波传播指数和特征电极阻抗。

电光调制。

评估调制器性能的更直接方式是测量其电光调制特性,包括准静态半波电压(Vπ)和3 dB电光带宽。准静态Vπ是通过对CPW电极施加低频三角电压信号并同时记录光输出进行测量的。关于这一过程的详细信息在补充材料中提供。为了生产出能够实现最佳调制特性的器件,我们对各种CPW几何形状进行了有限元仿真(COMSOL Multiphysics),计算了预期的VπL和光损耗。

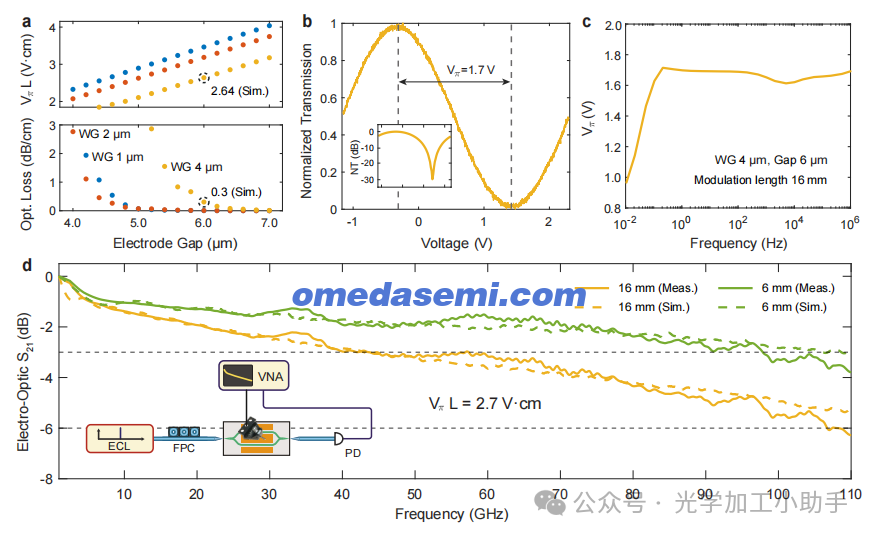

图3. Cu-TFLT MZM的电光表征

a. 不同波导宽度和电极间隙值的MZM的VπL和光吸收损耗的数值仿真。对于波导宽度为4 µm和电极间隙为6 µm的器件,仿真得到的VπL为2.64 V·cm。

b. 16 mm长器件的归一化光传输与施加电压的关系,显示Vπ值为1.7 V。

c. 测量的Vπ与施加电压信号的扫频频率的关系。

d. 分别具有16 mm和6 mm调制长度的器件的小信号电光响应。测得的VπL与a中4 µm波导宽度和6 µm电极间隙的预期值相符。插图:电光响应测量的测试装置。

图3(a)展示了这些仿真结果,确定了制造的器件几何形状,其间隙为6 µm,波导宽度为4 µm。图3(b)展示了调制器的归一化传输与施加电压(以100 Hz的频率变化)之间的关系,突出显示了理想的正弦波形和Vπ为1.7 V。由于测得的器件具有16 mm的有效调制长度,这对应于VπL为2.7 V·cm,略高于模拟值2.64 V·cm。插图中的dB尺度图显示了30 dB的消光比,这对于进行PAM4和PAM8等高级通信实验至关重要。我们还研究了Vπ对施加电压信号频率的依赖性,如图3(c)所示。我们的调制器在1 Hz到1 MHz的广泛频率范围内呈现出非常稳定的Vπ。这一平坦响应与先前报道的使用金CPW的铌酸锂MZM的响应不同,后者在低于100 kHz的频率下被观察到非常不稳定[23]。凭借这种稳定的Vπ,不再需要加热器,它们具有稳定的响应但高功耗和串扰,用于调制器偏置。图3(d)显示了我们调制器的电光响应,频率可达110 GHz。对于16 mm长的器件,3 dB电光带宽达到了40 GHz,而对于6 mm的器件,带宽高达100 GHz,二者的CPW间隙为6 µm。这一优异的电光调制特性表明,我们的调制器可以用于高速通信系统,以满足对高速数据传输不断增长的需求。

光通信。

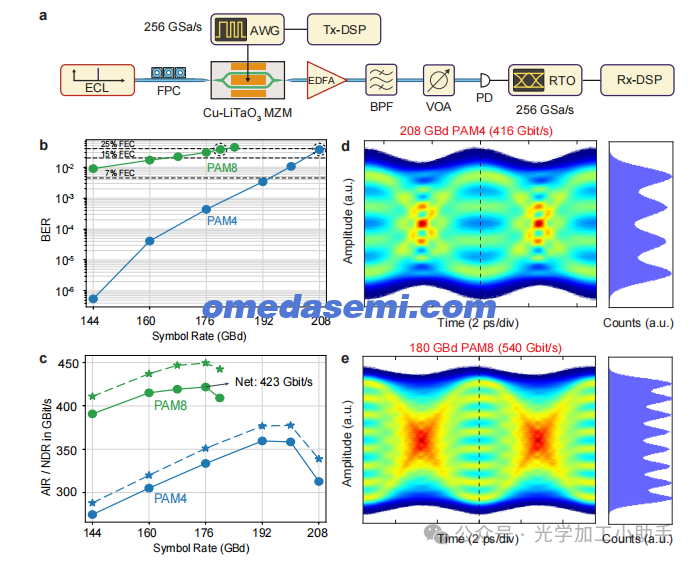

图4. 使用强度调制直接检测(IMDD)进行的数据传输实验,采用Cu-TFLT MZM

a. 实验装置:外腔激光器(ECL)用作光源,光纤偏振控制器(FPC)调节光的偏振状态。光输入和输出与Cu-TFLT MZM的耦合通过一对透镜光纤实现。驱动信号由发射端数字信号处理(Tx-DSP)合成,并由任意波形发生器(AWG)生成。调制后的光信号通过掺铒光纤放大器(EDFA)放大,带外放大自发辐射(ASE)噪声通过可调带通滤波器(BPF)抑制。放大的信号随后通过可变光衰减器(VOA),然后由光电二极管(PD)检测。高速实时示波器(RTO)对结果信号进行采样,该信号随后通过接收端数字信号处理(Rx-DSP)进行离线处理。

b. 测量的比特错误率(BER)与PAM8(绿色)和PAM4(蓝色)信号的符号速率的关系。横向黑色虚线表示25%和15%软判决前向错误校正(SD-FEC)以及7%硬判决前向错误校正(HD-FEC)的阈值。

c. 提取的可用信息率(AIR,虚线)和相应的净数据速率(NDR,实线),测量结果的BER值低于25% SD-FEC阈值。使用PAM8信号,在符号速率为176 GBd时,最大净数据速率为423 Gbit/s。

d, e. 眼图和相应的直方图,在符号槽的中心(由垂直虚线表示)采集,取自b中圈出的数据点。

为了展示我们Cu-TFLT MZM的卓越性能,我们进行了高速强度调制和直接检测(IMDD)信号实验。该实验装置如图4(a)所示。外腔激光器(ECL,1550 nm时为17.8 dBm)提供光载波。我们使用高速任意波形发生器(AWG,M8199B,Keysight)生成电驱动信号,并通过20 cm长的射频电缆、宽带射频放大器和110 GHz射频探针将信号输入到MZM的CPW中。我们基于伪随机比特序列合成了各种脉冲幅度调制(PAM)信号,并应用了具有β = 0.05滚降因子的根升余弦脉冲整形滤波器。我们通过应用线性最小均方误差(MMSE)预失真来考虑频率依赖的射频损耗,直到喂入探针的输入端口。CPW通过第二个110 GHz射频探针与50 Ω电阻终止。如图3(c)所示,Cu-TFLT调制器的电光稳定性使得能够在正交点进行可靠的直流偏置调制,且偏置T附加到第二个探针上。MZM在正交点操作时的输出光功率为5.6 dBm,超过了典型高速光以太网收发器规格中的功率要求[24]。尽管如此,实验中仍需要一个附加的掺铒光纤放大器(EDFA),以为接收端的高速光电二极管(8.5 dBm)提供足够的功率水平。请注意,实际的收发器实现可以依赖于光电二极管后的足够宽带的放大器,从而使EDFA不再必要。在我们的实验中,通过可调带通滤波器(BPF)抑制了EDFA的带外放大自发辐射(ASE)噪声,并使用可变光衰减器(VOA)调整光电二极管输入端的功率水平为8.5 dBm。光电二极管输出端的电信号通过实时示波器(RTO,UXR 1004A,Keysight)进行数字化,示波器具有105 GHz的模拟带宽和256 GSa/s的采样率。数据最终由离线接收器DSP(Rx-DSP)提取,包含重采样至2 Sa/symbol、时钟恢复、线性Sato均衡和附加的决策导向最小均方(DD-LMS)均衡器。在数据传输实验中,我们生成并接收了符号速率在144 GBd到208 GBd之间的PAM4和PAM8数据信号。图4(b)显示了不同PAM信号的测量比特错误率(BER)与符号速率的关系。横向虚线表示典型软判决(SD)前向错误校正(FEC)在25%和15%开销下的阈值,以及硬判决(HD)FEC在7%开销下的阈值。结果显示,我们可以传输180 GBd的PAM8信号和208 GBd的PAM4信号,同时其对应的BER分别为3.76 × 10−2和3.56 × 10−2,仍低于25%的SD-FEC限值。图4(c)中,我们进一步计算了基于对数似然比的广义互信息(GMI),并使用加性白高斯噪声通道模型[25]。虚线曲线表示可达的信息速率(AIR),即GMI与符号速率的乘积。图4(c)中的实线曲线显示了BER低于25% SD-FEC限值的测量净数据速率,其中净数据速率是通过将传输的线路速率与与标准化GMI阈值相关联的编码速率相乘得到的,编码速率从[26]中提取。结果表明,使用PAM8信号,在符号速率为176 GBd时,达到了449 Gbit/s的最高AIR。这对应于423 Gbit/s的净数据速率,达到了高带宽薄膜铌酸锂MZM的结果[27]。需要注意的是,一些结果,如PAM4符号速率,受到我们驱动电子设备带宽的限制,而不是MZM本身的限制。

讨论。

从材料的角度来看,铜的低电阻率使其非常适合最小化制造的调制器中的微波损耗。如图2(d)所量化的,这种较低的电阻率相比金等传统材料(具有较高电阻率)改善了微波传输。我们的电镀铜结果也显示,与使用电子束蒸发的铜基调制器[28]相比,电镀铜提供了更低的损耗,并且提供了制造更厚金属结构的更实用方法,最终还引入了制造多层电子结构的可能性。这一改进在数据传输过程中至关重要。如图4中我们的脉冲幅度调制结果所示,依赖铜CPW的调制器可以达到与使用其他低电阻金属(如银)实现的CPW相同的数据传输速率[14]。数据传输的进一步改进可能涉及将我们的调制器集成到适用于相干通信的发射器架构中[29, 30]。

通过对图1(a)所示的PIC材料堆叠进行轻微修改,我们可以进一步减少微波损耗。我们的仿真表明,这些损耗的部分来源于传播的微波场与芯片硅基底之间的重叠。因此,在TFLT晶片上实现铜基调制器,并使用更大的底部氧化层将LT薄膜与基板隔离开,可能会进一步减少损耗。最后,CPW边缘的电流集中效应也会导致我们的损耗[31]。如补充材料中进一步探讨的,我们可以通过采用电容负载的CPW设计来缓解这一效应,这可以将微波损耗降低至50 GHz时约1 dB/cm。这样的电极会使微波场的有效折射率高于调制光场,从而导致两种场之间的相位失配,这对于电光调制并不理想。然而,兼容减少其他损耗贡献的器件修改,如更厚的底部氧化层[32]或硅基板的下切[33],可以减少这种失配,使得低损耗的电容负载电极适应我们的铜Damascene平台。这一改进可能会使微波损耗接近我们电容负载CPW测试结构中测量的1 dB/cm。

除了降低微波损耗外,采用铜基工艺制造集成电光调制器,还使片上电子更加接近目前商业硅光子集成电路(PIC)所使用的那些[16]。这种相似性可能对适应基于铜凸点键合的三维(3D)硅光子集成的新兴趋势非常有用[34]。在这里,由铜Damascene工艺产生的平坦表面对于芯片对晶片的混合键合起到了关键作用,从而为3D堆叠芯片提供了所需的连接。这些技术,已经应用于GPU和CPU的组装,现在可以与我们的钽酸锂调制器一起使用。由这种密集电子共集成形成的器件承诺将在数据通信[4]到人工智能[35, 36]等领域中发挥作用。

总之,我们在钽酸锂电光调制器的制造中引入了铜Damascene工艺。我们的工艺相比依赖金电极的调制器实现了10%的微波传输损耗降低,同时保持了低Vπ和宽带宽。在数据传输环境下,我们的铜基调制器与其他低电阻但较不常见的金属制造的调制器实现了相同的性能。它们依赖于半导体行业广泛使用的金属沉积工艺,这进一步增强了部署下一代电光PIC的共封装光学器件的前景。

方法

铜Damascene制造流程。

首先,通过等离子体增强化学气相沉积(PECVD)将TFLT PICs包覆一层2.5 µm厚的二氧化硅层。这个包覆层将嵌入随后形成的铜电极。这些电极的布局通过深紫外光步进光刻(ASML PAS 5500/350C)定义,并通过氟基干法蚀刻转移到包覆层中。这些预成型结构经过10 nm的钛(Ti)和100 nm的铜(Cu)溅射沉积(Alliance-Concept DP 650)。钛层作为阻隔层,防止铜扩散到周围的电介质中[37],并为随后溅射的铜层提供附着力,铜层作为种子层促进铜电镀。电镀在Silicet电镀单元中进行,铜层厚度为2.8 µm,具有低电阻率(2.04 µΩ·cm)。化学机械平坦化(CMP)用于去除多余的铜,只留下蚀刻的预成型结构中的铜,最终铜层厚度为1.8 µm。随后,通过PECVD沉积100 nm厚的氮化硅钝化层,以防止铜的氧化。然后打开电极垫,并用金(Au)覆盖,以实现高效稳定的电气探针。最后,通过干法蚀刻——标准的反应离子蚀刻用于LT和二氧化硅,深反应离子蚀刻用于硅——和背面磨削实现芯片切割。此工艺确保了平滑的面,用于与单模光纤的边缘耦合。

作者:Mengxin Lin,1, 2 Zihan Li,1, 2 Alexander Kotz,3 Hugo Larocque,1, 2Johann Riemensberger,1, 2 Christian Koos,3and Tobias J. Kippenberg1, 2, ∗

单位:1Institute of Physics, Swiss Federal Institute of Technology, Lausanne (EPFL), CH-1015 Lausanne, Switzerland

2Institute of Electrical and Micro Engineering (IEM), EPFL, CH-1015 Lausanne, Switzerland

3Institute of Photonics and Quantum Electronics (IPQ),

Karlsruhe Institute of Technology (KIT), 76131 Karlsruhe, Germany