二阶非线性光学过程在研究和工业领域有着广泛的应用。然而,大多数可用的二阶非线性器件依赖于二阶非线性度较低的块体非线性晶体。利用集成光学领域的进步,具有较大二阶非线性度的材料可以低成本地实现高效、小尺寸的片上非线性器件。然而,主要用于光子集成电路的硅和氮化硅的二阶非线性度(χ(2))可忽略不计,因此必须研究替代材料。具有高二阶非线性度的锆钛酸铅 (PZT) 薄膜是片上非线性器件的良好候选材料。本文展示了在玻璃基板上生长的 PZT 薄膜中电场诱导的 χ(2) 调谐,调谐效率为 3.35 pm V−2。记录到强烈的二次谐波产生,并报告了非常高的主导张量分量 χ(2) 为 128 pm V−1。PZT 薄膜的 χ(2) 可以通过在室温下用直流电场极化来反转。这为高效、可调谐的片上非线性器件开辟了道路。

#划重点

#PZTOI晶圆 #PZT电光调制器光刻显影刻蚀流片

#6寸DUVKRF150nm晶圆级流片

引言

二阶非线性光学效应,如二次谐波产生(SHG)、参量下转换和差频生成,在超快光学光谱学、[1] 谐波生成显微镜学、[2] 量子计算[3]等应用和领域中取得了显著进展。倍频激光器[4]、光学参量振荡器[6]、放大器[8] 和太赫兹辐射源[9] 都是依赖于二阶非线性效应的有用设备的例子。此外,除了基于χ(2)的光生成功能外,基于波克尔效应的电光调制器[10] 是我们通信世界中的关键设备。然而,这些设备大多数仍然昂贵且依赖于体积庞大的非线性晶体。

集成光学使得光子集成电路(PICs)变得更小、更节能,并且可以低成本大规模生产。通过集成上述非线性设备,可以极大地提高这些PICs的复杂性和功能。例如,通过利用硅(Si)和氮化硅(SiN)的三阶非线性,已经证明了用于量子随机数生成[11]、波长转换器[12] 和频率梳生成[13]的PICs。与三阶非线性相比,二阶非线性更强,并且需要较低的功率。不幸的是,硅具有中心对称结构,因此不支持二阶非线性过程。然而,通过使用SiN薄膜在Si波导中引入应变场,或通过在Si脊波导中施加直流电场,可以分别在SHG实验中测量到2.3 µm处的χ(2)为40 pm V^(-1) 和2.29 µm处的41 pm V^(-1) [14]。然而,获得这些χ(2)值的复杂性仍然是一个问题。在使用等离子体增强化学气相沉积(PECVD)法沉积的SiN薄膜中,使用SHG实验发现,在1064 nm处,χ(2)zzz值(z方向垂直于薄膜平面)高达5 pm V^(-1)[16]。然而,与大多数非线性晶体相比,获得的χ(2)值仍然较低。

因此,已经研究了将非线性晶体的薄膜集成到Si或SiN上的异质集成(heterogeneous integration)作为实现片上光学非线性设备的一种尝试。这些薄膜应具有较大的二阶非线性和高的光学质量。钽酸锂(LiNbO3)晶体是非线性光学领域的黄金标准,因其已确立的非线性特性而成为这种集成的主要材料。它们已经广泛用于电光调制器作为波克尔效应的基础,在电信行业中应用,并且通过SHG实验也研究了其χ(2)系数[17],其中在1064 nm处,χ(2)zzz = -54 pm V^(-1) 是报道的最大系数[18]。最近,已经报道了在周期性极化或纳米图案化的LiNbO3波导上实现片上SHG,这些波导与Si或SiO2结合[19]。在钛酸钡(BaTiO3)薄膜中也已演示SHG[24],在Ce:BaTiO3:SrTiO3超晶格中,测量到在1064 nm处应力诱导增强的χ(2)zzz = 152 pm V^(-1)[24]。然而,LiNbO3和BaTiO3薄膜的异质集成需要额外的粘接程序,而且BaTiO3薄膜的光学损耗较高(6 dB cm^(-1))[27]。非线性有机晶体如4-N,N-二甲氨基-4'-N'-甲基-斯蒂尔巴佐铵托烷酸盐(DAST)或N-苄基-2-甲基-4-硝基苯胺(BNA)也被用于强二次谐波生成,分别具有χ(2)值高达χ(2)xxx = 580 pm V^(-1) 在1542 nm处和χ(2)zzz = 468 pm V^(-1) 在1064 nm处[28]。在1550 nm处进行的SHG测量揭示,在BNA晶体中χ(2)zzz = 160 pm V^(-1)[30],在BNA薄膜中χ(2)zzz = 153 ± 70 pm V^(-1)[31]。尽管这些有机晶体报告了非常高的χ(2)值,但生长具有高光学质量的有机晶体薄膜的挑战对于实现高效的片上非线性仍然是一个问题。

在铁电氧化物中,钛酸铅锆(PZT)因其出色的铁电性和压电性特征,被广泛应用于微型压电传感器和执行器、微机电系统(MEMS)、声学传感器和非易失性随机存取存储器(NVRAMs)中。[32] PZT的较大透明窗口[35]和光学非线性[36]使其成为片上非线性设备的理想材料。已经报道了一种新颖的方法,将具有优异电气和光学性能的PZT薄膜集成到不同基底上。[37] 该方法使用基于镧系元素的中间低损耗层作为PZT沉积的种子层,而不是传统上使用的高吸收金属种子层,从而能够直接将薄膜沉积在Si或SiN波导的顶部。通过这种方法,已经成功地在SiN[38]和Si[39]波导上生长了具有强波克尔效应的PZT薄膜,并报告了额外损耗小于1 dB cm^(-1)的高速电光调制。虽然SHG已被用于探测铁电PZT薄膜,[40] 但尚未报告任何χ(2)值。然而,从PZT薄膜中测得的大波克尔系数(≈250 pm V^(-1))[37]表明,测量χ(2)值以探讨SHG的可能性。本文中,我们展示了在玻璃基底上通过化学溶液沉积法生长的PZT薄膜中的强SHG。我们从SHG测量中提取出非常大的二阶光学非线性易感性分量,并研究了极化对PZT薄膜非线性响应的影响。我们证明,通过在PZT薄膜上施加电场,二阶非线性分量可以被调节并反转。所得结果在多个样品中一致。

实验部分

PZT薄膜通过化学溶液沉积(CSD)方法生长在玻璃基底上的氧化铟锡(ITO)层上,使用镧系元素为基础的中间层作为种子层,如George及其同事所报道。[37] 该中间层既充当防止铅(Pb)扩散的屏障层,又作为PZT生长的种子层。使用Corning玻璃基底(CB-90IN,Delta Technologies),厚度为1.1 µm,表面涂覆一层20 nm厚的ITO层,作为透明的底电极(片电阻70-100 Ω sq^(-1))。然后沉积10 nm厚的基于镧系元素的中间层,接着是PZT薄膜的沉积。中间层和PZT薄膜都通过反复旋涂和退火过程沉积,这可以控制薄膜的厚度。我们采用化学组成PbZr0.52Ti0.48O3来制作PZT薄膜。PZT层在620°C下退火15分钟,使用氧气氛围在管式炉中处理。然后,最后在样品上沉积圆形(1 mm半径)ITO电极作为顶电极。通过超声焊接方式在PZT薄膜中制作通孔,以便与底部ITO电极接触。我们制作了三种不同厚度的样品,分别为PZT厚度871.9 nm(S1)、885 nm(S2)和920.7 nm(S3)。通过光谱椭圆偏振法测量薄膜的厚度。

图 1. A) 样品示意图及光束轨迹。基频 ω 的光(红色)激发样品,测量出射的二倍频 2ω 光(蓝色)。PZT 薄膜沿 z 方向极化(底部图片)。黑点为钛离子或锆离子,其位置决定了薄膜的偏振密度。B) 用于二次谐波 (SHG) 测量的装置。样品安装在旋转台上,并固定在 70° 入射角。使用电动台上的半波片旋转基频光的偏振,并测量 s 或 p 偏振二倍频光随偏振角的变化。偏振分束立方体 (PBSC)、长通滤光片 (LP)、短通滤光片 (SP)、带通滤光片 (BP)。

对于SHG表征,我们采用Hermans等人[41]报道的测量技术。图1b显示了用于SHG测量的设备设置。光源为一台模式锁定激光器(Calmar FPL-03CCFPM),发射波长为1550 nm的0.1 ps脉冲,重复率为20 MHz,平均功率为12 mW。使用偏振光束分离立方体(PBSC)确保准直光束的线偏振(光束直径为3 mm(1/e^2))。使用半波片在测量过程中旋转线性偏振光的偏振方向。半波片由电动舞台控制,允许进行依赖于偏振角度的测量。使用两个焦距为5 cm的抛物镜将激光束聚焦到样品上,并在样品后重新准直。聚焦光斑在样品上的直径(1/e^2)为30 µm。这为我们提供了1 mm的对焦深度,便于样品在焦平面内对准,且峰值强度约为176 MW cm^(-2)。在样品前方放置长通滤光片,以滤除样品前产生的任何寄生SH光,而在样品后方放置短通滤光片,抑制基本波长的激光光并仅允许SH光通过。样品放置在一个电动旋转舞台上,允许设置入射角度。在检测器前方放置第二个PBSC作为分析器,允许s-或p-(分别对应0°和90°)偏振的SH光通过。生成的SH光通过硅雪崩单光子探测器(ID120,ID Quantique)捕捉。在测量过程中,入射角度保持固定,通过旋转半波片调节基本光束的偏振状态。然后记录s-和p-偏振的SH功率,并作为偏振角度的函数进行分析。通过使用已知二阶非线性材料(β-硼酸钡(BBO)晶体)的Maker条纹测量法[41]来校准设备(参见支持信息中的图S2,查看测量和拟合结果)。在1550 nm波长下,BBO的非线性易感性值为χ(2)xxz = -0.057 pm V^(-1),χ(2)yyy = 4.162 pm V^(-1),χ(2)zx = -0.076 pm V^(-1),χ(2)zzz = -0.077 pm V^(-1)。BBO晶体(来自Eksma Optics)与熔融石英光学接触,尺寸为10 mm × 10 mm × 0.065 mm,晶体角度θ = 20.2°,φ = 90°。在PZT样品的χ(2)测量前后进行校准,以避免激光和光学设备波动的影响。

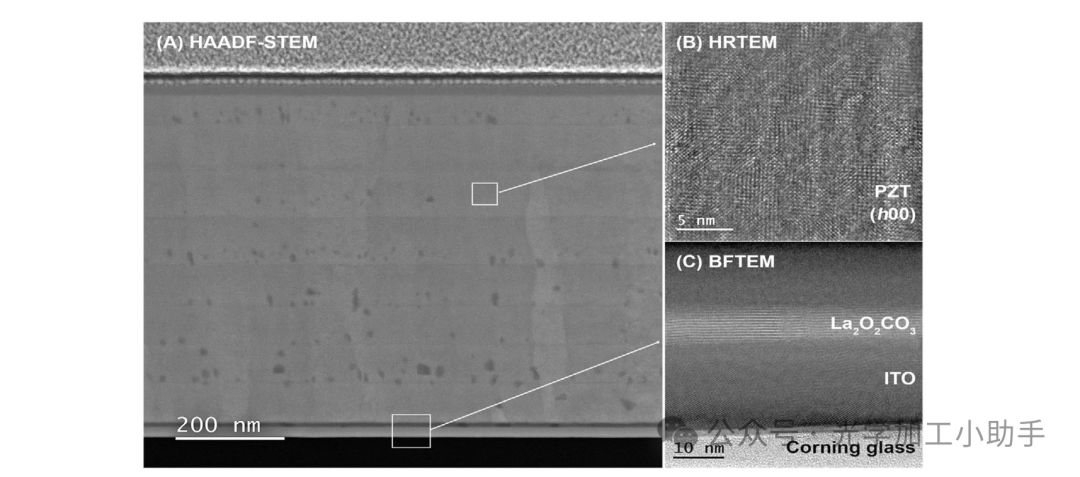

图 2. A) 在 ITO/康宁玻璃上沉积的镧系中间层上生长的 PZT 薄膜的扫描透射电子显微镜 (STEM) 图像。B) 生长的 PZT 薄膜的高分辨率 (HR) TEM 图像;C) ITO 上镧系中间层的明场 (BF) TEM 图像。

图 3. A) 使用镧系中间层在玻璃基底上生长的 PZT 薄膜的 XRD 谱图。B) 未经极化的样品 S1 和 S2 的 p(圆形)和 s(三角形)极化 SH 功率及其相应的拟合曲线,该曲线与极化角的关系。非零响应证实了生长后对称性破缺。为了更清晰地显示,s 极化 SH 功率的数据和拟合曲线乘以 10。

生长后,PZT薄膜为多晶材料,铁电畴优先沿(100)晶面取向,这可以通过透射电子显微镜(TEM,图2a)和X射线衍射(XRD,图3a)测量观察到。图2c和XRD图谱显示,基于镧系元素的中间层具有强烈的优选生长,c轴垂直于基底。这导致PZT薄膜沿c轴取向生长(图2b)。[37] 基于横截面微观结构的研究,PZT薄膜从基于镧系元素的中间层异质结晶,形成了柱状钙钛矿相(晶粒尺寸在40到110 nm之间),并且形成了一些次生相(图2a中的黑点)。基于镧系元素的中间层,其成分为La2O2CO3,既充当防止铅扩散的屏障层,又作为PZT生长的种子层。为了评估中间层作为屏障层的质量,获取了元素分布图(见支持信息中的图S3)。未观察到铅从PZT薄膜扩散到基底,表明La2O2CO3薄层作为有效的缓冲层起到了作用。PZT薄膜具有随机的面内取向[37],因此相对于法线具有C∞v对称性,因此其非零的二阶易感性张量分量为χ(2)xxz = χ(2)yyz = χ(2)xz = χ(2)zy = χ(2)zx = χ(2)yy 和χ(2)zzz,其中z是薄膜的法线方向,x和y是两个正交的面内方向(图1a)。[42] 这里计算的二阶易感性张量分量的值是有效(平均)值,来源于PZT薄膜中不同畴的累积响应。为了探测不同的张量分量,在测量过程中入射角设定为70°。测量并拟合s-和p-偏振的SH功率,以提取张量分量。测量数据被拟合到Bethune所描述的模型中[43],该模型考虑了薄膜中的反射(关于模型和拟合函数的详细信息见支持信息)。该模型基于光学传输矩阵的形式。在输入中,我们使用不同层的厚度和折射率,并拟合未知的χ(2)系数。我们忽略了厚玻璃基底中的弱反射以及基底背面玻璃-空气界面上的弱SH贡献。[41]

结果与讨论

首先,在没有极化处理的情况下对样品S1和S2进行了测量。图3b显示了s-(三角形)和p-(圆圈)偏振SH功率的独立测量结果,以及作为φ的函数的相应拟合模型(线)。良好的拟合结果表明C∞v对称性是假设是有效的。结果显示出非零响应,表明在PZT薄膜生长过程中发生了对称性破缺。铁电畴不仅在生长后具有优先的(100)面外取向,而且铁电畴的偶极子取向也不均匀地指向或背离基底,且两个方向中的一个占主导地位。PZT薄膜中的极化密度在不同样品之间有所不同,这解释了图3b中样品S1和S2之间观察到的差异。

为了最大化非线性响应,对样品进行了常温和常压下的极化处理,通过在PZT薄膜上施加直流电场来实现,使用ITO电极进行操作。我们进行了一个实验,其中样品被p-偏振光激发,并记录了施加直流偏压下PZT薄膜产生的p-偏振SH功率。图4展示了生成的SH功率,呈现出类似蝴蝶的滞后行为。这证实了沉积的PZT层的铁电性质,并表明铁电畴在施加的直流电场作用下发生了重新排列。图中还可以看到轻微的不对称性,因为在-15V施加电压时记录的SH值高于+15V时的值。这一轻微差异再次表明铁电畴在生长方向上有优先取向,即朝向上方。

图 4. 三角形直流偏压下 SHG 功率的变化。从 0 V 开始,我们施加直流偏压,曲线如图所示,依次为蓝色、灰色和红色。A) 从 0 V 开始,我们施加负偏压。B) 从 0 V 开始,我们施加正偏压。在直流偏压下,SH 功率观察到的蝴蝶形磁滞行为证实了畴的排列和 PZT 薄膜的铁电性质。

此外,在图4a中,我们观察到在负直流偏压下初始生成的SH功率增加,而在正直流偏压下减少(图4b),即电场线朝下,与极化密度相反。这证实了铁电畴在生长方向上优先排列,因为负偏压下电场线朝上,与极化密度方向一致,而正偏压则与极化密度相反。

图5. A) 极化过程中及极化后SH功率的时间依赖性测量。B) 经过-15V极化10分钟后,三种不同样品S1(蓝色)、S2(绿色)、S3(黄色)得到的p-(圆圈)和s-(三角形)偏振SH功率及相应的拟合曲线,作为极化角度的函数。C) 样品S3在三种偏压条件下的SHG功率;0V(蓝色)、-15V(绿色)、-20V(黄色)。为更好地显示,s偏振SH功率的数据和拟合结果乘以10。D) 随着偏压电压增加,χ(2)zzz的演变,包括线性拟合。数据(蓝色点),拟合(虚线)。

施加电压后,SH功率随时间变化不大。当释放施加的电压时,SH功率会下降至较低的值,然后在较长时间内保持稳定(图5a)。该测量还进行了多次循环(见支持信息中的图S4)。SH功率在有无电压的增加和下降分别归因于薄膜中的畴反转。图5b显示了在施加-15V偏压处理10分钟后的三种样品的s-和p-偏振SH功率的独立测量结果,并拟合了相应的模型作为φ的函数。测量是在没有直流偏压的情况下进行的,样品S1、S2和S3分别得到了χ(2)zzz为61.1、60.2和59.6 pm V^(-1)的值。无论极化方向如何,得到的χ(2)zzz值都相似。χ(2)zzz值的相似性和滞后测量表明,尽管这里只提取了SHG的二阶易感性张量分量的绝对值,但这些张量元素的符号可以通过偏压电压进行反转。这为使用施加电场进行按需畴工程开辟了道路。通过仔细的电极设计,周期性极化以实现PZT薄膜的准相位匹配应该是可行的。因此,与模式相位匹配技术(其中SH在较高阶模中生成,并需要通过模式转换器转换回)相比,这将导致更高的转换效率。此外,我们的PZT薄膜的极化不需要复杂的过程和高电压,这与制造周期性极化的钽酸锂(PPLN)薄膜所使用的电压相比要简单得多。图5c显示了在三种不同偏压(0、-15和-20 V)下,从样品S3获得的s-和p-偏振SH功率的测量结果及其相应的拟合模型作为φ的函数。类似的结果也在入射角设置为65°时获得(见支持信息中的图S5)。图5d中绘制了有效的χ(2)zzz与施加的偏压电压的关系图,从中可以观察到随着偏压电压的增加,χ(2)zzz呈线性增加。在-20V偏压下,得到的调谐效率为-3.35 pm V^(-2),有效的χ(2)zzz为128 pm V^(-1)。下面的表1总结了对三个样品平均提取的张量分量。 在电场作用下,二阶极化可以通过以下公式描述:

在电场存在的情况下,二阶极化可以用以下公式来描述

表1. 不同偏压条件下三个不同样品的PZT薄膜二阶磁化率张量分量的平均绝对校准值及相应的标准差。

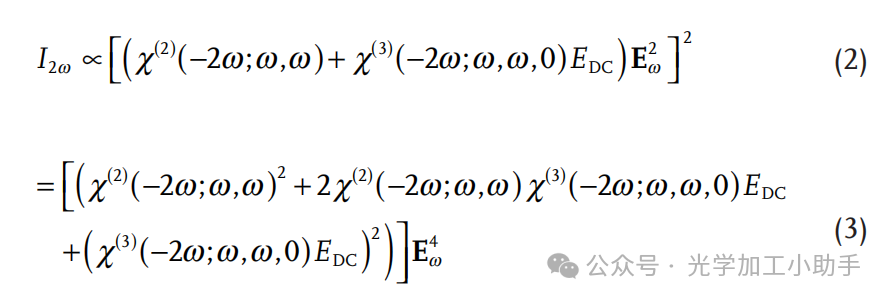

这种极化产生的 SHG 强度可以用以下公式描述:

带有χ(3)(−2w; w, w, 0)EDC描述的场依赖效应被称为电场诱导二次谐波生成(EFISH)。[48]

EFISH是一个瞬时的三阶非线性效应,源自频率为ω的两个光子与外部低频偏压之间的相互作用。在具有反演对称性的材料中,二阶易感性为零,因此仅剩下EFISH贡献。[49]

因此,在没有反演对称性的材料中,在直流偏压下测得的SHG功率是二阶χ(2) SHG过程、EFISH以及这两种效应之间的耦合所产生的结果,该耦合由方程(2)中的项χ(2)(−2w; w, w)χ(3)(−2w; w, w, 0)EDC描述。[50]

这些不同效应对场依赖性测量的贡献尚不明确。我们试图阐明主要效应。首先,图4中直流偏压下的SHG滞后行为与PZT薄膜中铁电畴的翻转有关。畴翻转改变了PZT薄膜中的有效χ(2),无论是符号还是幅度。当更多的畴沿直流电场方向对准时,得到更大的χ(2)值。然而,滞后行为不能排除EFISH贡献,因为耦合项也可以引起滞后。铁电畴的翻转和放松对SHG功率与直流电场的依赖性也有影响。SHG功率的拟合(见支持信息中的图S6)显示,在施加电场的绝对值较小(亚强制场)时,SHG功率呈二次依赖关系,这可能表明EFISH效应占主导地位。然而,对于较大绝对值的直流电场,SHG功率偏离了二次拟合,观察到与施加的直流电场之间的线性关系,这排除了EFISH的主导贡献。这在直流电场减小时的下降周期中得到了始终如一的观察。在直流电场减小的周期中,之前通过较大电场对准的铁电畴首先处于放松阶段,其中它们旋转到稳定的群体状态。由于不同晶粒的取向不完全沿垂直于基底的方向,可能发生旋转极化。最近有研究表明,极化旋转是PZT薄膜中的一个重要效应。[51] 随后,畴翻转发生在靠近强制场的直流电场作用下。我们假设,在滞后回线中这种状态的变化导致SHG功率偏离了与直流电场的二次依赖关系。因此,场依赖性测量中的主导效应似乎与畴翻转和重新定向以及有效的χ(2)变化有关。此外,Bao等人测量了铅钪钛酸铅(PLZT)中的EFISH响应上升时间为10 ps,[52] 并将场依赖性的二次谐波生成归因于对称性变化,而不是发生在飞秒时间尺度上的纯电子χ(3)(−2w; w, w, w)效应。虽然这并不完全排除EFISH在我们的测量中的贡献,但它进一步表明,观察到的SHG效应主要源于χ(2)贡献。

结论

总之,本文展示了通过化学溶液沉积法在玻璃基底上生长的PZT薄膜中的强SHG。使用薄且低损耗的镧系元素层作为种子层,并且PZT薄膜也可以像最近所示那样轻松与Si或SiN光子集成电路集成。[38] 我们能够确认PZT薄膜在生长后发生了对称性破缺,铁电畴优先沿生长方向排列。经过极化处理后,三种不同样品的一致测得的平均χ(2)zzz为60 pm V^(-1)。这些样品在常温和常压下进行了极化处理。我们展示了通过电场诱导的χ(2)调节。通过-20V偏压测得的有效χ(2)zzz为128 pm V^(-1),调谐效率为-3.35 pm V^(-2),这是LiNbO3的χ(2)zzz的两倍。极化测量还揭示了χ(2)张量分量随直流偏压的可逆性。这是首次报告在非线性薄膜中进行这种χ(2)调节和可逆性的研究。我们的PZT薄膜因此被定位为薄膜和集成光学中新功能的理想候选材料,如片上光学参量振荡器、频率梳发生器[44]、太赫兹源[45]、量子源[46]和频率转换器[47]。

作者;Gilles F. Feutmba, Artur Hermans, John P. George, Hannes Rijckaert, Irfan Ansari, Dries Van Thourhout, and Jeroen Beeckman*

单位;Ghent University