#薄膜铌酸锂晶圆 #薄膜钽酸锂晶圆 #铌酸锂电光调制器 #铌酸锂微波光电转换 #高速电光调制

摘要:薄膜铌酸锂绝缘体(LNOI)已成为非线性集成光子器件的重要平台,类似于绝缘体上硅(SOI)在电子器件中的影响。然而,尽管 LNOI 与 SOI 具有相似的硅/氧化物界面结构,其界面电荷对射频(RF)损耗的作用却鲜有研究。本文揭示了 LNOI 平台中硅/氧化物界面处的可移动电荷所导致的寄生导电效应,并发现该效应在等离子体刻蚀过程中会显著增强,从而引起较大的 RF 损耗。通过在界面引入富陷阱多晶硅层,我们有效抑制了寄生导电并显著降低了 RF 损耗。本研究为 LNOI 在高频电机耦合器件、高速电光调制器及高效微波-光转换器等应用中的发展提供了关键设计指导。

#0:10mm-10mmsto衬底-bto薄膜(300nm厚度可定制)

#1:sto外延片

2寸 外延 sto 2-20nm(可定制)- 2um Sio2(可定制) -Si(可定制)

#2:a向 bto外延片

2寸 外延 a-向 bto(300nm或者500nm,或者定制)-sto 8nm(可定制)- 2um Sio2(可定制) -Si(可定制)

#3:C向 bto外延片

2寸 外延 c-向 bto(150nm或者300nm,或者定制)-sto 8nm(可定制)- 2um Sio2(可定制) -Si(可定制)

#离子注入铒代工

#6寸DUV步进式光刻代工,最小线宽180nm,超高性价比,可以只曝光

#快速氮化硅硅光铌酸锂流片 #高性价比 #低成本

#提供8寸 8umSiO2热氧片,6寸15um热氧片 10um热氧片 8寸10um热氧片

室温低损伤@GCIB抛光代工@束斑小(4-5mm)更均匀

#降低硬质材料化合物晶圆等绝大多数材料的表面粗糙度,比如金刚石 ,磷化铟,砷化镓,碳化硅

#提高复合衬底和镀膜膜层的器件层膜厚均匀性,

比如SOI LNOI LTOI SICOI 等 SMARTCUT得到的薄膜

或者镀膜所得到的膜层 ,比如镀了一层氮化硅,但是由于是cvd镀膜所得到的,表面的膜厚精度很差,粗糙度很差,可以通过粗糙度初步降低粗糙度,然后通过GCIB团簇离子束抛光来修整整面的膜厚均匀性 到0.5%以下举例:

未经过Trimming 工艺的 6寸LN/LTOI晶圆 数据:

Range:100-200A

经过Trimming 工艺的 6寸LN/LTOI晶圆 数据:

Range:60A以内

SOI晶圆:--220nm薄膜/ 3um厚膜-3umSIO2-675umALOOI晶圆;--氧化铝薄膜晶圆,键合工艺和镀膜工艺

TAOOI晶圆--氧化钽薄膜晶圆,镀膜工艺

SINOI晶圆--超低损耗氮化硅薄膜晶圆,210nm-300nm-400nm-800nm

SICOI晶圆;新型量子光学平台500nm-700nm-1um

8寸LTOI晶圆批量供应;铌酸锂的有力的竞争对手,薄膜钽酸锂晶300600

8寸LNOI晶圆;8寸LNOI助力更大规模薄膜铌酸锂产品量产

LN/LT-SOI/Si/SIN W2W&D2W异质集成

流片: 6寸 氮化硅 铌酸锂 硅光 超高性价比流片, 1个BLOCK的价格买一整片晶圆

划重点--全国产-超高性价比-6 寸硅光-氮化硅-铌酸锂流片白皮书

我们为客户提供晶圆(硅晶圆,玻璃晶圆,SOI晶圆,GaAs,蓝宝石,碳化硅(导电,非绝缘),Ga2O3,金刚石,GaN(外延片/衬底)),镀膜(PVD,cvd,Ald,PLD)和材料(Au Cu Ag Pt Al Cr Ti Ni Sio2 Tio2 Ti3O5,Ta2O5,ZrO2,TiN,ALN,ZnO,HfO2。。更多材料),键合(石英石英键合,蓝宝石蓝宝石键合)光刻,高精度掩模版,外延,掺杂,电子束光刻等产品及加工服务(请找小编领取我们晶圆标品库存列表,为您的科学实验加速。

请联系小编免费获取原文

文章名:Parasitic conduction loss of lithium niobate on insulator platform作者:Mohan Shen,a) Likai Yang,a) Yuntao Xu, and Hong X. Tangb)单位:Department of Electrical Engineering, Yale University, New Haven, CT 06511, USA薄膜铌酸锂绝缘体(LNOI)结构是在低折射率的二氧化硅(SiO₂)层上引入铌酸锂(LN),从而实现了高光学约束和紧凑的光子电路设计¹,²。结合 LN 的大电光、声光及压电系数,LNOI 平台在电光调制器³–⁵、量子换能器⁶–⁹、电机耦合谐振器¹⁰,¹¹,以及片上二次谐波与光频梳产生¹²等方面带来了显著性能提升。在 LNOI 的实现中,可采用不同材料作为衬底,包括体 LN、石英以及硅(Si)¹³。其中,以硅作为衬底的 LNOI(见图 1a)因其低成本及与硅基工艺的兼容性而成为最常用的选择。然而,基于 Si 衬底 LNOI 的许多应用受制于射频(RF)损耗,这一关键因素限制了电光调制器的带宽⁵、微波-光量子换能器的效率⁶,以及基于电机耦合谐振器的微波滤波器的插入损耗与带宽¹⁴。

图 1. LNOI 薄膜中的陷阱与可移动电荷示意图及 Si/SiO₂ 界面的能带图。

a, 上图展示了制备后的 LNOI 材料堆叠结构,下图为其对应的能带结构。

b, 氩等离子体刻蚀过程在埋氧层中引入固定电荷,使 Si/SiO₂ 界面进入反型区,在界面处形成一层自由载流子,如下图所示。

c, 在界面插入富陷阱的多晶硅层能够抑制自由载流子的形成,从而降低射频(RF)损耗。

d, 倒装键合示意图:在蓝宝石衬底上的 NbN 超导谐振器被倒装键合至 LNOI 芯片上。

e, 倒装键合芯片的截面图。PSC 层处于微波谐振器电场中,并影响谐振器的 Q 因数。

在研究 Si 衬底 LNOI 的 RF 损耗时,人们大多关注于金属的欧姆损耗⁵以及 LN 的压电机械损耗⁷,⁸。然而,LNOI 中还存在一种重要但常被忽视的损耗机制,即 寄生表面导电(PSC)损耗¹⁵,¹⁶,且在制程过程中会被增强,例如等离子体辐射。等离子体辐射会产生从真空紫外(VUV)到 X 射线的辐射¹⁷,¹⁸,导致 SiO₂ 层内的正固定电荷增加,并在 Si/SiO₂ 界面处产生缺陷态¹⁹,²⁰。这些增强的正电荷会对 Si/SiO₂ 结构产生偏置,从而吸引自由载流子在界面处聚集。累积的自由载流子降低了电阻率并引起微波损耗²¹。图 1a,b 展示了 PSC 的形成过程及相应的能带结构图。由于氩等离子体刻蚀 LN 是当前 LNOI 图形化的标准工艺¹,²²,因此这一损耗机制对 LNOI 尤为重要。在刻蚀设备中,LNOI 芯片会直接暴露于等离子体辐射下。

近期一项关于 LN-on-Si 平台表面声波(SAW)的研究表明,PSC 效应会导致 SAW 器件能量泄漏²³。同样地,PSC 也会引起微波器件的能量损耗。在许多基于 LNOI 的微波应用中,人们极力追求高品质因数(Q 因数)的微波谐振器,例如微波-光量子换能⁶–⁸和微波与固态自旋之间的强耦合²⁴。但这些器件也最易受到微波损耗的影响。另一方面,超导谐振器对 RF 损耗高度敏感,使其成为表征 LNOI 微波损耗的理想工具。基于这一优势,我们利用超导谐振器通过倒装键合和直接在 LNOI 芯片上制备谐振器的方法来测量 LNOI 的 RF 损耗。图 1d,e 展示了倒装键合方案。PSC 层在微波谐振器电场中的存在可通过 Q 因数的变化加以揭示。

本文在低温条件下,利用超导谐振器研究了氩等离子体辐射诱发的 PSC 损耗。从未加工的 LNOI 芯片出发,我们分步刻蚀 LN,并在每一步后通过倒装键合高 Q 超导谐振器来测量其 RF 损耗。结果表明,随着刻蚀时间延长和辐射暴露增加,RF 损耗显著增强。而当去除 SiO₂ 层、消除 Si/SiO₂ 界面后,RF 损耗也随之消失。此外,我们还证明,在 Si 衬底与埋氧 SiO₂ 层之间沉积一层薄的多晶硅(poly-Si)即可抑制该 RF 损耗。我们的研究确认了氩等离子体辐射在 Si/SiO₂ 界面诱发的 RF 损耗,并提供了一种有效的解决方案,该方法可广泛应用于基于 LNOI 的各类器件中。

我们首先在常规 LNOI 晶圆(NanoLN)上测试 PSC 损耗。如图 1a 所示,该晶圆由 600 nm 厚的 X-cut LN、2 µm 厚的热生长 SiO₂ 层以及 500 µm 厚的高电阻硅衬底组成。LN 的干法刻蚀采用纯氩气物理刻蚀工艺(Oxford Plasmalab ICP 100)。在 110 W 射频功率和 300 W ICP 功率下,刻蚀速率约为 20 nm/min。为了制备高 Q 超导谐振器以探测 RF 损耗,我们首先在蓝宝石衬底上通过原子层沉积(ALD)沉积 50 nm 厚的氮化铌(NbN)薄膜。随后利用电子束光刻(EBL)和反应离子刻蚀(RIE)相结合的方法将薄膜图案化为微波谐振器。接着将两块已图案化的芯片正面对准键合并置于铜封装中,其中布置了环形天线以电感耦合微波谐振器。最终,器件被安装在低温恒温器中并冷却至 4 K 以测量 Q 因数。

图 2. 氩等离子体辐射引起的 RF 损耗。

a, LNOI 测试芯片的工艺流程。从未加工的 600 nm X-cut LNOI 芯片开始,首先通过氩等离子体干法刻蚀将顶层 LN 薄膜刻蚀至 380 nm。第二次刻蚀进一步将 LN 薄膜减薄至 100 nm。最后一次刻蚀完全去除 LN。完全刻蚀后,再通过 BOE 去除 SiO₂。

b, 各工艺步骤后的微波共振谱测量结果。对于未加工芯片,测得的本征 Q 因数为 4800。经过第一次氩等离子体刻蚀后,本征 Q 因数下降至 550。经过第二次及完全刻蚀后,Q 因数过低,谱中不再出现明显的共振信号。当 SiO₂ 被去除后,微波共振恢复,本征 Q 因数达到 6000。

倒装键合方法允许我们在同一块 LNOI 样品上连续进行刻蚀,并用同一个微波谐振器测量其损耗。从未加工的 LNOI 芯片开始,键合后的谐振器本征 Q 因数约为 4800,如图 2b i) 所示。经过初始测试后,LNOI 芯片被刻蚀至 380 nm 厚,并再次进行测量,其共振谱如图 2b ii) 所示。经过 11 分钟刻蚀后,谐振器的本征 Q 因数降至 550,约下降了 9 倍。当 LNOI 芯片进一步刻蚀至 100 nm 厚甚至完全刻蚀时,Q 因数过低,谱中不再出现明显共振。为了进一步确认 RF 损耗源自 Si/SiO₂ 界面,我们使用缓冲氧化物刻蚀液(BOE)去除 SiO₂ 层,从而消除 Si/SiO₂ 界面,如图 2b v) 所示。在这种情况下,微波共振恢复,本征 Q 因数测得为 6000。这些结果表明,随着刻蚀时间延长和辐射暴露增加,RF 损耗显著增强,与 SOI 上的研究结果一致¹⁹,²⁰。

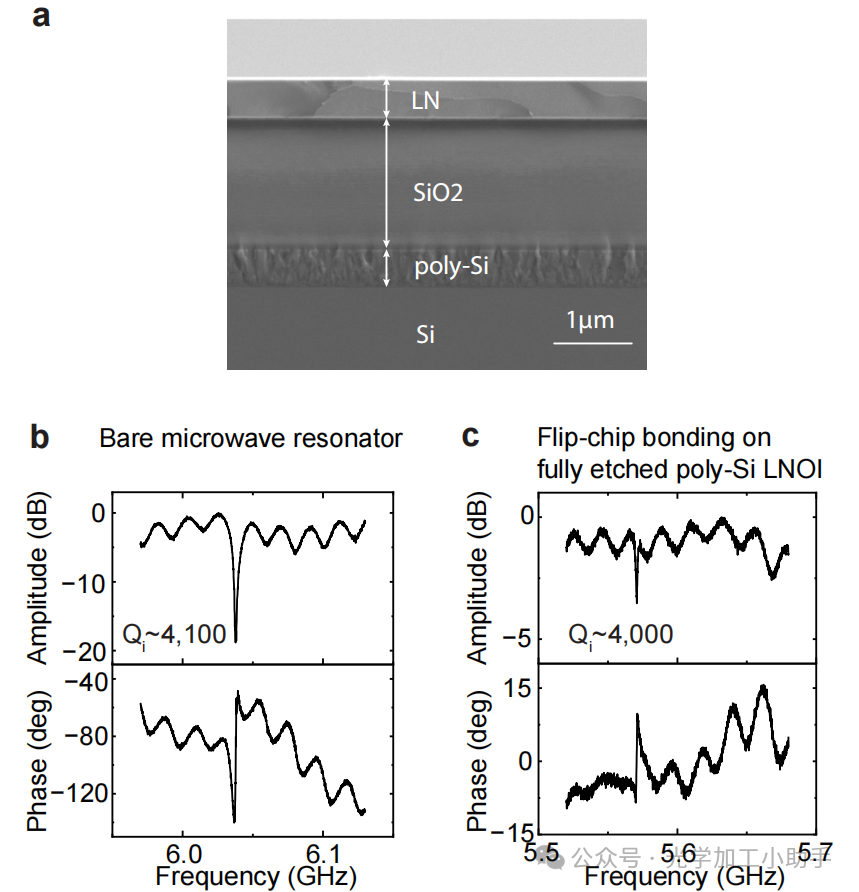

降低 PSC 损耗的一种常用策略是表面钝化²⁵。通过在 Si/SiO₂ 界面引入富陷阱层,自由载流子被俘获,从而降低导电性并减少 RF 损耗,如图 1c 示意所示。已有多种方法实现这一目的,包括在高电阻硅表面沉积非晶硅(α-Si)²⁶ 或多晶硅(poly-Si)²⁷,以及对硅衬底进行氩离子注入²⁸。这些方法均在硅中产生悬挂键,作为载流子陷阱。为了验证表面钝化处理在 LNOI 中的有效性,我们设计了一种定制 LNOI 晶圆。在 500 µm 厚的高电阻硅衬底上,先沉积 500 nm 厚的多晶硅层,再通过等离子体增强化学气相沉积(PECVD)沉积 2 µm 厚的 SiO₂,最后在其上键合 600 nm 厚的 LN 薄膜。该定制晶圆由 NanoLN 制备,其横截面的扫描电子显微镜(SEM)图像如图 3a 所示。

图 3. poly-Si LNOI 上的 PSC 损耗。

a, poly-Si LNOI 晶圆的截面示意图:在 Si 衬底上沉积 500 nm 厚的 poly-Si 层,其上沉积 2 µm 厚的 SiO₂ 层,再在 SiO₂ 上键合 600 nm 厚的 LN。

b, 裸微波谐振器芯片的微波共振谱测量结果,其本征 Q 因数约为 4100。

c, 与完全刻蚀的 poly-Si LNOI 芯片键合后的微波共振谱测量结果。微波谐振器仍保持约 4000 的高 Q 因数。

d–e, 直接在完全刻蚀的 poly-Si LNOI 与常规 LNOI 上制备的谐振器的微波共振谱。poly-Si LNOI 上的 Q 因数约为 1300,而在常规 LNOI 上未观察到明显的共振。

在 poly-Si LNOI 晶圆上,我们进行了与常规 LNOI 相同的倒装键合测试。首先对裸超导微波谐振器器件进行表征,其测得的微波响应谱如图 3b 所示,本征 Q 因数约为 4100。随后将 poly-Si LNOI 芯片上的 600 nm LN 薄膜完全刻蚀,PECVD SiO₂ 层仍然保留(如图 2iv 所示)。在完全刻蚀后,芯片再次与谐振器芯片倒装键合,测得谐振器仍保持接近不变的高 Q 因数 4000,如图 3c 所示。这与常规 LNOI 的结果形成鲜明对比:在常规 LNOI 中,当仅刻蚀 220 nm 时,Q 因数就已显著下降至 550,而 poly-Si LNOI 即使在完全刻蚀后仍保持低微波损耗。

在电光与电机应用中,直接在 LNOI 上沉积超导体对于增强目标耦合强度是理想的方案。为验证这一情形,我们在经过工艺处理的 LNOI 芯片上直接制备微波谐振器。具体而言,选择两种 LNOI 薄膜:一种包含 poly-Si 层,另一种不含 poly-Si 层,二者均经过氩等离子体的完全刻蚀,随后作为 NbN 沉积的衬底(NbN 薄膜沉积在 SiO₂ 层上)。在 poly-Si LNOI 芯片上制备的谐振器测得结果如图 3d 所示,其本征 Q 因数为 1300。相比之下,在常规 LNOI 薄膜上未能观察到明显的共振(见图 3e),表明存在过量的 PSC 损耗。这些结果显示,引入中间的 poly-Si 层可显著提升对氩等离子体辐射的不敏感性,并降低微波损耗。

结论上,本文研究了氩等离子体辐射增强的 LNOI 上 PSC 损耗。通过与超导谐振器倒装键合,我们观察到随着氩等离子体辐射暴露时间的延长,RF 损耗增加;当去除 SiO₂ 层后,RF 损耗得到恢复。实验结果确认了氩等离子体辐射在 LNOI 的 Si/SiO₂ 界面诱发 PSC 损耗的存在。虽然测试是在低温条件下进行,但从定性角度看,PSC 效应在室温下同样存在²¹,²⁵,只要在 Si 界面施加电压偏置并形成导电层。从定量角度而言,损耗大小在低温与室温下可能不同,这是由于 Si 中电子迁移率的温度依赖性所致。在室温条件下,PSC 损耗可能并非决定性因素,因为金属欧姆损耗等其他损耗机制亦存在。然而,如果埋氧层中正电荷密度足够高,PSC 在原理上仍可能成为主导损耗因素,并导致微波能量泄漏¹⁶。我们还通过定制设计的 poly-Si LNOI 晶圆,实现了对 Si 表面进行钝化,从而实验性地验证了一种有效缓解 PSC 损耗的方法。尽管通过更换 Si 衬底为蓝宝石或石英等其他材料同样可以消除 PSC 损耗,但 Si 衬底上的 SiO₂ 在多个方面具有独特优势。在光子学应用中,SiO₂ 的折射率(电信波段下为 1.44)低于蓝宝石(1.76),从而能够为 LN 波导提供更好的模式约束。与绝缘体衬底相比,室温下 Si 的适度导电性在涉及电子束光刻和电子束显微镜的制程中提供了便利。在可扩展性方面,Si 也更具成本效益,并且能够更直接地与成熟的硅基半导体器件集成。因此,poly-Si LNOI 平台(以及其他采用类似表面钝化处理的方法,如 α-Si 或离子注入的 LNOI 平台)可作为传统 LNOI 的可行替代方案,显著降低 RF 损耗。这种损耗的降低有望提升多种集成器件的性能,并释放 LNOI 平台的全部潜力