#soi晶圆 #Cavitysoi晶圆 #FDSOI晶圆 #厚膜SOI晶圆 #热氧化硅片 #POWERSOI #毫米波芯片 #射频芯片 #硅量子比特 # #Gan-SOI晶圆 #氮化镓HEMT

摘要—我们展示了基于GaN-on-silicon-on-insulator (SOI)平台的高电压耗尽模式和增强模式(E模式)AlGaN/GaN高电子迁移率晶体管(HEMTs)。GaN-on-SOI晶圆采用金属有机化学气相沉积(MOCVD)技术,在p型(111)Si SOI衬底上生长GaN外延层,且衬底采用p型(100)Si支撑片。微拉曼光谱显著揭示了GaN外延层中应力的减小,这是由于SOI衬底的柔性特性所致。采用氟等离子体注入技术制造的E模式HEMTs具有高的开/关电流比(108−109)、较大的击穿电压(1471 V,浮动衬底)和低的导通电阻(3.92 mΩ·cm²)。

关键词—AlGaN/GaN高电子迁移率晶体管(HEMTs)、增强模式(E模式)、氟等离子体注入、GaN-on-silicon-on-insulator(SOI)、高电压。

#全国产SOI晶圆定制加工 #468寸50nm-15um热氧片

库存片:

220nmSI高阻-3umSIO2-675umSI 6寸8寸 用于薄硅硅光

3000nmSI高阻-3umSIO2-675umSI 6寸8寸 用于厚硅硅光

#尺寸4-8寸

#最小起订量1片

#热氧层厚度范围50nm-15um

#膜厚精度最高精度+-5nm

#厚膜SOI-减薄抛光工艺600nm到微米级,加离子束精修,超级高精度膜厚均匀性

#CavitySOI-带空腔SOI晶圆,光刻显影刻蚀键合制作SOI一条龙

#FDSOI -最薄顶层10nm,特殊工艺精修,粗糙度小,膜厚精度高

普通超薄:SMARTCUT+离子束精修

超级超薄:EPI+SMARTCUT+离子束精修

#超平硅片-TTV500nm

我们为客户提供晶圆(硅晶圆,玻璃晶圆,SOI晶圆,GaAs,蓝宝石,碳化硅(导电,非绝缘),Ga2O3,金刚石,GaN(外延片/衬底)),镀膜(PVD,cvd,Ald,PLD)和材料(Au Cu Ag Pt Al Cr Ti Ni Sio2 Tio2 Ti3O5,Ta2O5,ZrO2,TiN,ALN,ZnO,HfO2。。更多材料),键合(石英石英键合,蓝宝石蓝宝石键合)光刻,高精度掩模版,外延,掺杂,6寸DUVKRF电子束光刻等产品及加工服务(请找小编领取我们晶圆标品库存列表,为您的科学实验加速。

请联系小编免费获取原文

文章名:1.4-kV AlGaN/GaN HEMTs on a GaN-on-SOI Platform

作者:Qimeng Jiang, Cheng Liu, Yunyou Lu, and Kevin J. Chen, Senior Member, IEEE单位:Hong Kong University of Science and TechnologyI. 引言

基于硅基板制造的AlGaN/GaN高电子迁移率晶体管(HEMT)是高效能功率开关和集成电力转换器的有前景候选器件,原因在于硅晶圆具有优异的可扩展性以及有利的器件特性,包括高击穿电压、低导通电阻和高开关频率。为了实现GaN功率器件与门驱动电路的单片集成,已展示了一种GaN智能电源集成电路平台,可以在同一芯片上提供高电压组件(晶体管和整流器)以及外围的混合信号功能模块。另一种具有吸引力的方法是GaN HEMT与Si CMOS的异质集成,这种方法能够利用成熟的高集成密度Si CMOS技术。对于这种异质集成的主要挑战在于GaN外延生长更偏向(111)Si,而主流的CMOS技术是基于(100)Si基板开发的。已经报道了几种异质集成方案,包括晶圆键合、在(100)Si-SiO2-(111) Si硅绝缘体(SOI)晶圆上选择性分子束外延生长GaN和直接在(111)硅基板上集成CMOS。然而,需要注意的是,尚未在这些平台上报道过高电压的AlGaN/GaN HEMT。

稿件收到日期:2012年11月28日;修订日期:2012年12月18日;接受日期:2012年12月20日。出版日期:2013年1月14日;当前版本发布日期:2013年2月20日。本研究部分得到了香港研究资助局的支持,资助编号为611311和611512。本文的审稿由编辑J.A. del Alamo安排。

作者来自香港科技大学电子与计算机工程系,位于香港九龙(电子邮件:qmjiang@ust.hk;eekjchen@ust.hk)。

本文中的部分图形的彩色版本可在线查看,网址为:http://ieeexplore.ieee.org。

数字对象标识符:10.1109/LED.2012.2236637

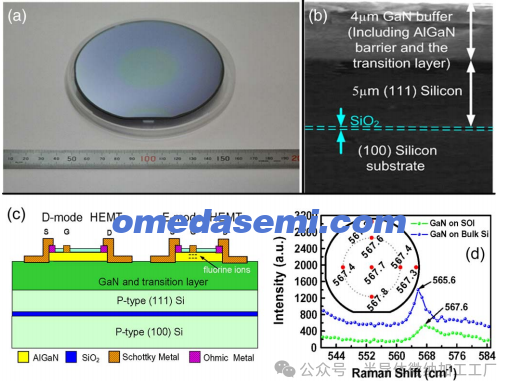

图1:(a)4英寸GaN-on-SOI晶圆的照片。(b)GaN-on-SOI晶圆的扫描电镜(SEM)截面图。(c)在GaN-on-SOI平台上制造的D型和E型HEMT的示意截面图。(d)GaN-on-SOI和GaN-on-Si(散装)晶圆的微拉曼光谱。(插图)GaN-on-SOI晶圆上E2峰的映射图。

在本文中,展示了在GaN-on-SOI平台上制造的高性能耗尽型(D型)和增强型(E型)高电压AlGaN/GaN HEMT,击穿电压超过1400V。GaN-on-SOI晶圆具有通过金属有机化学气相沉积(MOCVD)在p型(111)Si SOI基板上生长的GaN外延层,基板具有p型(100)Si承载晶圆。为了将来与Si CMOS的异质集成,可以通过去除顶部的材料,包括GaN、(111)Si和SiO2,选择性地暴露出与CMOS兼容的(100)硅。

II. GaN-ON-SOI晶圆和器件制造

本文中使用的4英寸AlGaN/GaN-on-SOI晶圆的照片和扫描电镜(SEM)截面图分别如图1(a)和(b)所示。4μm厚的AlGaN/GaN外延结构(包括30nm的Al0.25Ga0.75N障碍层、1μm的非故意掺杂GaN缓冲层和3μm的非故意掺杂过渡层)是通过MOCVD在4英寸SOI晶圆上生长的。SOI晶圆具有5μm的(111)p型Si层、0.2μm的SiO2层和600μm的p型(100)Si承载晶圆,且采用晶圆键合法制造。为了比较,同样的AlGaN/GaN外延结构也在4英寸的散装(625μm厚)p型(111)Si晶圆上生长。

有研究提出,SOI晶圆提供了一种柔性基板,有助于释放由于基板与外延层之间存在较大晶格失配所产生的应力。

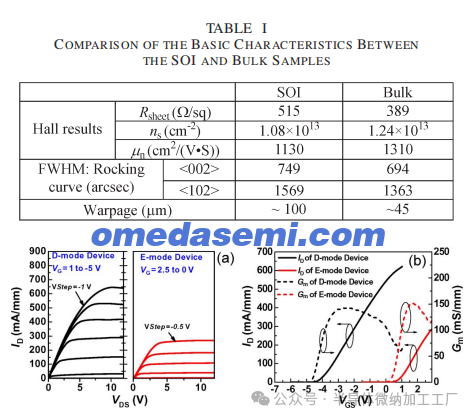

图2. GaN-on-SOI晶圆上D型和E型器件的直流特性。(a)源-漏I-V特性(未钝化)。(b)线性刻度下的转移特性(未钝化)。这些器件的栅-漏距离为10 μm。

我们对GaN-on-SOI晶圆进行了微拉曼光谱测试,结果如图1(d)所示。E2峰值为567.5 ± 0.2 cm−1,这与大面积自由立GaN薄膜中报告的值(567.4 cm−1)非常接近。与此同时,GaN在散装Si基板上的E2峰值为565.8 cm−1,表明GaN薄膜中存在拉伸应力。GaN-on-SOI晶圆的翘曲度约为100 μm(相比之下GaN-on-Si晶圆为约45 μm),这是由于5μm厚的(111)Si器件层的残余应力以及GaN缓冲层/过渡层为Si散装基板优化所致。未来工作中将进一步优化GaN外延层以适应SOI基板。表I列出了SOI和散装Si样品的基本特性。

器件制造从通过Cl2/He干法刻蚀进行的台面隔离开始。接着,通过电子束蒸发沉积了源/漏欧姆金属堆叠Ti/Al/Ni/Au,随后在N2气氛下850°C下进行35秒的快速热退火。然后沉积了Ni/Au栅金属,并在N2气氛中进行了400°C的栅后退火,持续10分钟。制造了带有和不带有AlN/Al2O3(2 nm/10 nm)介质钝化层的器件。对于E型器件,栅金属沉积前进行了CF4等离子体处理。D型和E型HEMT器件在同一样品上制造,如图1(c)所示。在本信中,所有器件的栅长LG为1.5 μm,栅源距离LGS也是1.5 μm。设计的栅漏距离LGD为5、10、15和20 μm。

III. 结果与讨论

GaN-on-SOI晶圆上D型和E型HEMT的直流输出和转移特性如图2所示。所有展示的器件具有1.5 μm的栅长(LG)和10 μm的栅宽(WG)。D型器件的阈值电压为−4.0 V,E型器件的阈值电压为+0.9 V,在VDS = 10 V时。两个器件的亚阈值斜率约为75 mV/dec。

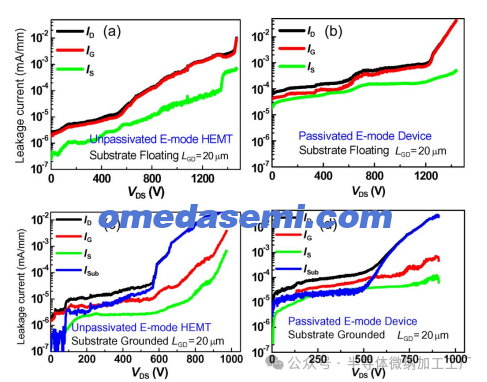

图3展示了GaN-on-SOI晶圆上E型HEMT的三端OFF状态特性,在VGS = 0 V时进行测量。

(a) 未钝化器件,

(b) 具有浮动终端的钝化器件(在Si承载晶圆上)。

(c) 未钝化器件,

(d) 具有接地终端的钝化器件(在Si承载晶圆上)。

D型和E型器件的峰值跨导Gm约为150 mS/mm。在D型HEMT(VGS = 1 V)和E型HEMT(VGS = 2.5 V)中,最大漏电流分别为646 mA/mm和315 mA/mm。已确认GaN-on-SOI晶圆和GaN-on-Si(散装)晶圆表现出类似的自加热效应(功率密度为10 W/mm)。这是因为4μm厚的GaN外延层和氧化层上的5μm(111)Si能够有效地扩散来自热点的热量,而不像Si SOI CMOS晶圆那样由于氧化层上方薄硅(最多几百纳米厚)导致热散发效率较低。

使用[10]中描述的方法,测得钝化E型HEMT(LGD = 10 μm)在100毫秒开关时间和200V OFF状态应力下的动态导通电阻为静态值的1.57倍。值得注意的是,100毫秒的开关时间仅能评估当前“慢陷阱”抑制,未来应通过适当的测试设备缩短此时间。

OFF状态特性通过Agilent B1505功率器件分析仪/曲线跟踪仪进行测量。图3(b)和(c)展示了GaN-on-SOI晶圆上LGD = 20 μm的钝化和未钝化E型HEMT的三端OFF状态击穿特性。对于钝化器件,测得的OFF状态漏电流在800V漏极偏置以下比未钝化E型HEMT增加了约一个数量级,这是由于通过AlN/Al2O3钝化层的横向漏电流所致。以Id = 10 μA/mm作为击穿标准。对于基板浮动的E型器件(通过将探针台的夹具设为浮动),击穿主要由栅漏电流主导,钝化器件的击穿电压为1354 V,未钝化器件为1471 V。当基板通过探针台的夹具接地时,钝化器件的击穿电压为806 V,未钝化器件为832 V。此时,垂直基板到漏极的漏电路径开始占主导地位。

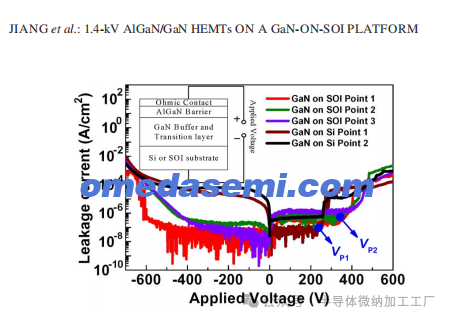

图4. GaN-on-SOI和GaN-on-Si(散装)平台上的垂直漏电特性。在不同样品的多个芯片上测量了多个点。(插图) 两端测试配置。

图5. GaN-on-SOI平台上制造的E型HEMT的RON与击穿电压关系。源/漏欧姆接触(每个接触的延伸长度为1.5 μm)被包含在RON的计算中。

在VDS > 500 V时,漏极漏电流增加并最终导致漏极的“击穿”,这一击穿通过漏电流标准进行定义。

为了研究SOI晶圆的SiO2层对垂直漏电流的影响,测量了在隔离的欧姆接触垫(100 μm × 100 μm)之间和底部承载晶圆之间的两端I-V特性,如图4所示。观察到不对称特性。

在正向偏置下(顶部电极为正偏),SiO2层使得漏电流的急剧上升延迟了95 V(即,VP 2 − VP 1),这大约是0.2 μm SiO2层的击穿电压。随着偏压增大,漏电流急剧上升,对应的是电子从Si通过III氮化物/Si界面注入,之后漏电流主要由通过GaN缓冲/过渡层的空间电荷限制电流导电。

在反向偏置下(顶部电极为负偏),GaN-on-SOI样品明显在电子向下导电至承载晶圆之前表现出较小的漏电流。SiO2层提供了一个能量屏障,阻止了垂直漏电流的特性,这些特性在GaN-on-SOI和GaN-on-Si(散装)样品上是可重复的,正如图4中多个点的测试结果所示。

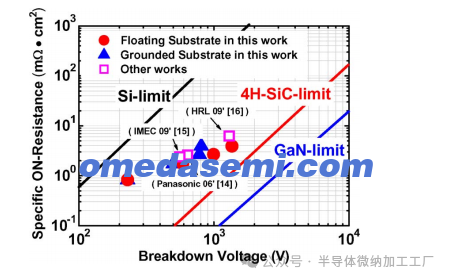

图5中绘制了E型HEMT(LGD = 5、10、15、20 μm)在RON与击穿电压之间的关系,表明SOI平台上的器件在性能上与散装Si基板上的最先进器件具有竞争力。GaN-on-SOI平台的主要优势是Si器件层和Si承载晶圆中双Si取向的设计。

IV. 结论

在GaN-on-SOI平台上制造的高电压D型和E型AlGaN/GaN HEMT已经展示。该器件具有高击穿电压、低导通电阻和减少的垂直漏电特性。SOI晶圆提供了在不同应用中使用不同晶体取向的硅材料的灵活性。