摘要:在本研究中,我们展示了在200毫米SOI(硅基绝缘体)衬底上生长氮化镓(GaN)缓冲结构的外延生长过程。该外延层使用反向阶梯型超晶格缓冲层(RSSL)生长,由两个不同铝成分比的超晶格(SL)层反向堆叠而成。上层具有较高的铝成分比,产生拉伸应力而非累积的压缩应力,并减少晶片的原位弯曲,从而实现了对厚度为3.3 µm的缓冲层晶片弯曲度的良好控制,弯曲度≤±50 µm。得益于具有柔性特性的SOI衬底,所生长的GaN层具有良好的晶体质量,并且实现了3.3 µm厚GaN缓冲层的750V击穿电压。外延GaN缓冲层在SOI衬底上的击穿电场强度估计约为2.27 MV/cm,较GaN-on-Si外延缓冲层的击穿电场强度更高。该RSSL缓冲层还展示了较低的缓冲层离散度,低于10%,足以满足后续器件和电路加工的要求。我们在该RSSL缓冲层上制作了D模式GaN HEMT,结果显示良好的开关比约为109,且击穿电压为450V。

关键词:GaN-on-SOI;反向阶梯型超晶格缓冲层;金属有机化学气相沉积

#用于氮化镓外延功率器件的 111晶向SOI晶圆

#全国产SOI晶圆定制加工 #468寸50nm-15um热氧片

库存片:

220nmSI高阻-3umSIO2-675umSI 6寸8寸 用于薄硅硅光

3000nmSI高阻-3umSIO2-675umSI 6寸8寸 用于厚硅硅光

#尺寸4-8寸

#最小起订量1片

#热氧层厚度范围50nm-15um

#膜厚精度最高精度+-5nm

#厚膜SOI-减薄抛光工艺600nm到微米级,加离子束精修,超级高精度膜厚均匀性

#CavitySOI-带空腔SOI晶圆,光刻显影刻蚀键合制作SOI一条龙

#FDSOI -最薄顶层10nm,特殊工艺精修,粗糙度小,膜厚精度高

普通超薄:SMARTCUT+离子束精修

超级超薄:EPI+SMARTCUT+离子束精修

#超平硅片-TTV500nm

我们为客户提供晶圆(硅晶圆,玻璃晶圆,SOI晶圆,GaAs,蓝宝石,碳化硅(导电,非绝缘),Ga2O3,金刚石,GaN(外延片/衬底)),镀膜(PVD,cvd,Ald,PLD)和材料(Au Cu Ag Pt Al Cr Ti Ni Sio2 Tio2 Ti3O5,Ta2O5,ZrO2,TiN,ALN,ZnO,HfO2。。更多材料),键合(石英石英键合,蓝宝石蓝宝石键合)光刻,高精度掩模版,外延,掺杂,6寸DUVKRF电子束光刻等产品及加工服务(请找小编领取我们晶圆标品库存列表,为您的科学实验加速。

请联系小编免费获取原文

文章名:750 V Breakdown in GaN Buffer on 200 mm SOI Substrates Using Reverse-Stepped Superlattice Layers

作者:Shuzhen You 1,2,* , Yilong Lei 1,2, Liang Wang 1,2, Xing Chen 3, Ting Zhou 1,2, Yi Wang 1,2, Junbo Wang 1,2,

Tong Liu 1,2 , Xiangdong Li 1,2 , Shenglei Zhao 1,2, Jincheng Zhang 1,2 and Yue Hao 1,

1. 引言

基于氮化镓(GaN)的功率器件具有较大的带隙、高电子迁移率和高击穿电压等优点,使其在高效能功率转换系统中非常受欢迎【1–3】。GaN材料的质量对实现优越的器件性能至关重要。由于具有低位错密度和低杂质浓度等特性,原生GaN大尺寸衬底被认为是GaN外延生长的理想选择【4】。然而,GaN大尺寸衬底非常昂贵,并且其直径通常小于100毫米。这一限制要求在外衬底上进行GaN的异质外延。考虑到经济因素,低成本的硅(Si)衬底相比于碳化硅(SiC)衬底更具吸引力【5】。为了充分释放GaN高电子迁移率晶体管(HEMT)在功率应用中的潜力,单片集成GaN集成电路(IC)是必需的,它能够比使用分立元件的功率系统实现更快的开关速度,通过抑制寄生电感和电容。然而,GaN-on-Si衬底上功率器件的单片集成面临设备之间的串扰问题以及通过“衬底接触”产生的“背栅效应”。抑制串扰和“背栅效应”的一种解决方案是使用结合了沟槽隔离的SOI(硅基绝缘体)衬底【6,7】。GaN-on-Si器件显示出“背栅效应”,即硅衬底影响GaN-on-Si结构中通道的电气特性。这种效应可能导致阈值电压和泄漏电流的不稳定,进而影响器件的性能和可靠性【8】。一种替代解决方案是使用具有聚铝氮(poly-AlN)核心的工程化衬底,这种衬底作为QST®(QROMIS衬底技术)商用化出售【9–12】。然而,QST®衬底的相对高价限制了其广泛应用。最近,GaN-on-Sapphire(GaN在蓝宝石上的外延生长)引起了极大关注,这种衬底也可用于GaN单片集成电路。然而,GaN-on-Sapphire的缺点是蓝宝石衬底的低热导率【13–15】。因此,SOI衬底在单片电路的低成本与高性能之间提供了良好的折衷。

SOI衬底的灵活结构由下至上组成:把持硅片、作为电气绝缘的埋氧化物(BOX)层和顶部硅半导体层。使用金属有机化学气相沉积(MOCVD)法在柔性SOI衬底上生长GaN的研究最早在文献中报道【16】,其外延层的晶体质量优于直接在硅衬底上的生长。这种晶体质量的提高归因于SOI衬底的柔性效应,顶部硅层和埋SiO2层吸收了大部分应变。Simoen等人在文献【17】中报告了在硅和SOI衬底上生长的AlN成核层的缺陷评估,并指出SOI衬底上层的陷阱密度较低,表明其AlN层质量较好。尽管在SOI衬底上生长的GaN材料可以获得更好的形态,但如何在外延过程中调整晶片的翘曲和应力控制仍然是一个需要解决的关键问题。缓冲层的设计长期以来一直是GaN异质外延研究的关键焦点。诸如AlN缓冲层【18】、AlGaN铝组分梯度缓冲层【19】和超晶格结构【20】等缓冲层策略已经相继被采用,旨在提高GaN外延层的质量。缓冲层设计的重要性不仅在于优化晶格质量,还在于其对垂直击穿特性的影响。对于高性能器件来说,垂直击穿能力至关重要。通常,缓冲层的厚度与击穿电压之间存在正相关关系。因此,当前的目标之一是进一步增大GaN-on-SOI衬底的尺寸和GaN层的堆叠厚度。然而,在柔性SOI衬底上生长厚GaN层以实现高击穿电压器件,在翘曲控制和机械控制方面仍然存在挑战【21】。单纯增加缓冲层厚度并不是一种可行的方法,因为随着缓冲层厚度的增加,晶片的固有曲率可能接近或甚至超过塑性变形曲率的上限。这种情况是不可取的,因为它可能导致外延晶片的开裂。为了解决这一问题,Imec提出了反向阶梯型超晶格(RSSL)结构,该结构由两个铝成分比不同的超晶格(SL)层反向堆叠而成。上层的铝成分比高于下层,引入拉伸应力并减少晶片的原位弯曲,从而实现减少翘曲的目标【22,23】。根据这一提议,我们在本研究中使用MOCVD方法生长RSSL结构的GaN缓冲层,并展示了3.3 µm厚GaN缓冲层的750V击穿电压。

2. 外延生长与器件制作

在本研究中,SOI衬底的顶部层为P型硅(111),厚度为2 µm,电阻率为0.01–0.025 Ω·cm;BOX层为厚度为1 µm的SiO2;把持层为硅(100),厚度为1070 µm。GaN-on-SOI缓冲结构在200毫米SOI衬底上生长,使用AMEC Prismo 480-PD反应室,通过MOCVD法,采用三甲基镓(TMGa)、三甲基铝(TMAl)和氨气(NH3)作为Ga、Al和N源气体,氢气(H2)作为载气。

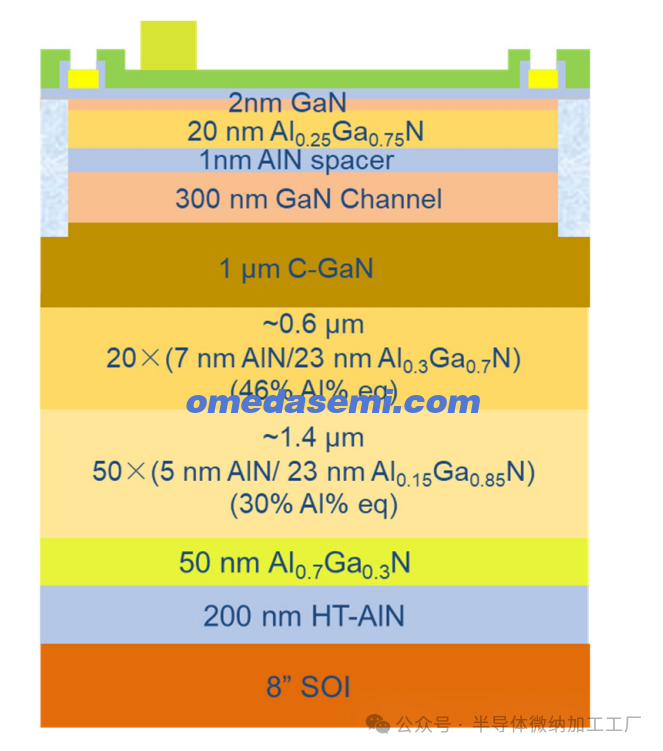

图 1. GaN 外延片结构示意图。

缓冲层的设计如图1所示,包含200 nm的AlN成核层、50 nm的AlGaN下过渡层、首先重复5 nm的AlN/23 nm的Al0.15Ga0.85N单元格50次(平均铝含量:Al%=30%)形成的第一超晶格(SL1)、其次重复7 nm的AlN/23 nm的Al0.3Ga0.7N单元格20次(平均铝含量:Al%=46%)形成的第二超晶格(SL2)、1 µm的碳掺杂GaN层、300 nm的GaN通道层、1 nm的AlN插层、20 nm的Al0.25Ga0.75N屏障层和2 nm的GaN帽层。欧姆接触使用Ti/Al/Ni/Au(20/140/55/45 nm)堆叠层处理,并在830°C的氮气环境中退火30秒。然后,进行多次氮离子注入工艺以实现横向隔离。随后,依次通过PEALD和PECVD沉积了2.5 nm的Al2O3和50 nm的SiO2层。器件的门电极金属由20 nm/120 nm的Ni/Au构成。沉积门电极后,使用CF4、Ar和N2气体进行反应离子刻蚀(RIE),刻蚀SiO2并打开源/漏窗口。Al2O3层作为RIE的刻蚀停止层,在SiO2被刻蚀后,通过在稀释的HCl中浸泡1分钟去除。所制作的HEMT具有100 µm的门宽(Wg)、1 µm的门长(Lg)、0.75 µm的门源间距(Lgs)和6 µm的门漏间距(Lgd)。

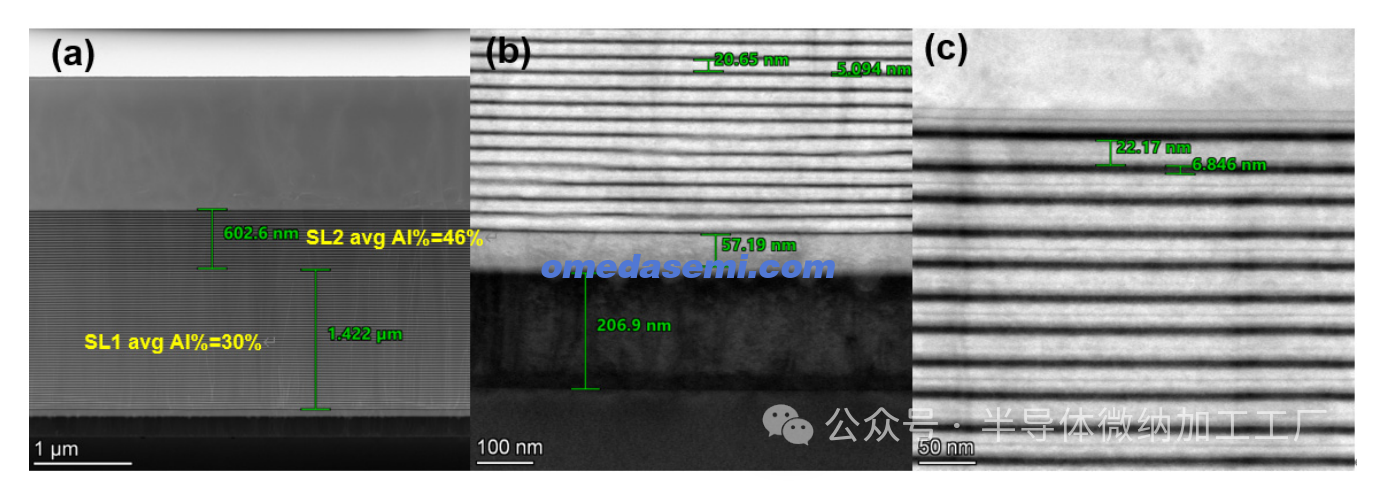

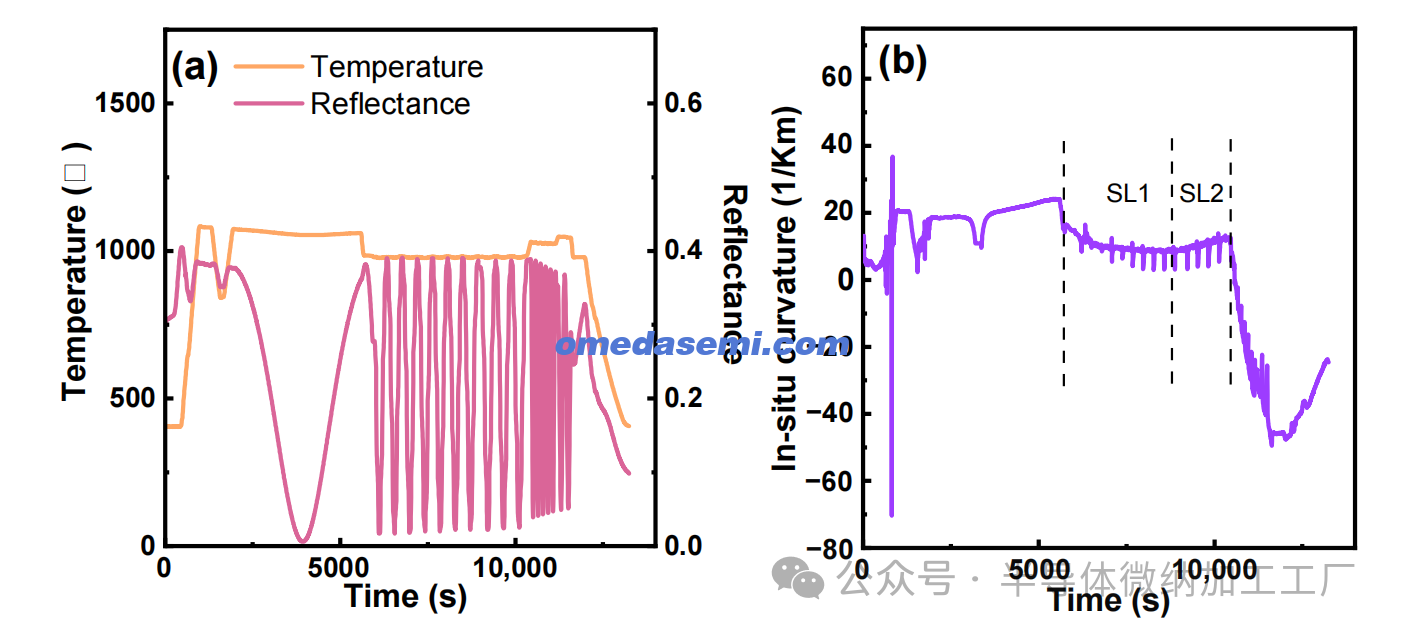

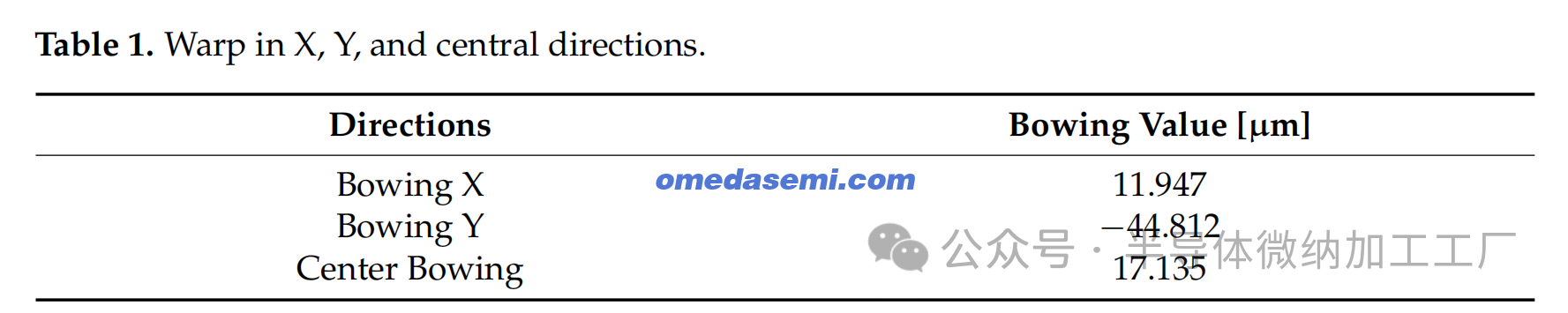

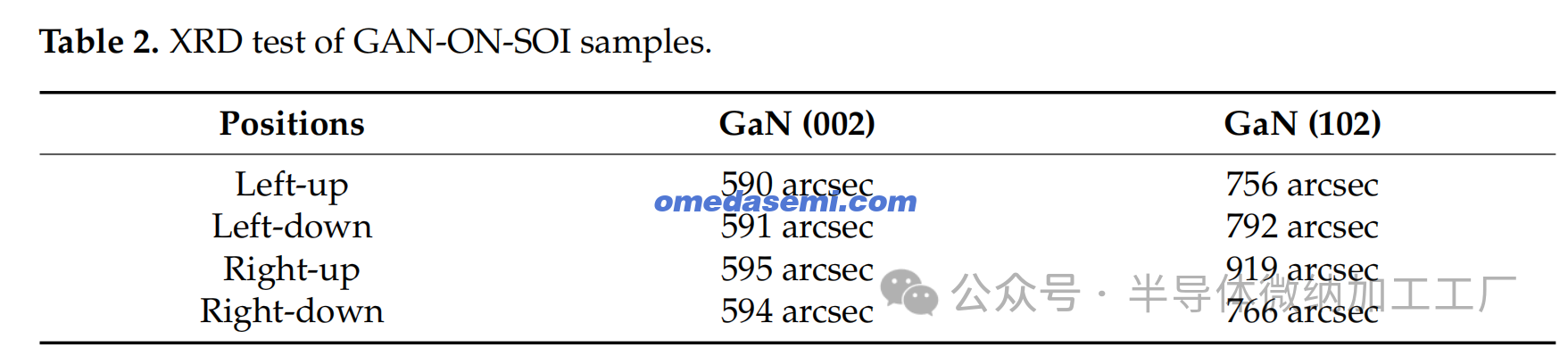

图 2. (a) 使用 RSSL 缓冲液拍摄的厚度为 ~3.3 μm 的外延层的 TEM 横截面图像。(b) SL1 的局部 TEM 放大倍率和 (c) SL2 的局部 TEM 放大倍率。图2展示了使用RSSL缓冲层生长的(Al)GaN堆叠的透射电子显微镜(TEM)横截面图,整体厚度约为3.3µm。在这个RSSL缓冲层中,第二超晶格(SL2,平均铝含量为46%)被堆叠在第一超晶格(SL1,平均铝含量为30%)之上。图 3. 缓冲液的生长曲线:(a) 反射率和生长温度,以及 (b) 原位晶圆曲率。图3显示了反射率、外延生长温度和晶片原位弯曲的缓冲层生长曲线。从图3b可以看出,生长曲率的斜率从SL1中的负值变化为SL2中的正值,表明SL2中较高的铝成分引入了拉伸应力,而不是传统阶梯型超晶格堆叠中的累积压缩应力。表1展示了在200毫米SOI衬底上外延后晶片的原位翘曲情况,结果表明晶片的原位翘曲得到了很好的控制,翘曲度始终保持在±50µm范围内,完全符合弯曲度≤±50µm的规格;晶片翘曲测试表明,RSSL结构能够有效调整晶片的固有曲率。采用这种RSSL方法后,我们的MOCVD反应室和器件加工试验线中未观察到晶片破裂的情况。获得了具有良好晶体质量的 GaN 层,如表 2 中的 X 射线衍射全宽半高值 (XRD FWHM) 值所示。

表 2 显示了 GaN-on-SOI 样品在四个位置的 XRD FWHM 值。这也反映了良好的一致性。

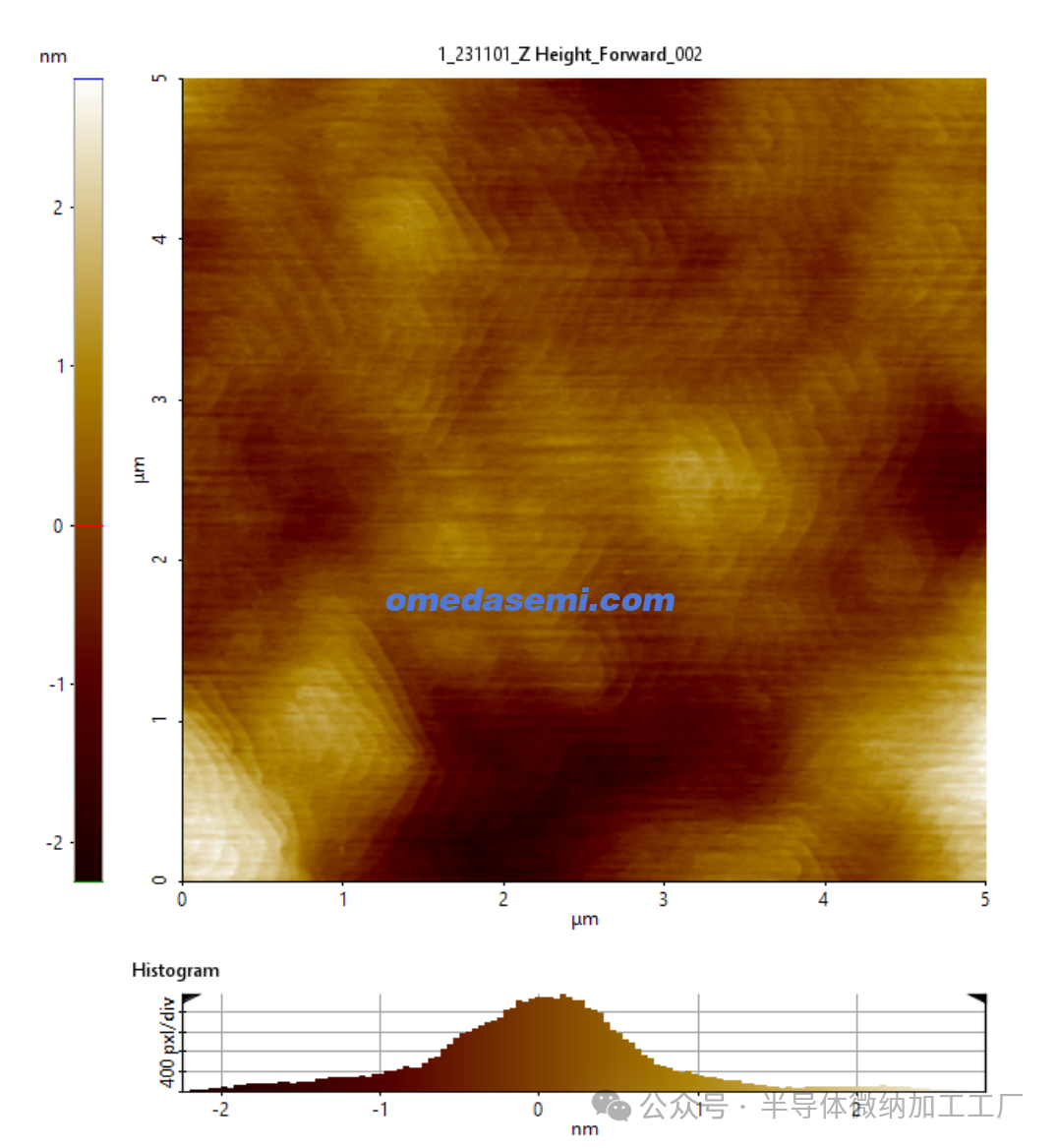

扫描原子力显微镜 (AFM) 用于测量扫描尺寸为 5 μm × 5 μm 的 GaN 外延层的表面形貌,如图 4 所示,AFM 图像显示光滑平坦的表面,RMS 值为 0.7 nm。

图 4. 200 mm GaN-on-SOI 表面粗糙度的 AFM 测试。

光滑的外延层表面有利于 2DEG 性能和后续的晶圆加工。

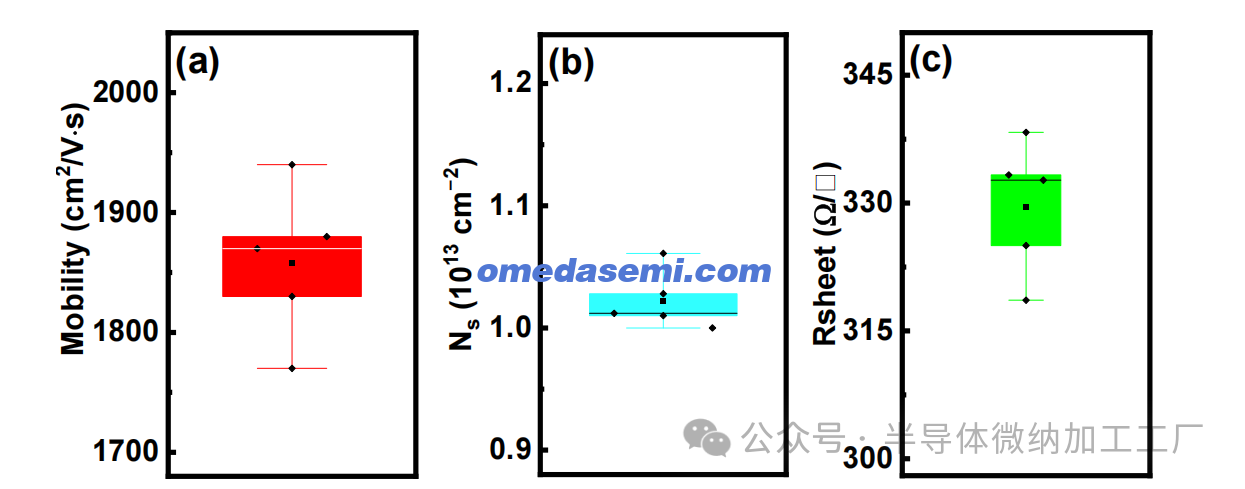

图 5. (a) 2DEG 电子迁移率,(b) 2DEG 浓度,和 (c) 2DEG 薄层电阻。

图 5 显示,基于该堆栈的 AlGaN/GaN 异质结具有优异的电性能,在 300 K 时,2DEG 迁移率和浓度分别为 1850 cm2/V·s 和 1.03 ×10 13 cm−2,2DEG 薄层电阻为 330 Ω/.

获得了具有良好晶体质量的 GaN 层,如表 2 中的 X 射线衍射全宽半高值 (XRD FWHM) 值所示。 表 2 显示了 GaN-on-SOI 样品在四个位置的 XRD FWHM 值。这也反映了良好的一致性。

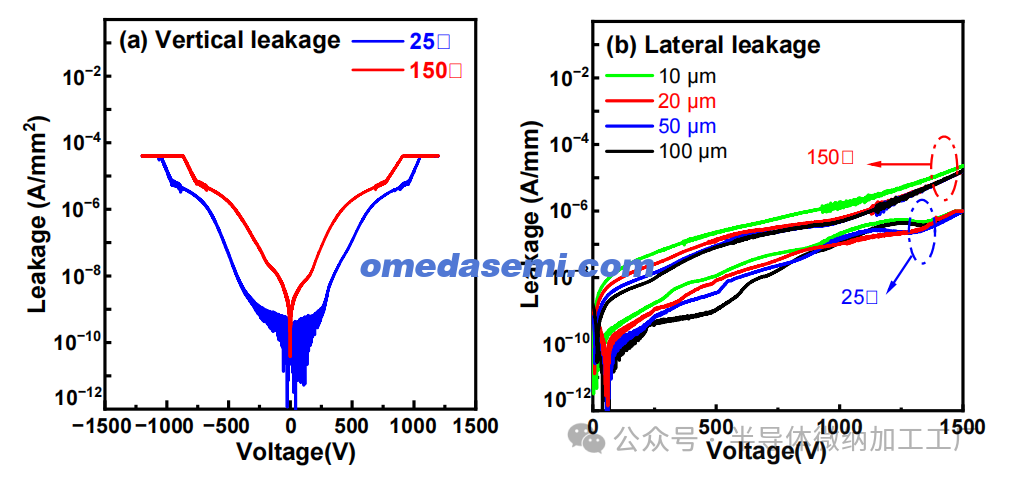

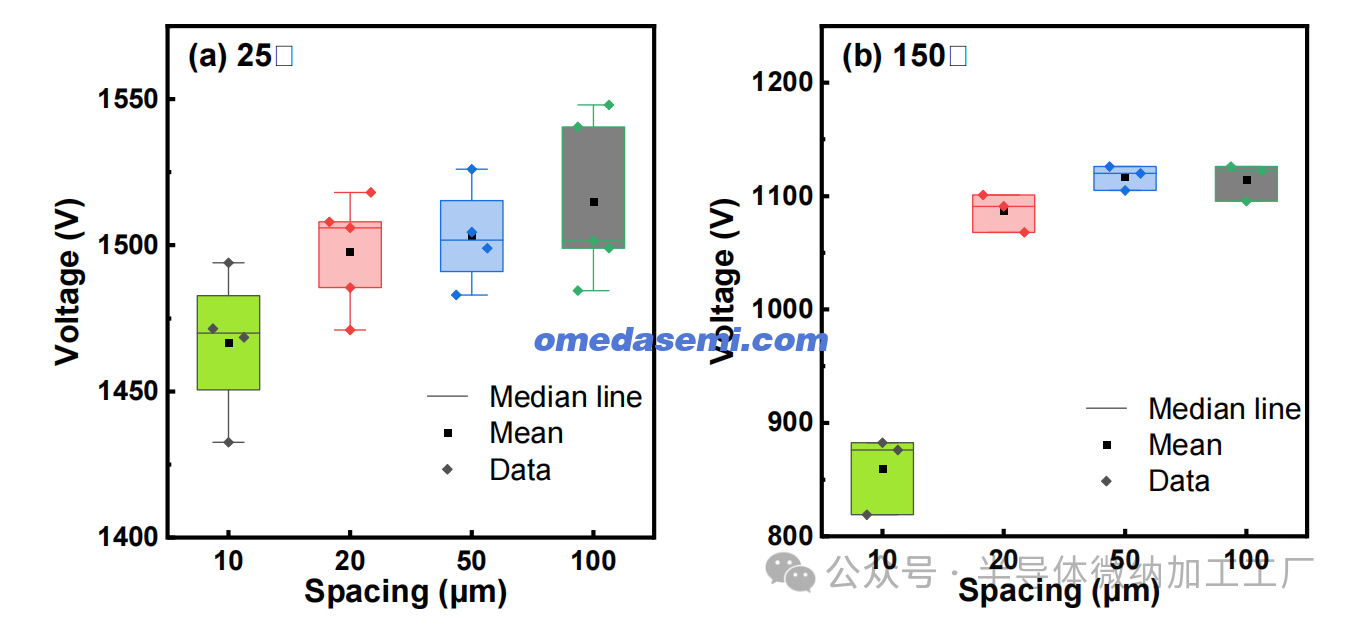

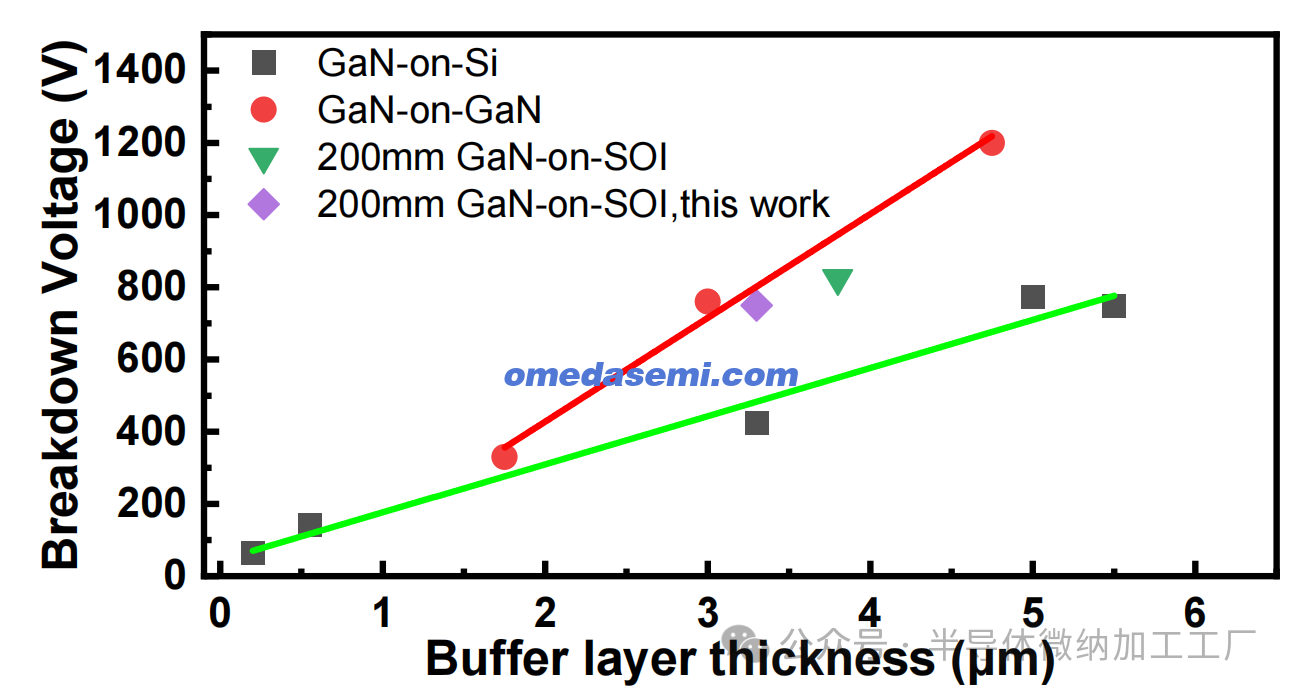

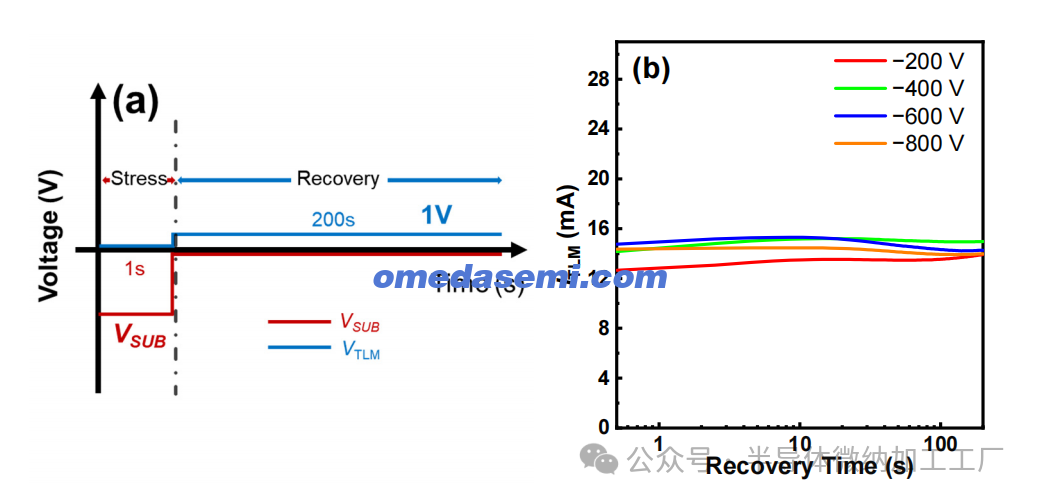

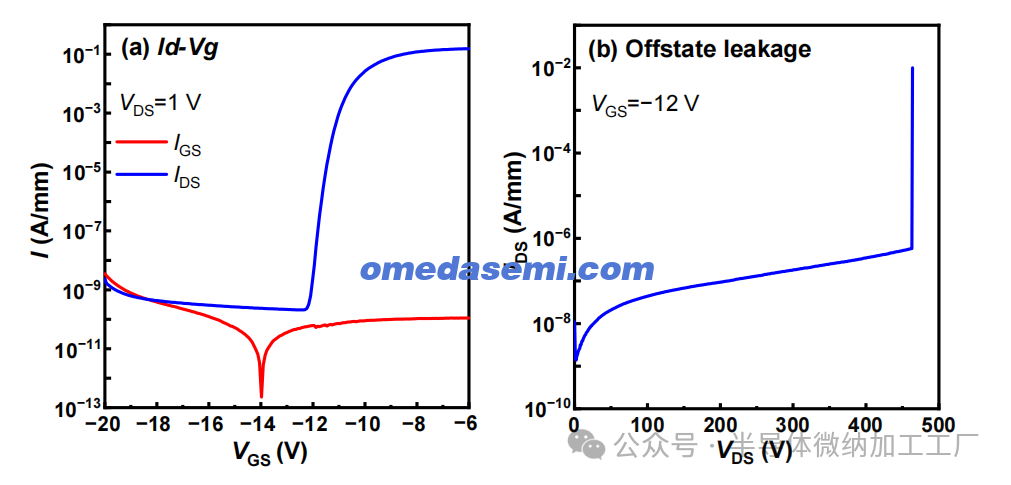

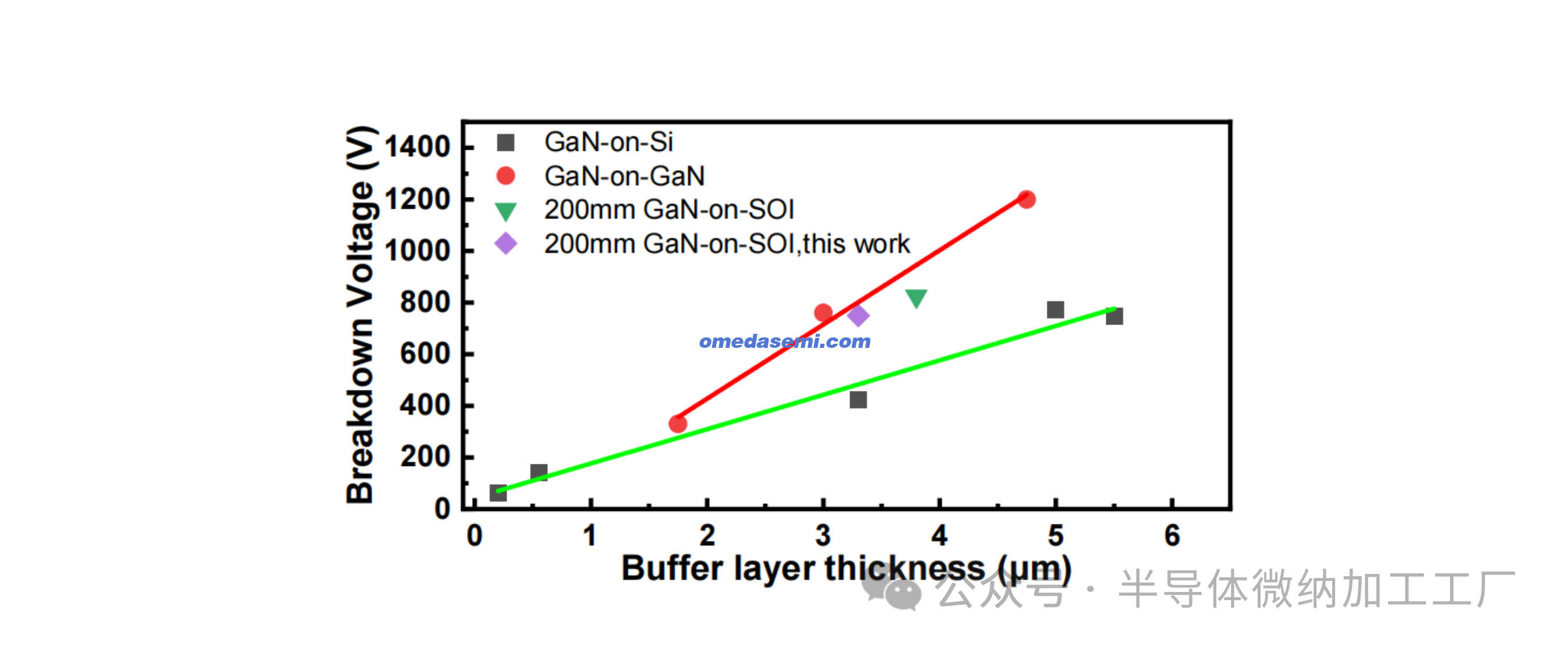

通过将衬底接地并用正或负电压偏置顶部欧姆阳极来测量垂直缓冲器泄漏。通过在两个欧姆触点之间施加偏置来测量横向缓冲器泄漏,并在它们之间施加隔离间隙。图 6. (a) 缓冲液在 200 mm GaN-on-SOI 衬底上的垂直和 (b) 横向泄漏曲线。从图 6a 中的泄漏曲线中,提取了 25 °C 时 ~900 V (@10 × 10−6 A/mm2) 的垂直击穿电压 (BV)。 众所周知,SOI 衬底中的盒子可以承受 100 V;因此,唯一的外延缓冲层可承受 ~800 V。 图 6b 中 25 °C 时的横向缓冲器泄漏曲线显示,对于 10 μm、20 μm、50 μm 和 100 μm 的隔离间隙,类似的击穿电压为 ~1500 V (@1 × 10−6 A/mm),表明缓冲器击穿电压由 GaN 缓冲层决定,而不是由隔离间隙决定。因此,横向缓冲器击穿电压大约是垂直缓冲器击穿电压的两倍,表明垂直 GaN 缓冲层承受 ~750 V 的电压,这略低于图 6a 中从垂直泄漏测量中提取的值,因为横向测量结构中的欧姆接触面积更大。 图 6a、b 还显示了外延堆栈在 150 °C 时的垂直和横向泄漏行为。 在 150 °C 时,堆栈的唯一垂直 GaN 缓冲层仍然可以承受 ~550 V 的击穿电压。图 7. 当电流达到 1 × 10−6 A/mm 时,带有 RSSL 缓冲层的 GaN-on-SOI 上不同隔离间距的电压值:(a) 在 25 °C 的温度下测试,(b) 在 150 °C 的温度下测试。同时,如图 7 所示,当电流达到 1 × 10−6 A/mm 时,我们在 25°C 和 150°C 下用 RSSL 缓冲层和各种隔离间距测试了 GaN-on-SOI 结构上多个位置的电压值。 可以观察到,在相同电极间距下,测量之间的电压偏差不超过 5%,显示出良好的一致性。25 °C 的 750 V 缓冲击穿电压用于将我们的工作与其他工作进行基准测试,如图 8 所示。图 8. 不同缓冲层厚度的 GaN 外延层在不同衬底上的击穿电压 [6,24,25,26](包括 Si 、GaN、SOI)。图 8 显示了在不同缓冲层厚度的不同衬底上生长的 GaN 的击穿电压。可以看出,缓冲层的击穿电压与缓冲层厚度几乎呈线性关系,斜率反映了缓冲层的电压电阻。从图中可以清楚地看出,GaN-on-GaN 具有最强的耐电压性,GaN 同质外延缓冲层的击穿电场为 2.3 MV/cm,接近 GaN 击穿场的理论值 3 MV/cm。然而,GaN 同结外延需要巨大的成本,这并不是衬底的最佳选择。要实现商业化,价格仍然是一个关键因素。对于成本相对较低的 GaN-on-Si,GaN-on-Si 缓冲层的击穿场强约为 1.33 MV/cm,这并不能最大限度地发挥 GaN 材料的优势。本工作在 200 mm SOI 衬底上制备的 GaN-on-SOI 外延层在外延缓冲层上的击穿场强约为 2.27 MV/cm,劣于 GaN-on-GaN 外延层的击穿场强,但优于 GaN-on-Si 外延缓冲层的击穿场强。然后,首先通过衬底对缓冲器施加应力,然后监测 2DEG TLM 结构的电流恢复情况 [27]来评估缓冲器色散,如图 9a、b 所示。图 9. (a) 缓冲分散的测试程序和 (b) 各种应力后的 TLM 电流 (ITLM) 恢复曲线。GaN-on-SOI 缓冲液表现出相当稳定的 ITLM,分散性小于 10%,这意味着该缓冲液足以进一步处理器件和电路制造。图 10. (a) 在 8 英寸 GaN-on-SOI 衬底上 LGD 为 6 μm 的 GaN 功率 HEMT 的对数转移特性,在 Vds = 1V 下测量;(b) 关态击穿曲线,在 Vgs = −12V 时测量。图 10a 显示了 GaN HEMT 在该 RSSL 缓冲器 8 英寸 SOI 上的传输特性,阈值电压约为 −11 V (@1 × 10−4 A/mm)。由于外延堆栈结构的低垂直缓冲器泄漏和源极/漏极欧姆触点的低接触电阻,晶体管表现出约 10:9 的良好开/关电流比。 图 10b 显示,在关断状态条件下 (@Vgs = −12 V),器件泄漏保持在低水平 (<1 × 10−6 A/mm),直到击穿电压达到 450 V 左右 在这项工作中,在 200 mm SOI 衬底上制备了反阶梯超晶格结构的 GaN-on-SOI 缓冲液。可以看出,通过将 Al 百分比从 SL1 增加到 SL2,生长曲率的斜率从 SL1 的负变为 SL2 的正,表明 RSSL 缓冲器在传统的阶梯式超晶格堆栈中引入了拉应力而不是累积压缩应力。这种反阶梯超晶格缓冲器产生了可控的原位晶圆曲率,对于 3.3 μm 厚的缓冲器,晶圆的翘曲小于 ±50 μm。在 GaN-on-SOI 堆栈上实现了 750 V 的击穿电压,外延 GaN 缓冲层的击穿场强估计约为 2.27 MV/cm,优于 GaN-on-Si 外延缓冲层的击穿场强。这项工作中的缓冲器还表现出小于 10% 的缓冲器色散,表明该缓冲器有望在器件和电路制造中进一步加工。该 RSSL 缓冲器上的制造器件具有良好的 ~10:9 的开/关比,并且可以承受 450 V 的击穿电压。