LN在0.35到5μm的光谱范围内透明,并通过泊克尔斯效应显示出强烈的二阶非线性(r系数为35 pm/V)【7】。这一效应允许纯相位调制,而不产生吸收变化。LN波导调制器设计有两种主要类型。当晶体的光学轴位于晶圆平面时,我们有x型或y型切割设计;当光学轴垂直于晶圆时,我们有z型切割设计。通过晶圆粘接集成在硅上的薄切LN晶体称为薄膜LN(TFLN)。有关基于LN的硅集成调制器的全面回顾,读者可参考张等人最近的文章【10】。

在电信波长(1550 nm)的TFLN调制器中,电压-长度乘积Vπ·L通常为1.5−3 V·cm【10】。刻蚀LN层产生的波导具有0.3 dB/cm的损耗,因此可以使用LN制作肋型或脊型波导,这种设备称为单片式设备【11】。另一种类型的设备是混合设计,其中波导由不同材料制成。最好的LN混合设备性能指标(来自不同设备)已展示Vπ·L为3 V·cm,损耗低至0.2 dB/cm,带宽为106 GHz,而单片设备则具有Vπ·L为1.2 V·cm,损耗为0.15 dB/cm,带宽为100 GHz【11】。最近,金等人通过双电容电极设计展示了0.64 V·cm的Vπ·L【12】。

BTO是硅光子学中的新兴材料。它具有已知最大的泊克尔斯系数之一(1300 pm/V),可以方便地集成到硅上,并且与CMOS制造工艺和工厂完全兼容【13】。它是一种从近紫外到中红外光谱区域的介电材料,具有低光学损耗(极化前为1.5 dB/cm)和相对较高的折射率(1550 nm时no= 2.304,ne= 2.267)。关于BTO的基本光电性质及其与硅集成的努力,读者可参考最近的综述文章【14】【15】【16】【17】。

在讨论基于硅集成BTO调制器的现状之前,我们想指出这项技术已有三十多年历史。BTO单片波导和波导相位调节器由西北大学的Wessels团队在1990年代中期首次开创【18】【19】。这些波导是在通过低压金属有机化学气相沉积(CVD)在MgO基板上沉积的0.3 μm厚的BTO薄膜中制造的。薄膜的表面粗糙度约为13 nm,需要进行平整化。对于1.55 μm的光,40 nm高、2.5 μm宽的脊型波w导展示了5 dB/cm的损耗。电极之间的间距为5至20 μm,长度从2.7 mm到1.0 cm不等。报告显示,调制深度大于14 dB,半波电压为20 V。对于1.5 μm和1.3 μm光,测得的有效泊克尔斯系数reff约为50 pm/V。报告显示在5 MHz下,Vπ·L为4 V·cm【19】。

更早之前,McKee及其同事在橡树岭国家实验室专门为电光应用研究了BTO与硅的集成【20】。他们成功地通过分子束外延(MBE)使用BaO缓冲层将25 nm厚的BTO薄膜集成到3英寸(001)硅晶圆上。七年后,他们对硅-钙钛矿界面有了更好的理解【21】。结果证明,二元氧化物缓冲层并非必需。几年后,摩托罗拉开发了一种更好的制造工艺,用于将SrTiO3沉积到硅(001)上【22】【23】。该工艺使得在(001)硅上获得高质量的单晶SrTiO3(STO)缓冲层,形成了如今的硅和SOI集成BTO的核心【24】【25】。

A. BTO与硅及其他材料的集成

使BTO与硅集成的关键步骤,即在硅(001)上进行STO外延,仍然需要使用MBE进行精确的原子层控制。MBE不是一种适合大规模生产的技术。然而,在STO缓冲层的支持下,可以使用几种标准沉积工艺将外延单晶BTO集成到硅上。

化学气相沉积(CVD)是一种以其多功能性和非常高的生长速率而著称的工艺【26】。在钛酸钡(BaTiO3)中,金属有机化学气相沉积(MOCVD)是最常用的CVD变种。Wessels等人使用MOCVD在MgO单晶上沉积BTO薄膜【27】。他们的混合设备,使用SiN波导与BTO集成,展示了VπL为1.1 V·cm和有效泊克尔斯系数为162 pm/V【28】。原子层沉积(ALD)是CVD过程的一种特殊变种。Ngo等人首次报道了通过ALD在硅上外延生长BTO【29】。Lin等人测量了通过ALD生长的BTO在传输几何中的电光性质,并报告了有效泊克尔斯系数为26 pm/V【30】。泊克尔斯响应值较低,可能是由于使用的薄膜厚度较小【31】以及ALD生长的钙钛矿薄膜的柱状微结构导致一些孔隙。另一种化学方法,溶胶-凝胶沉积,因其低成本而闻名,但薄膜的结构质量相对较差【32】。Edmonson等人使用这一工艺在硅上生长外延BTO【33】。该工艺经高温氧气流处理后,90 nm薄膜的电光响应为89 pm/V。

MBE是一种物理气相沉积形式,使用超高真空和元素源。在BTO生长过程中,金属钡和钛作为金属源,分子氧即可足以产生高质量的薄膜。在过去几年中,已经制造了集成在硅上的MBE生长的BTO电光器件,并且报告了一些电光调制器中有效的泊克尔斯系数【34】。这证明了MBE所能达到的薄膜极高的晶体质量,其主要缺点是沉积速率较慢,并且随着时间的推移会出现通量漂移。

脉冲激光沉积(PLD),有时称为激光烧蚀或激光MBE,是一种薄膜沉积方法,使用一系列高能激光脉冲快速蒸发源材料(称为靶材),靶材通常是与待生长薄膜组成相同的块状材料。Petraru等人通过PLD在MgO单晶基板上制造了BTO脊型波导【35】。最近,Cao等人通过PLD在DyScO3基板上生长了BTO,尽管没有展示电光调制,但他们在单片脊型波导中演示了非常低的传播损耗(2 dB/cm)【36】。

射频溅射沉积与PLD有许多相似之处。溅射通常是在轴向几何结构中进行的,这会遭遇类似于PLD中的飞溅问题。一种解决方法是使用90°的离轴几何结构,这可以消除大部分颗粒,但沉积速率较PLD有所降低。A. Rosa等人通过射频溅射在STO缓冲的硅-绝缘硅片(SOI)晶圆上生长了50 nm的BTO,并报道了有效的泊克尔斯系数为157 pm/V【37】。最近,Posadas等人利用离轴射频溅射沉积了MBE质量的BTO薄膜在硅上,演示了有效的泊克尔斯系数为157 pm/V【38】。Kim也使用射频溅射在MgO上生长了BTO,并展示了有效的泊克尔斯系数为110 pm/V【39】。在物理气相沉积技术中,离轴射频溅射提供了沉积速率和光学性能的最佳组合。

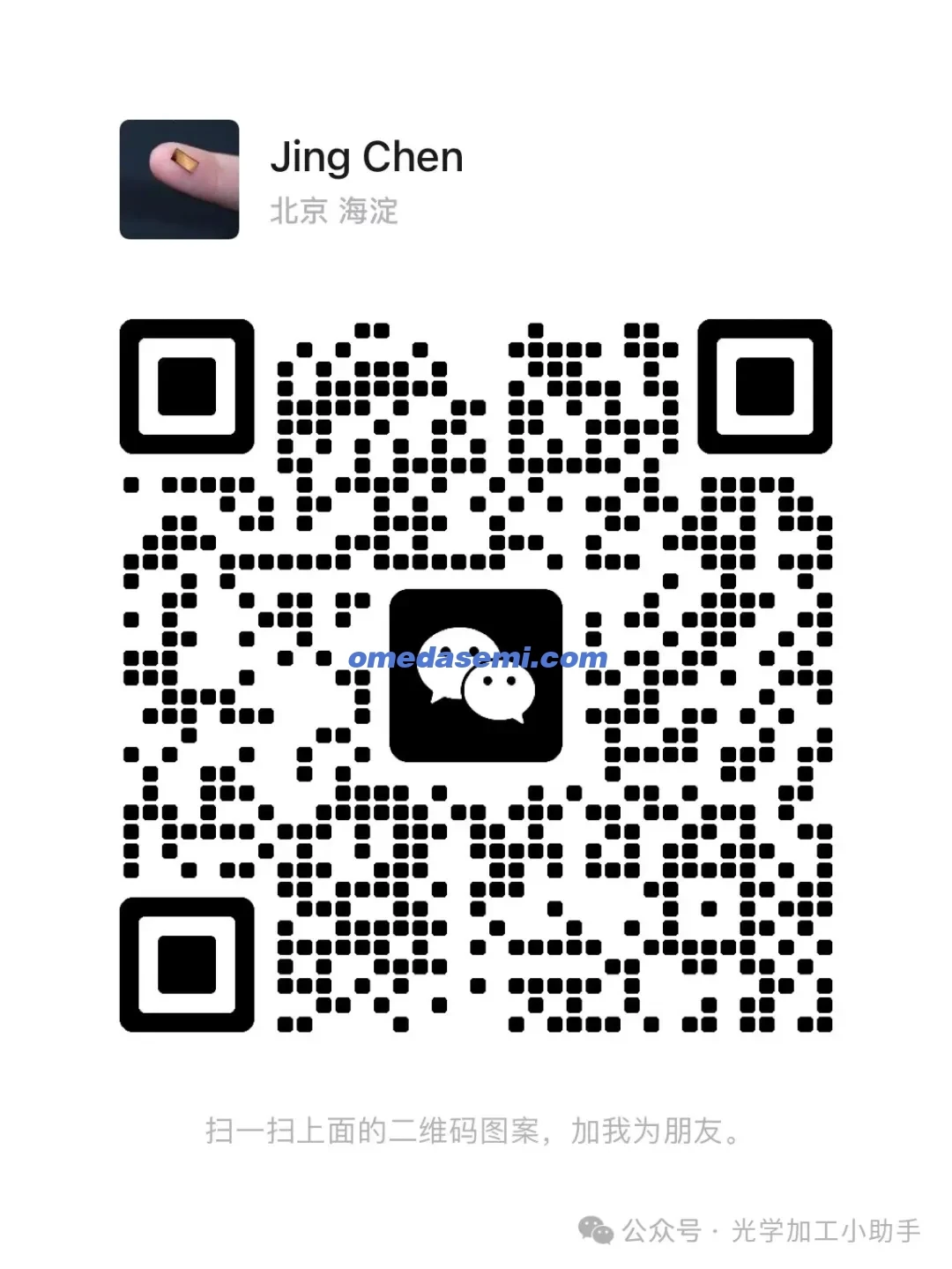

图1. c取向(a),(b)和a取向(c),(d)BTO薄膜在极化前后的畴形态示意图。需要注意的是,对于c取向薄膜,畴是铁电的,可以进行对齐,从而形成单畴薄膜。a取向薄膜的畴可以是晶体学畴或铁电畴(在(c)和(d)面板中用点划线表示)。在(d)面板中,水平电场对齐了水平的180°畴并消除了相应的畴壁,但晶体学畴壁和正交方向的180°畴仍然存在。

由于四方晶系BTO的c/a比接近于1,能够在硅上稳定地生长平面内(长轴平行于表面)或a取向以及垂直于表面(长轴垂直于表面)或c取向的BTO薄膜。两种方法各有利弊,都可以通过适当的器件结构来使用。c取向的器件类似于Z切割的LN器件,而a取向的则类似于X或Y切割的LN器件。在a取向的薄膜中依赖于巨大的r42分量,但在场方向上有非常大的相对介电常数分量,而在c取向的薄膜中,r33的十倍下降被介电常数的五十倍减少所补偿。高介电常数会导致器件在射频频率下操作时性能下降。因此,两种取向在高频下提供合理的调制。两种情况下都可以使用单片(刻蚀在BTO中)或混合波导。c取向薄膜的一个潜在优势来自于能够实现完全极化,从而消除c取向薄膜中铁电域之间的180°畴壁。在a取向薄膜中,可能会有四种不同的畴:它们是两个90°的平面内晶体学畴,每个可以进一步分裂成两个180°的铁电畴。虽然铁电畴壁可以通过极化驱除【40】,但晶体学畴壁无法被驱除。该情况如图1所示。对于a取向薄膜,水平方向的电场消除了180°畴壁(点划线),但并未消除可能带电的晶体学畴壁。这些畴壁可能是BTO器件损耗较LN器件高的原因。

应该指出,外延BTO薄膜的实际微观结构是薄膜所经历的电气和机械边界条件以及薄膜电导率的复杂函数。此外,在大多数a取向薄膜中,STO缓冲层上方的区域在20至30 nm的范围内仍然是c取向的,之后才变为a取向。原始的、未极化的微观结构通常在薄膜从生长至室温冷却过程中建立。最近的相场模拟表明,冷却路径在建立最终的畴形态中起着至关重要的作用【41】。模拟进一步表明,硅集成BTO薄膜的有效泊克尔斯系数可能对畴形态的细节以及畴壁分布敏感【42】。畴壁对有效泊克尔斯效应的影响是各向异性的。在薄膜中观察到的有效泊克尔斯系数的降低,很可能是由于复杂的畴形态、畴壁的存在,可能还与薄膜厚度内的c到a畴转变有关。

本文的其余部分组织如下。我们将简要回顾当前BTO基电光调制器的进展,按照沉积类型分为MBE或射频生长,按照架构分为单片式或混合式,按照晶体取向分为a取向或c取向。每种方法都有其优点和挑战,可能所有类型都会在不同应用中找到其位置。

II. 当前状况

A. MBE生长的BTO薄膜

2014年,Xiong等人报告了硅集成钛酸钡(BaTiO3,BTO)电光调制器的早期突破【43】。他们使用生长在SOI晶圆上的单晶BaTiO3薄膜,通过MBE工艺制造了环形谐振器和马赫-曾德尔调制器(MZM)。在这些MZM中,他们使用了80 nm厚的BaTiO3,电极间隙为10 μm,器件长度为400 μm。其结构中的上下硅层均为110 nm厚。他们报告了213 pm/V的有效泊克尔斯系数,但传播损耗相对较高,为44 dB/cm,且马赫-曾德尔型设备的调制带宽仅为0.8 GHz。

Eltes等人报告了首个基于混合BaTiO3-Si结构的低损耗波导。他们使用了在50 nm BaTiO3薄膜上,在SOI上方用SiO2条形波导几何结构,并在100 nm厚的Si器件层上图案化,发现BaTiO3-Si混合波导的传播损耗主要来源于SrTiO3缓冲层中的氢【44】。他们展示了通过在500°C下用氧气退火30分钟,可以将传播损耗降至2.2 dB/cm。

在1.55 μm的电光调制方面,2019年,Eltes等人报告了硅集成BaTiO3调制器的最佳VπL值【45】。他们报告了一种MZM结构的VπL值为0.23 V·cm,器件长度为1 mm,电极间隙为2.6 μm,相当于380 pm/V的有效泊克尔斯系数。他们还展示了其设备能够在20 Gb/s的速率下工作。Rosa等人进行了BaTiO3在硅上的射频表征,并表明MBE生长的薄膜可以实现超过40 GHz的电光调制带宽【46】,但理论上应该更高。

Abel等人展示了基于硅槽波导和环形谐振器架构的混合BaTiO3-Si设备的数据传输速率最高可达50 Gb/s。BaTiO3的厚度为220 nm,电极间隔为2 μm,硅波导宽750 nm,厚度为100 nm。他们的异质结构还涉及通过晶圆粘接来去除BaTiO3层下的硅。他们报告的VπL值为0.45 V·cm,基于他们报告的dn/dV值为3.4 × 10^−4 V^−1,应该对应于267 pm/V的有效泊克尔斯系数。报告的损耗为∼10 dB/cm【34】。

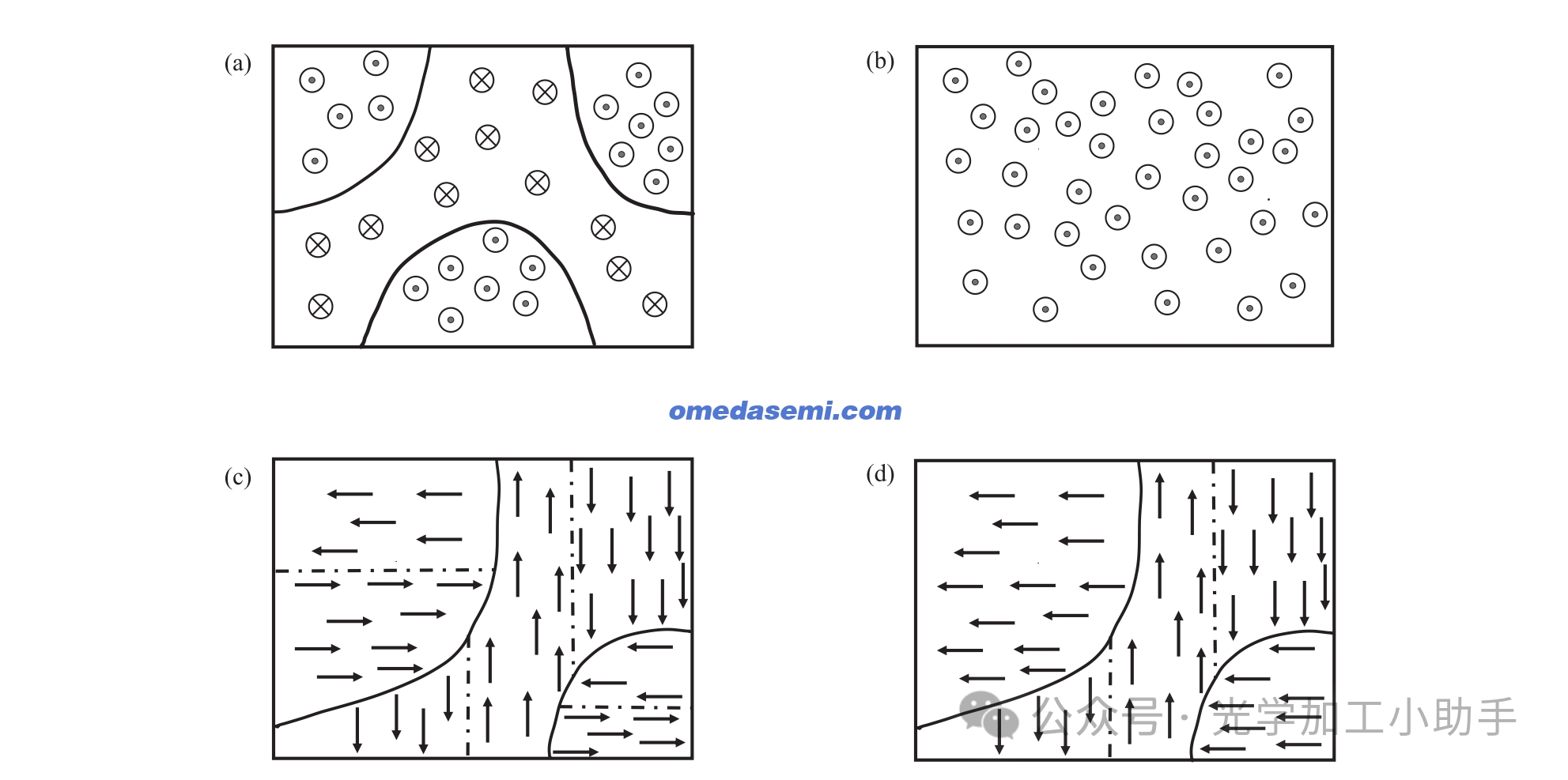

硅集成BTO薄膜的大泊克尔斯系数直接转化为低VπL值,并且这一点已经得到了充分验证。结合低插入损耗,这表明可以显著减少功耗。然而,直到最近,人们还不清楚基于BTO的调制器是否能够提供高数据速率。Eltes及其同事展示了一种单片BTO、低损耗MZM,在不使用驱动器的设置中,以9 fJ/bit的电功率消耗,在线性接收器DSP(数字信号处理)下实现了低于200 Gb/s HD-FEC(硬决策前向纠错)阈值的净PAM4(四级脉冲幅度调制)数据速率【47】。MZM的总插入损耗,包括分路器和直流调谐器,仅为2 dB。经过MZM后,光信号通过500米标准单模光纤(SSMF)传输。这模拟了大约10公里O波段边缘的有效信号传播色散(信号需要通过掺铒光纤放大器(EDFA)放大到6 dBm以进行补偿)。使用112 GBd PAM-6,展示了在6.7%开销HD-FEC阈值下的净比特率为262 Gb/s。

图2. (a) 无驱动器数据传输实验的实验设置,该实验不使用Tx,仅使用线性Rx DSP。在RF放大器输出端捕获的电眼图,显示为插图。(b)经过Rx DSP后的眼图,分别为128 GBd OOK(净117 Gb/s)和106 GBd PAM-4,低于HD-FEC限制(净200 Gb/s)。(c)BER与接收光功率(ROP)关系图,(d)OOK和PAM-4信号的驱动摆幅。转载自文献【47】。

作者们展示了通过消除对离散调制器驱动器的需求并简化满足目标前FEC比特错误率(BER)所需的DSP,功耗可以进一步减少。得益于低Vπ和高带宽,他们展示了在不需要Tx DSP的情况下,仅使用线性前馈均衡器(FFE)在Rx DSP中进行驱动器无需求的数据传输(<1 Vpp)(图2)。使用OOK(开-关键控),在128 GBd下,通过在FFE中使用11个tap实现了低于KP-4 FEC阈值的数据传输(图2(c))。使用PAM-4信号,达到了净数据速率为200 Gb/s(HD-FEC,31个tap)。

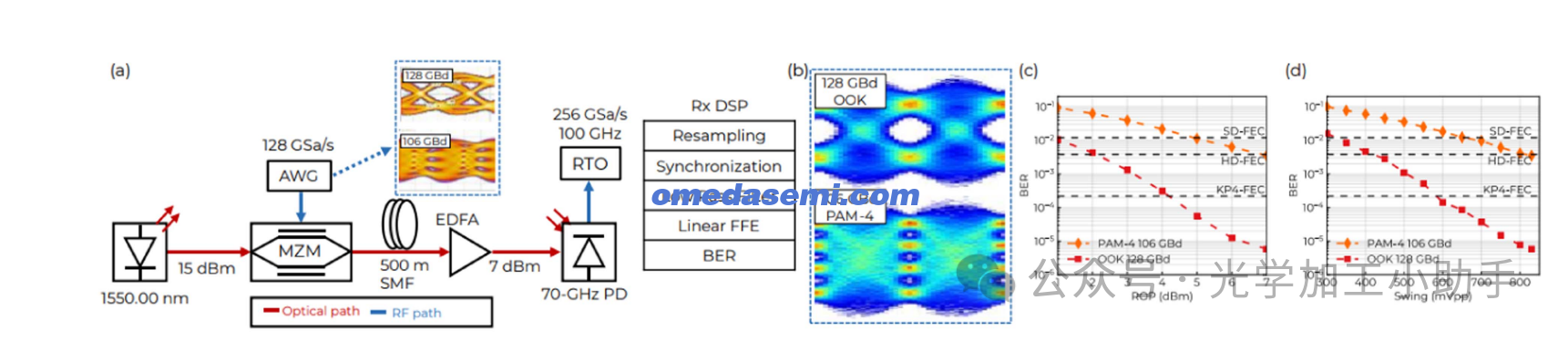

此外,关于在低温下操作的BTO基硅集成调制器也应该提及【48】。低温技术对于未来的量子计算系统以及下一代高性能经典计算系统变得至关重要。在低温下工作的光子集成电路(PIC)对于量子计算技术是必需的。硅在低温下的表现受到缺乏高效低温电光调制的限制。Eltes及其同事展示了使用硅集成BTO器件从室温到4 K的电光开关和调制。他们展示了在4 K下有效泊克尔斯系数为200 pm/V。该设备显示了30 GHz的带宽、超低功耗调谐和20 Gb/s的高速数据调制。使用500 μm混合(SiN-BTO)MZM,并且使用2 × 2多模干涉分路器(图3(a))。

图3. 在4 K下使用基于BaTiO3的器件演示低功耗开关和高速数据调制。

(a) 使用的马赫-曾德尔配置的示意图,用于在两个端口之间切换。

(b) 马赫-曾德尔开关两个端口的传输与施加电场的关系,以及静态功耗。

(c) 数据调制实验设置的示意图。

(d) 在10和20 Gb/s下记录的眼图,Vpp = 1.7 V,对应的调制能量为45 fJ bit⁻¹。转载自文献【48】。

黄色箭头指示输入端口,红色和蓝色箭头分别指示输出端口1和2。电压源V用于在马赫-曾德尔干涉仪的一个臂上施加电场E,由绿色箭头指示。图3(a)的插图显示了波导的横截面。在4K时,BTO的漏电流比室温时低约百倍,因此静态功耗小于10 pW,并且仅需30 pJ的动态能量即可在6 × 10^6 Vm^−1的电场下(图3(b))在两个光输出之间切换(π相位移)。该电场保持在BTO的强制场以下,以排除铁电畴切换的贡献。这对应于大约50 V的电压和VπL的5 V·cm。

他们还通过将伪随机比特序列发送到使用混合BTO-Si波导制造的环形调制器(Q≈6000)并记录光学眼图(图3(c))来进行数据调制实验。数据信号是使用任意波形发生器(AWG)生成的,然后放大并与偏置电压Vbias通过偏置T型接头结合。一个调谐激光器设置为约1550 nm,提供光载波。经过低温探针站的调制后,光信号通过光纤放大器放大并经过滤波后由光二极管检测。光二极管的电信号被放大,然后在实时示波器上记录。图3(c)的左插图显示了波导横截面,右插图显示了调制器的电光-电频率响应。使用仅1.7 V的驱动电压(Vpp),在20 Gb/s的速率下实现了数据传输,结果是每比特45 fJ的低能耗(图3(d))。

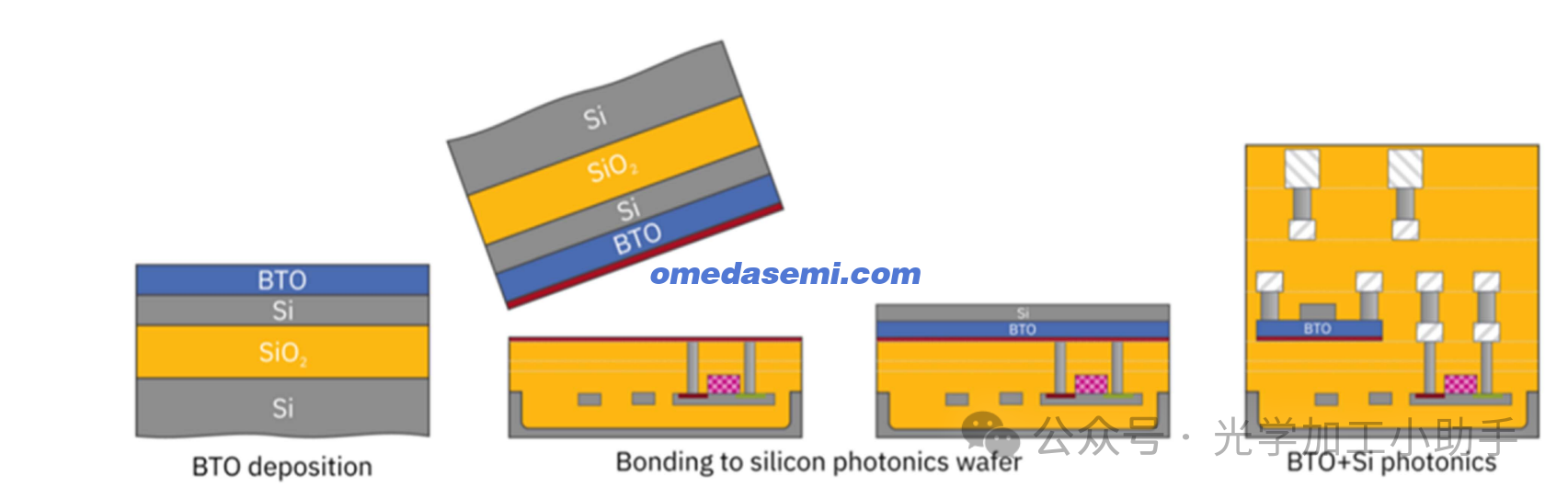

BTO可以在大直径晶圆(最高可达12英寸)上生长,并且在这一平台上有可能实现高密度光网络。将BTO集成到现有的硅光子学平台上可以通过低温晶圆粘接实现【49】。使用这种方法,BTO层可以在CMOS工艺中以任何平面化的水平集成。该工艺的示意图如图4所示。

图4. 使用分子晶圆粘接技术将BTO与硅光子学集成的概念。BTO沉积在SOI晶圆上,然后可以与任何具有电子或光子结构的晶圆在平面化的水平上进行粘接。通过机械和化学工艺去除供体晶圆。然后,BTO器件可以与任何后端工艺步骤一起加工。转载自文献【49】。

首先,在SOI晶圆上生长BTO层,然后使用分子晶圆粘接技术通过Al2O3粘合层将其转移到平面化的基底晶圆上。该过程包括在250°C下退火,这与前端和后端工艺的热预算一致。

B. 等离子体器件

电光调制器的另一个有前景的方向是结合BTO的大泊克尔斯系数和等离子体技术,以增强场强。这样的等离子体BTO调制器在硅上展示了将电压-长度乘积减少到0.2 V·mm,在推拉操作的马赫-曾德尔调制器中实现了高达72 GBd的操作。等离子体BTO调制器还被发现能够承受高达250°C的温度【50】。另一方面,SiN可以处理高输入功率,提供更大的透明窗口,较低的热灵敏度,并且由于核心和包层之间较低的折射率对比,具有更宽松的制造公差和超低的传播损耗。文献【51】【52】介绍了在SiN平台上以BTO作为活性电光材料的纳米级等离子体调制器。这些调制器是单片集成的,并与波导结合。采用了制造厂生产的SiN平台进行制造。成功演示了216 Gbit/s PAM-2和256 Gbit/s PAM-4强度调制与直接检测(IM/DD)。

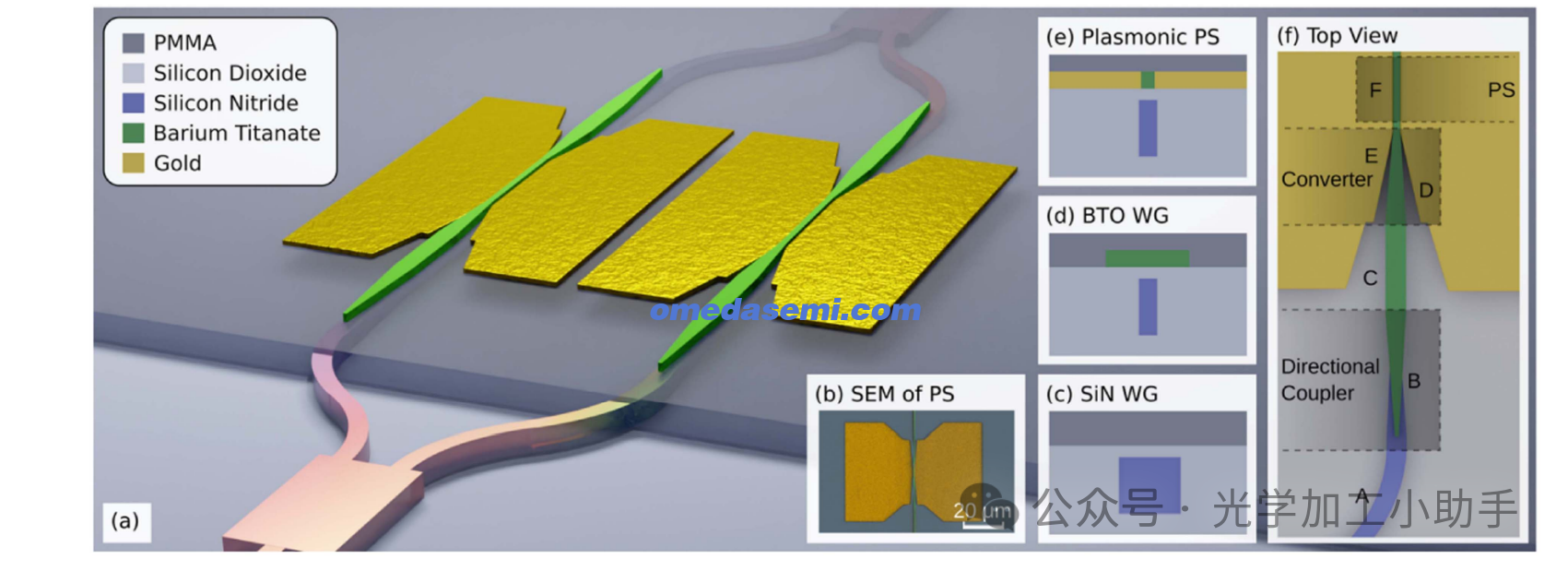

基于SiN的混合等离子体调制器包括一个马赫-曾德尔调制器(MZM)干涉仪,每个臂中有一个相位调节器。设备的示意图如图5(a)所示。

图5. 基于SiN平台的单片BTO等离子体调制器。

(a) 三维示意图,展示了SiN MMI中的1:2分裂,随后的BTO光子波导和BTO等离子体波导转换,以及两个BTO等离子体相位调节器。

(b) 同一芯片上的参考相位调节器的彩色扫描电子显微镜(SEM)图像。

(c) 嵌入在SiO2中的SiN波导横截面,并进行平面化,留下100 nm厚的层间氧化物(ILO)。

(d) BTO接入波导的横截面。

(e) 等离子体相位调节器(PS)的横截面,金属接触位于与BTO填充的纳米级槽相邻的位置。

(f) 调制器的俯视图,显示了用于层间过渡的定向耦合器、光子到等离子体的转换器和相位调节器部分。转载自文献【51】。

光从光纤耦合到SiN波导,采用有效且适应制造公差的非晶硅(aSi)覆盖光栅耦合器,用于TE极化光。SiN用于无损耗的无源路由和分路。图5(c)显示了嵌入SiO2中的SiN波导横截面。SiN到BTO的耦合是通过一个80 μm长的垂直定向耦合器实现的,用于层间过渡。SiN波导的尺寸从800 nm × 800 nm减小到200 nm × 800 nm,而BTO波导从200 nm × 200 nm开始,并逐渐变为名义上的单模横截面1200 nm × 200 nm(见图5(d))。

该设备是在两种材料平台的组合上制造的。SiN波导首先在平面化前定义并包覆氧化物。平面化后,BTO被晶圆级集成。调制器本身是在后端工艺中制造的。首先,通过电子束光刻(EBL)对BTO进行图案化并蚀刻,形成波导和等离子体部分。非晶硅通过等离子体增强化学气相沉积(PECVD)沉积,使用EBL图案化,并通过感应耦合等离子体反应离子蚀刻(ICP-RIE)进行蚀刻,用于非晶硅覆盖光栅耦合器。然后,沉积金属以形成等离子体调制器,并增加光子到等离子体的转换器。图5(b)显示了制造好的设备图像。

虽然模拟预测了光纤到光纤插入损耗(IL)低于10 dB,但原理验证调制器展示了29 dB的光纤到光纤插入损耗,而相位调节器(PS)本身与等离子体转换器一起贡献了20.5 dB。

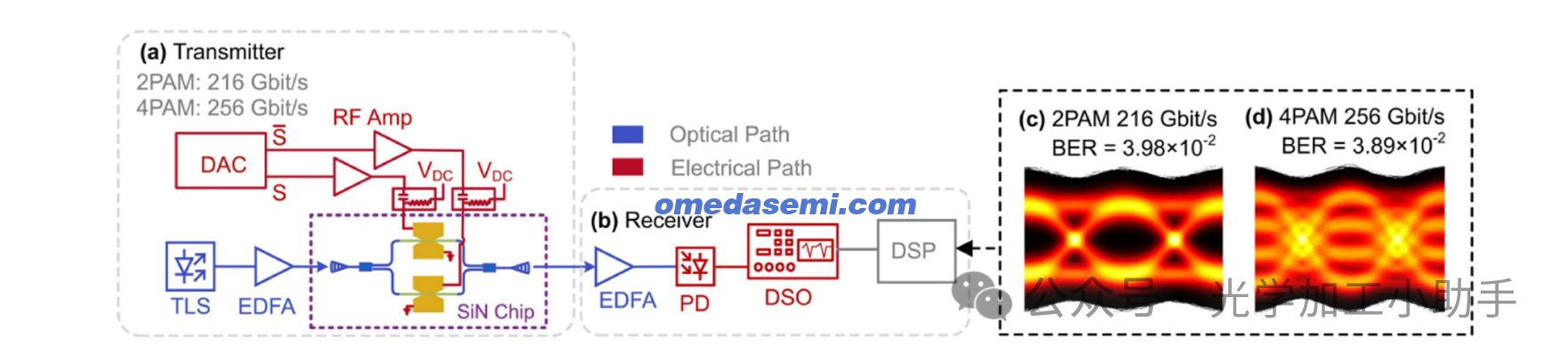

图6. (a) 数据传输实验中发射器的测量设置示意图,(b) 接收器的测量设置示意图。

(c) PAM-2 216 Gbit/s数据传输的眼图,BER为3.98 × 10⁻²。

(d) PAM-4信号以256 Gbit/s的数据速率传输的眼图,BER为3.89 × 10⁻²。

转载自文献【51】。

数据实验的测量设置,包括眼图,显示在图6中。发射器如图6(a)所示,光路为蓝色,电路为红色。接收器使用直接检测方案,如图6(b)所示。它首先通过EDFA放大信号,然后信号经过滤波后送至光电探测器(PD)。图6(c)显示了传输的216 GBd PAM-2信号的眼图。实现了3.98 × 10^−2的比特错误率(BER),信噪比(SNR)为6.2 dB。对于128 GBd PAM-4信号(图6(d)),BER为3.89 × 10^−2,SNR为11.43 dB。

该设备在100 MHz到70 GHz的范围内进行了特性测试,且在10 GHz以上展示了平坦的频率响应,Vπ·L为144 Vμm。得益于调制器的高带宽,可以为最高160 GBd的信号速率采用简化的DSP。

需要注意的是,除了【47】中的设备外,迄今为止所有描述的设备都采用了某种形式的混合技术,并依赖于部分限制在半导体波导结构中的TE模式。这简化了波导蚀刻并导致较低的损耗。

C. 射频溅射生长的BTO薄膜

上述所有BTO与硅光子学集成的里程碑都是通过MBE生长的BTO薄膜实现的。出于实际原因(约0.5 nm/min的慢沉积速率),MBE薄膜的厚度限制为300 nm以下;生长速率太慢且不稳定,无法用于大规模制造。Posadas等人报告了一种可制造的工艺,用于生长厚度可达1 μm的高质量钛酸钡薄膜【53】。他们使用了低功率密度(2.2 W/cm²)的离轴射频磁控溅射,以实现与MBE生长薄膜类似的薄膜结构质量,但沉积速率是其十倍。该工艺在每次运行中都非常稳定,适合用于制造。他们使用传输几何结构和马赫-曾德尔调制器设备测量了300 nm溅射的BaTiO3薄膜的电光特性。在两种情况下,他们得到约160 pm/V的有效泊克尔斯系数,对于马赫-曾德尔调制器,VπL值为0.42 V·cm,类似于MBE生长薄膜的报告值。

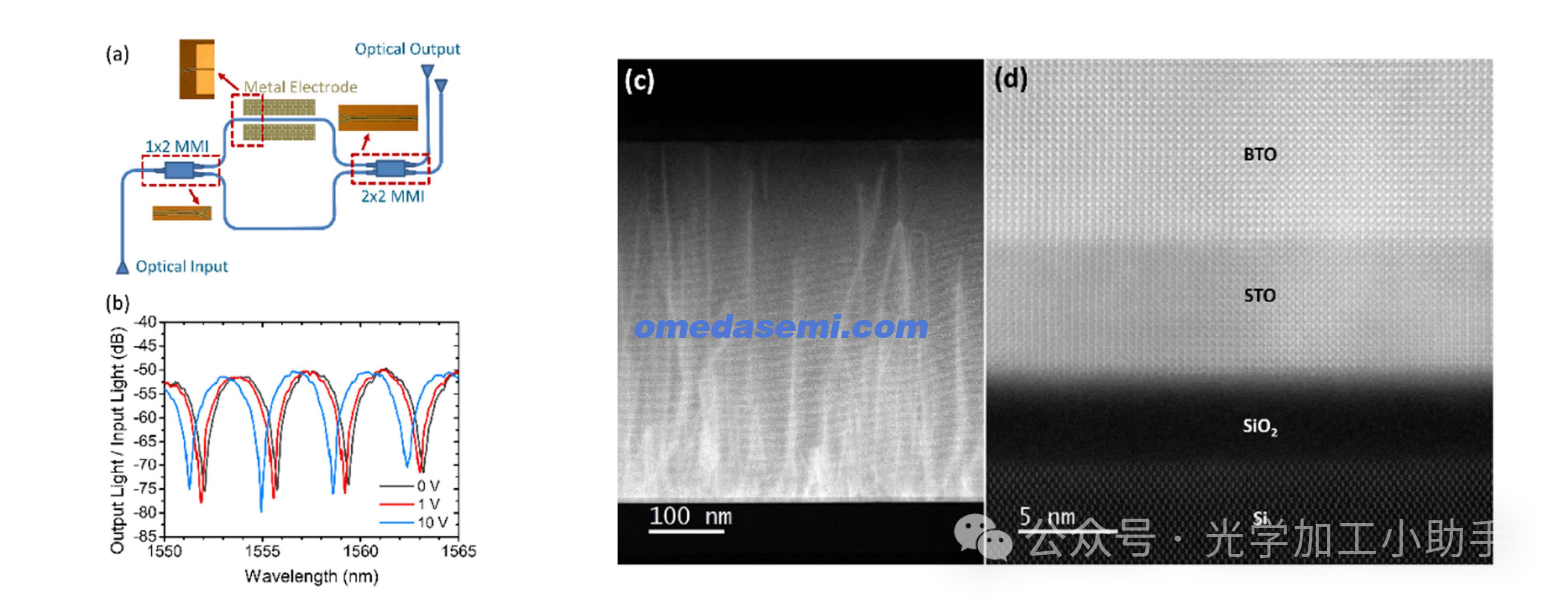

图7.

(a) MZM的示意图,光学显微镜图像展示了1 × 2 MMI、2 × 2 MMI以及带有电极的活性区域部分。

(b) 不同直流电压下的MZM调制响应。

(c) 低倍放大STEM图像,显示整个BTO层。垂直的白色线条为位错。

(d) 同一薄膜的界面区域的原子分辨率STEM图像。BTO和STO处于外延配对状态。

转载自《ACS Appl. Mater. Interfaces》13, 51230。版权归美国化学学会所有,2021年。

他们的马赫-曾德尔设备的长度为375 μm,电极间隙为2.6 μm,450 nm的SiNx作为波导在BTO上方生长并图案化(图7(a)和(b))。图7(c)和(d)显示了在700°C下生长的500 nm BTO薄膜的ADF-STEM横截面图像。

D. 单片器件

最近,溅射BTO的电光响应已通过基于单片波导相位调节器的调制器进行了探索【54】【55】。Posadas等人报告了一种基于BTO脊形负载硅波导的MZI调制器,如图8(a)所示【54】。

图8.

(a) Z切BTO MZI调制器测试设备的横截面几何结构;

(b) 制造设备的光学显微镜图像:分路器和电极馈送部分(左),以及射频垫片(右)。

转载自文献【54】。

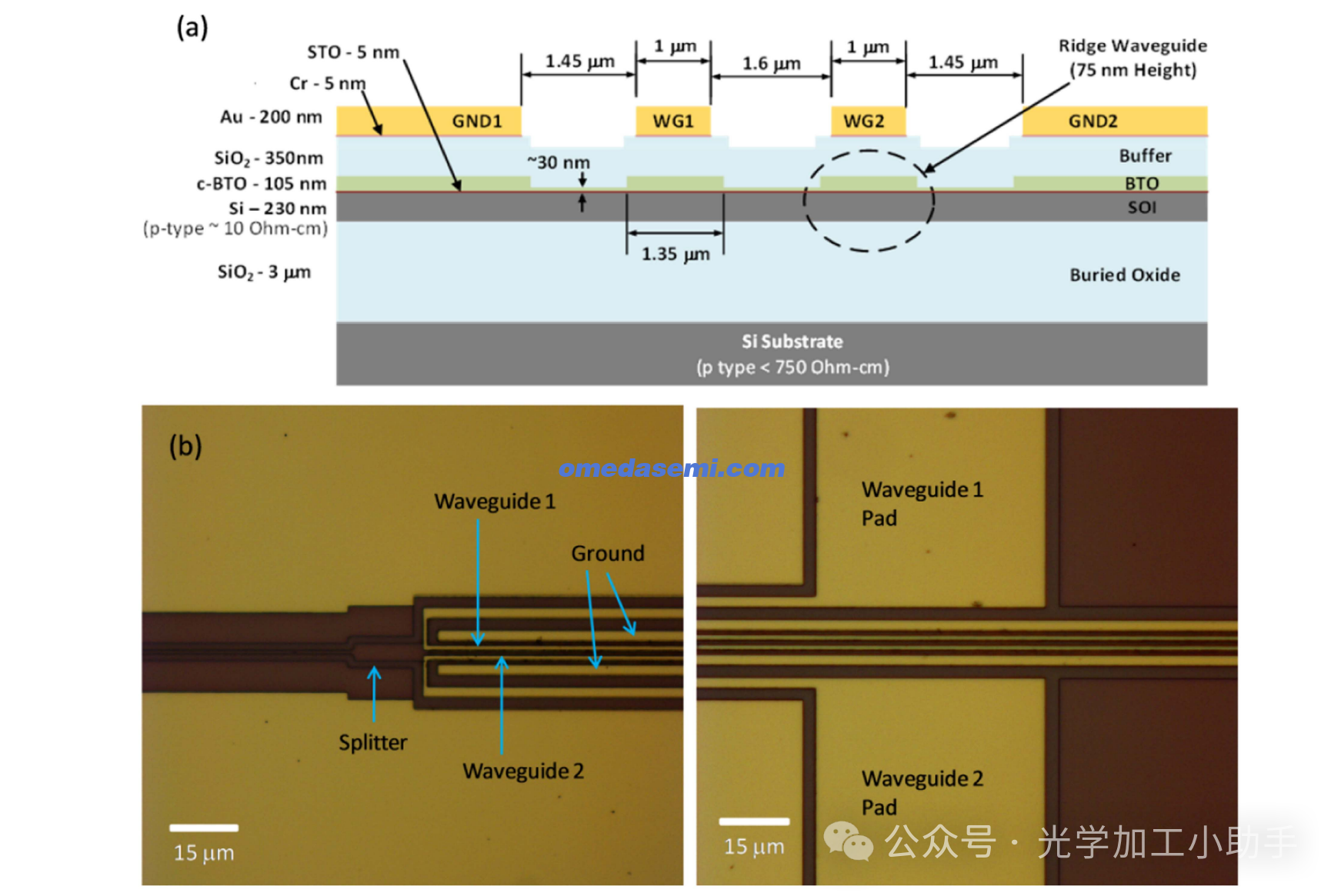

该设备使用0.1 μm厚的c取向BTO薄膜(即Z切)通过离轴射频溅射沉积在标准光子SOI晶圆上制造【56】。在器件制造之前,通过Metricon 2010棱镜耦合器系统测量了波导的损耗。报道的波导损耗为1550 nm波长下,TM模式为1.08 dB/cm,TE模式为1.65 dB/cm,确认了该材料适合用于调制器的制造。需要注意的是,测量是在未极化的情况下进行的。所提出的设备结构不需要额外的硅和BTO层,这主要是为了简化制造过程。30 nm高的BTO脊形通过湿法刻蚀BTO进行图案化。刻蚀后,沉积了350 nm的SiO2缓冲氧化层,并通过图案化和金属脱膜工艺使用Cr/Au进行金属化。图8(b)显示了设备的光学显微镜图像。

调制测试仅进行了至10 MHz。电光系数(r33)是通过模拟施加电场和光学模式在BTO中的电光重叠,并结合传播模式对BTO材料折射率的敏感度来计算的。对于BTO脊形负载波导设计,随着BTO材料折射率变化,传播光学模式的相对变化被计算为δ = 0.32,横向磁(TM)极化光波导折射率为2.344。r33系数表示沿c方向应用E场时,BTO材料折射率的变化。施加1V时,BTO中光模式内的电场约为30 kV/m。提取的r33值为134.4 pm/V,虽然稍高于通过波导电光测试测得的值,但一致。作者指出,BTO的介电常数对提取的r系数有重大影响。对于建模和模拟,假设沿表面法线c方向的体积相对介电常数为56(ε33)。实际上,BTO薄膜的表面法线方向的介电常数可能大于56,因为厚度大于0.1 μm的薄膜可能包含一些具有非常高介电常数的a取向材料。基于这些论点,预计r33系数至少为134.4 pm/V,可能稍高,取决于材料实际的c取向介电常数。

基于这些结果和模拟,作者得出结论,Z切BTO材料在槽波导配置中实现高效电光调制器是可行的,大部分光学模式被限制在110 nm厚的BTO层中。根据在脊形波导结构上测量的损耗和电光系数,以及模式重叠计算,基于这种结构的“推拉”MZI设备的Vπ·L值应该约为0.3 V·cm。

Dong及其同事最近展示了一种单片BTO马赫-曾德尔干涉仪,使用低损耗全BTO波导,光模式与非线性材料几乎完全重叠【55】。这些波导由500 nm厚的射频溅射a取向BTO(即X,Y切)制造,生长在SOI基底上,采用晶体-玻璃技术【56】。此外,他们还展示了单片BTO无源组件的制造,如输入/输出耦合器、渐变波导、Y分裂器、弯曲波导和直线波导,适用于通信C波段λ₀ ≈ 1535−1565 nm。

波导、渐变器和光栅耦合器通过EBL在Raith系统上图案化,使用未稀释的zep520a电子束光刻胶。电子束光刻胶作为蚀刻掩模,用于形成BTO波导和光栅耦合器。BTO通过离子铣削蚀刻,使用带有Ar+离子源的AJA离子铣削机。电极通过第二次EBL工艺使用PMMA-A4图案化。Cr/Au金属电极沿MZI的直臂图案化,间隙为8 μm,波导位于其间。间隙大小的选择是基于模拟,建议这样做可以最小化对波导损耗和折射率的影响。

图9.

(a) BTO马赫-曾德尔干涉仪的示意图,臂长为750 µm。BTO畴方向叠加在MZI的短臂上。

(b) 制造的BTO MZI的光学显微镜图像。

(c) 光栅耦合器的扫描电子显微镜图像,

(d) 波导弯曲、直臂和Cr/Au电极的扫描电子显微镜图像,

(e) 制造的MZI的直波导部分的扫描电子显微镜图像。

转载自文献【55】。

图9(a)显示了带有4种不同可能的BTO畴极化的MZI示意图,这些极化重叠在MZI的下臂上。该MZI是“非平衡的”;一条臂比另一条臂长100 μm。这允许在任何直流偏置(包括VDC = 0 V)下,通过调节信号激光器的波长来实现交流调制,这是平衡MZI无法做到的。图9(b)显示了制造好的MZI的光学显微镜图像,图9(c)-(e)显示了制造设备的不同组件的扫描电子显微镜图像:耦合光栅、波导弯曲和MZI臂以及直线波导。

使用的偏置T型接头的最大直流电压为±40 V,而上文讨论的前期研究【53】表明,需要大约三倍大的极化场来完全极化射频溅射的a轴BTO。这导致调制幅度的最大测量值为∼0.1015 rad/V,远低于此类设备可以实现的最大调制幅度。使用实验设置中可实现的最大相位变化值,所需电压以实现π相位变化为Vπ = 30.94 V。这对应于Vπ·L = 2.32 V·cm的电压-长度乘积,提取的有效泊克尔斯系数为reff = 89 pm/V。尽管测得的Vπ·L值不算高,但与最先进的LN基调制器相比仍具有竞争力。也许,这项工作的最重要发现之一是使用切割法测得的波导光损耗为3 dB/cm,即使在任何极化之前。

E. 剩余挑战

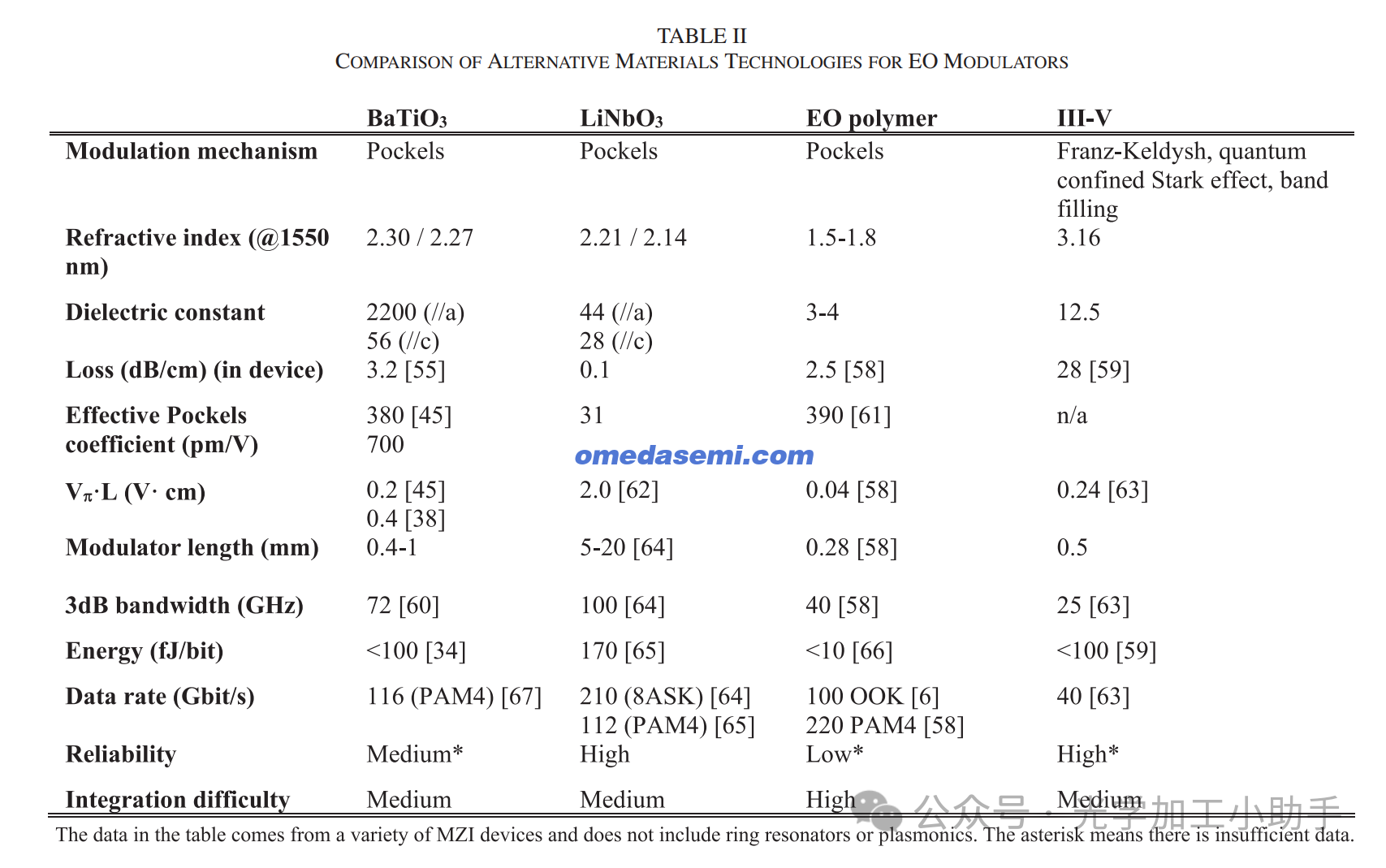

目前,基于硅的电光调制器正面临着未来硅光子学扩展的严重限制。目前,有四种替代技术有望实现高性能的硅集成电光(EO)调制器。它们是III-V族半导体、电光聚合物、LN和BTO【9】。虽然目前的III-V调制器受限于调制效率和带宽,聚合物受限于相对较低的可靠性和热稳定性,但硅集成单晶铁电材料,如LN和BTO,提供了紧凑的、高速的、低功耗、稳定的宽带调制,利用线性电光或泊克尔斯效应。它们能够支持几代集成电光调制器,在频率高于100 GHz的范围内工作,而对于BTO来说,其制造完全兼容现有的CMOS基础设施,使得这一材料尤为具有吸引力。表II列出了这些替代材料技术在电光调制器中的最佳报告关键参数。

然而,BTO仍然面临一些挑战。BTO波导中的光学损耗明显高于传统硅波导。这个损耗的物理来源尚不完全清楚,甚至很难区分固有材料损耗与波导制造过程中产生的损耗。因此,了解损耗机制的本质,并通过严格的物理分析将其与调制器性能关联起来至关重要。吸收损耗和非吸收或散射损耗都对总体光学损耗产生影响,并且从点缺陷到线缺陷,再到薄膜形态(堆垛故障、晶体学和铁电畴),都可能是导致损耗的原因。

为了缓解这个问题,可以将BTO的使用限制为仅作为相位调节器,使用不同的材料进行引导(例如,硅或SiNx)。这种混合方法将需要层转移或晶圆粘接。后者要求BTO层在整个晶圆上展示非常平滑的表面。初步结果是有希望的【49】, 但显然需要更多的工作。此外,晶圆级的应力管理仍然是一个挑战。BTO的热膨胀系数比硅大一个数量级,因此,冷却至室温时外延层中的热应力需要谨慎管理,以实现与光子应用兼容的形态。

另一个挑战是在BTO薄膜上极化,以便访问高泊克尔斯系数。因为BTO在硅上的制造是通过外延法进行的,且没有任何特殊的处理,BTO通常是随机极化的,这也部分导致了损耗。越能对齐铁电畴,设备的电光响应通常越强。目前,极化是针对每个器件单独进行的,而晶圆级的极化手段将是大规模生产所需要的。

最后,BTO的电光响应对温度的敏感性尚未经过彻底研究。已显示在低温下,电光响应显著抑制【48】,但目前尚不清楚在高温下电光响应的稳定性。已知四方晶体到立方晶体的过渡会在外延薄膜中向更高温度偏移【57】,但电光系数的变化尚未进行详细研究。

III. 结论

由于BTO强大的泊克尔斯效应能够大幅提升硅光子学(SiPh)调制器的性能,并以节能的方式实现这一点,因此将BTO集成到SiPh平台的推动力越来越大。将任何新材料集成到SiPh中总是具有挑战性的,并且需要大量的工艺开发,这会增加制造成本。幸运的是,BTO允许晶圆级集成,并且可以利用现有的新材料引入学习曲线,从而减少新材料平台的财务影响和技术复杂性。

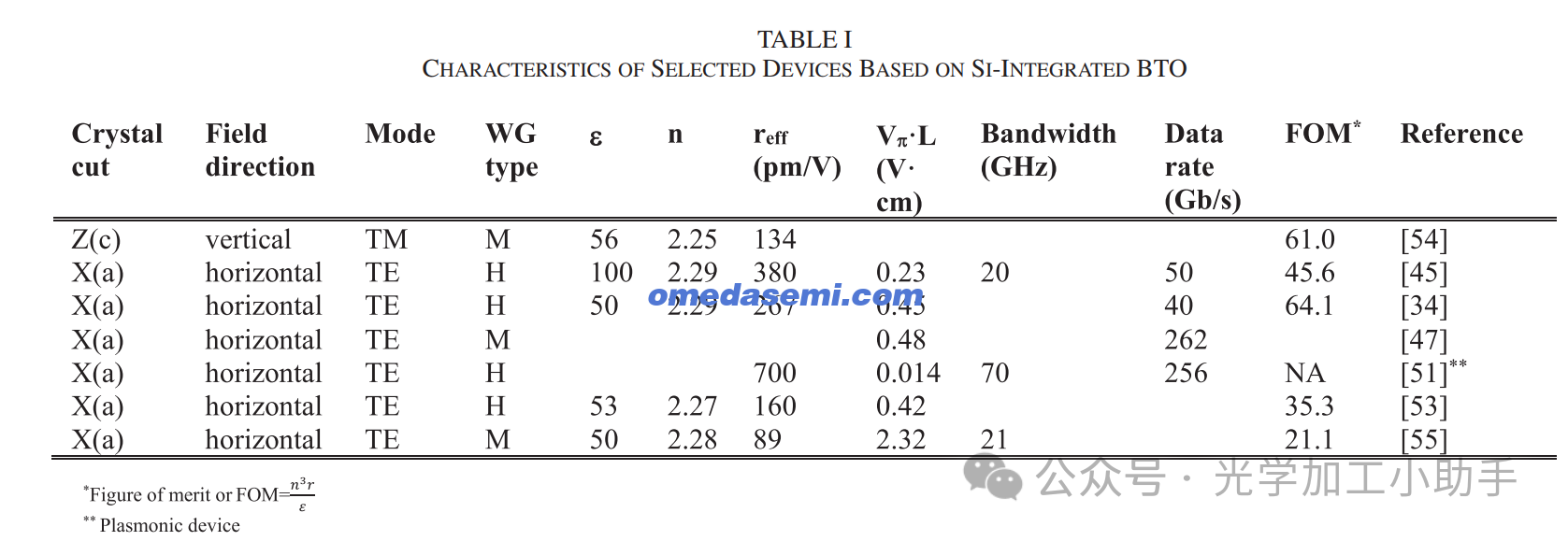

迄今为止,已经探索了使用TE和TM模式的混合波导和单片波导方法。BTO薄膜已在硅上集成了平面内(a取向薄膜)和垂直平面(c取向薄膜)铁电极化。结合这些选项创造了丰富的可能器件架构空间。此外,使用硅集成BTO的等离子体器件也得到了探索。总体而言,调制器表现非常有前景;损耗适中,约为1 dB/cm,Vπ·L最低已达到0.23 V·cm(在等离子体器件中为0.014 V·cm),带宽接近100 GHz,并且已实现超过250 Gb/s的数据传输速率。此外,硅集成BTO基器件展示了强大的低温性能。表I简要总结了BTO硅光子学技术的最新发展。这里的ε和n分别是材料的介电常数和折射率,如所引用的文献所报告。重要的是,这项技术完全兼容CMOS制造,并可在大面积晶圆上进行生产,因此适合低单价、大批量制造。

总之,基于BTO的集成电光调制器在过去十年中在技术成熟度上取得了巨大的进展,并且已经证明它们能够克服硅光子学等离子体色散调制器的带宽限制和功耗问题。这些进展使BTO硅光子学技术在未来成为数据中心和光互连应用(包括联合封装光学)以及未来光学量子计算和类脑计算平台的下一代电光调制器技术占据了有利地位。