摘要——本文研究了高电阻率衬底对22纳米FD-SOI射频(RF)和毫米波(mm-wave)器件及电路模块性能的影响。为此,在全球晶圆厂的22FDX®工艺节点上制造了关键器件,并在几种不同类型的衬底上进行了研究,从常规的1Ω·cm硅晶圆到超过10Ω·cm高电阻衬底。此外,还探索了几种硅界面条件,研究了衬底的界面电阻率变化对衬底体电阻率变化的影响。首先,通过使用CPW线和螺旋电感器研究衬底对无源结构的影响,并展示了使用改进的高电阻率(>10Ω·cm)衬底材料和钝化界面时,线性损耗和质量因子显著改善,与使用标准电阻率硅(1Ω·cm)的常规参考工艺相比。接下来,设计、制造并测量了几个关键的前端电路,以展示衬底对更高复杂度毫米波模块的影响,包括开关、低噪声放大器(LNA)和功率放大器(PA)。设计的DC-40GHz开关的插入损耗在采用高电阻衬底选项时测得改善了0.16dB。LNA演示电路在42至60GHz范围内工作,增益和噪声指数分别为11.5和1.99dB,在60GHz时,切换到低损耗衬底选项后,增益和噪声指数分别提高了+0.95dB和-0.28dB。最后,PA演示电路在24至40GHz范围内工作,参考标准衬底上的峰值附加功率效率为28.1%和输出功率为19.3dBm,在高电阻衬底上这些指标分别提高到29.9%和20.1dBm。该工作概述了主要毫米波无源和电路模块性能水平的提升,并展示了衬底对这些器件的主要性能指标在20-90GHz范围内的影响,改善幅度为0.16dB至1.13dB。

#全国产SOI晶圆定制加工 #468寸50nm-15um热氧片

库存片:

220nmSI高阻-3umSIO2-675umSI 6寸8寸 用于薄硅硅光

3000nmSI高阻-3umSIO2-675umSI 6寸8寸 用于厚硅硅光

#尺寸4-8寸

#最小起订量1片

#热氧层厚度范围50nm-15um

#膜厚精度最高精度+-5nm

#厚膜SOI-减薄抛光工艺600nm到微米级,加离子束精修,超级高精度膜厚均匀性

#CavitySOI-带空腔SOI晶圆,光刻显影刻蚀键合制作SOI一条龙

#FDSOI -最薄顶层10nm,特殊工艺精修,粗糙度小,膜厚精度高

普通超薄:SMARTCUT+离子束精修

超级超薄:EPI+SMARTCUT+离子束精修

#超平硅片-TTV500nm

我们为客户提供晶圆(硅晶圆,玻璃晶圆,SOI晶圆,GaAs,蓝宝石,碳化硅(导电,非绝缘),Ga2O3,金刚石,GaN(外延片/衬底)),镀膜(PVD,cvd,Ald,PLD)和材料(Au Cu Ag Pt Al Cr Ti Ni Sio2 Tio2 Ti3O5,Ta2O5,ZrO2,TiN,ALN,ZnO,HfO2。。更多材料),键合(石英石英键合,蓝宝石蓝宝石键合)光刻,高精度掩模版,外延,掺杂,6寸DUVKRF电子束光刻等产品及加工服务(请找小编领取我们晶圆标品库存列表,为您的科学实验加速。

请联系小编免费获取原文

文章名:Impact of a High-resistivity Substrate on RF and mm-wave Performance of 22 nm FD-SOI Devices and Circuits作者:Martin Rack, Lucas Nyssens, Massinissa Nabet, Dimitri Lederer, and Jean-Pierre Raskin单位:Université catholique de Louvain (UCLouvain), 1348 Louvain-la-Neuve, BelgiumI. 引言

如今,先进的CMOS节点在射频(RF)和毫米波应用中具有竞争力。特别是,全耗尽(FD)-SOI器件在300-400 GHz范围内具有f_t和f_max指标,并支持最多11层金属层的丰富后端线路(BEOL)选项,包括支持高Q值RF/毫米波无源组件和互连的几层厚铜层。

硅基底是这些无源组件和器件电磁环境的一部分,如果硅电阻率较低,它可能会导致显著的损耗、耦合和非线性信号失真【2】。

使用高电阻率(HR)硅基底(名义电阻率ρ_nom > 500 Ω·cm)而非标准掺杂硅(ρ_nom 10至20 Ω·cm)可以改善这些效应,尽管这些好处受到寄生表面导电(PSC)效应的影响。PSC层由位于Si/SiO2界面的固定正电荷引起,这些正电荷吸引大量自由电子,形成一个高度导电的薄层【3,4】。因此,PSC降低了基底上感知到的有效电阻率(ρ_eff)。由于这些原因,基底的电阻率通常仅在30-150 Ω·cm范围内【2, 5】。

为了解决PSC问题,已经开发了界面钝化解决方案,其中最广泛应用的是富陷阱层解决方案,该方案在SiO2和Si之间引入一层薄的多晶硅,富含缺陷,能够捕获自由载流子并使界面具有电阻性【4,5,6】。富陷阱SOI在部分耗尽(PD)-SOI节点中取得了显著的工业成功。然而,FD-SOI支持低于BOX的特性(如背门接触、隔离井、二极管等),这些特性在富缺陷的多晶硅中难以集成。因此,兼容性问题促使了替代界面钝化方案的发展。

基于这些原因,本文将特别研究应用于FD-SOI的新型PN界面钝化技术。

本文研究了基底及其界面钝化性能对毫米波设备性能指标的影响。此研究使用了GlobalFoundries的22nm FD-SOI节点,所设计的电路均在不同的基底选项上进行制造和测试,基底选项从标准电阻硅晶片到高电阻率硅,并探索了不同的界面钝化解决方案。

首先,介绍了基底对关键无源元件的影响,如共面波导(CPW)传输线和螺旋电感器。然后,描述了基底对关键毫米波前端电路模块的影响。具体而言,通过测量数据支持的研究,探讨了基底对(i)DC-40 GHz开关的插入损耗、(ii)24-43 GHz功率放大器(PA)设计的饱和输出功率和功率附加效率(PAE)以及(iii)42-67 GHz低噪声放大器(LNA)的噪声系数(NF)和增益的影响。

在这项工作中,GlobalFoundries的22FDX®技术在几种不同类型的FD-SOI晶片(p型)上进行处理,并且这些晶片具有不同的硅基电阻率值。此外,考虑了三种不同的界面变化:(i)默认,即记录工艺(POR)界面,(ii)增强界面,以及(iii)PN界面钝化技术。这些不同的选项不属于GlobalFoundries的标准技术产品,而是独特的探索性工艺的一部分。

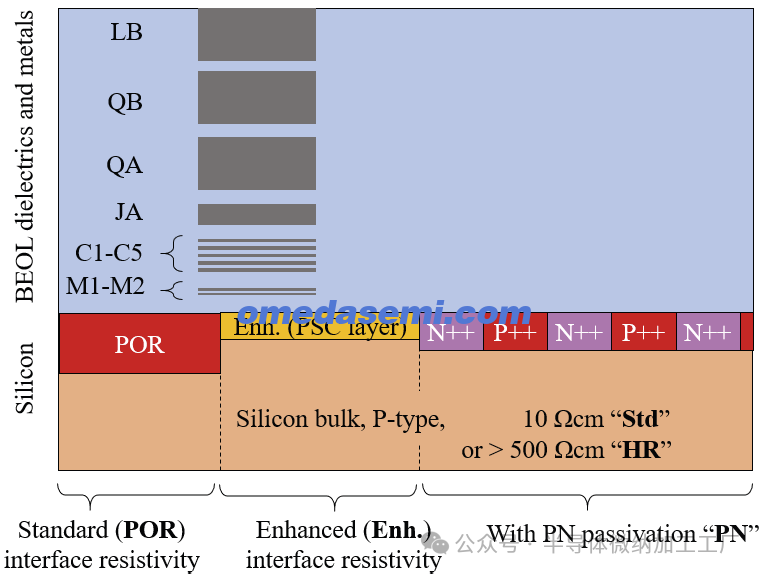

图1. 不同基底选项(在体材料和界面处)以及上方BEOL金属堆栈的示意图。

这些六种不同的基底选项(两种界面选项和四种基底电阻率选项)在图1中进行了展示,并附有该技术后端(BEOL)堆栈的示意图。在“增强界面”中,特别注意避免任何局部杂质,因此在这种情况下,任何存在的导电区域都与固定界面电荷引起的PSC效应相关。PN结基底的概念首次在[7,8]中提出并解释,它实现了P型和N型掺杂交替的区域,通过诱导的耗尽结中断了原本的导电界面(PSC效应),这些耗尽区的串联组合结果是整体基底阻抗(ρeff)的显著增加,从而提高了与共面电路连接的有效电阻。这些耗尽区由于本身是高电阻的,因此有助于增加Si/SiO2界面的有效电阻率。

本章节进一步补充了关于PN界面钝化的研究,作为首次展示其对完整FEM电路模块的影响和益处的工作,包括宽带单极双掷(SPDT)开关、42-67 GHz LNA和24-43 GHz PA,所有这些模块都在22nm FD-SOI中设计。

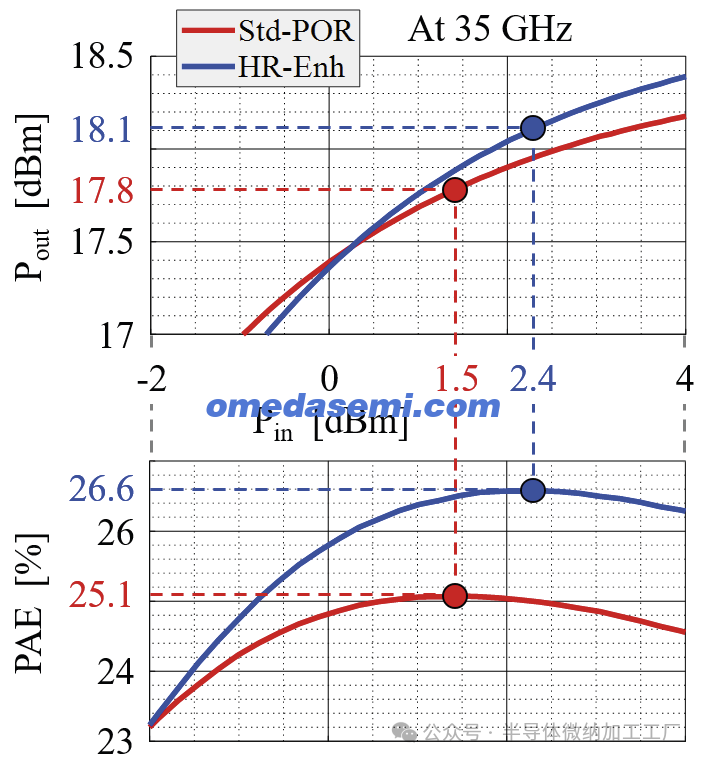

本章节的结构如下。首先,在第2节中,描述了本研究中使用的不同基底选项。在第3节中,报告了基底选项对实现最上层铜金属层QB的共面波导设计损耗的影响。通过测量数据提取了这些线路所感知的有效电阻率,并为不同晶片的实际体电阻率和界面钝化质量提供了强有力的见解。在第4节中,展示了螺旋电感器的结果,这些电感器也在QB金属层中实现,并展示了基底对其质量因子的影响。第5节讨论了基底对毫米波DC-40 GHz单极双掷(SPDT)开关的性能指标的影响,主要影响体现在观察到的插入损耗上。通过测量和仿真数据证明,简单地修改SPDT下方基底的有效属性,可以将30 GHz时的插入损耗从2.10 dB改善到1.75 dB。第6节研究了基底对42-67 GHz LNA的影响,并展示了在55 GHz时,使用高电阻基底相比于参考标准电阻基底,增益增加了0.95 dB,噪声系数降低了0.25 dB。最后,第7节展示了基底对24-43 GHz功率放大器设计的影响,观察到放大器的峰值功率附加效率(PAE)从25.1%增加到26.6%,同时输出功率在最大PAE点增加了0.3 dB。

总体来说,在这种多样化的毫米波集成电路中,观察到了显著的增益,并在第8节的结论中回顾了基底对所有这些电路的影响。

II. 22FDX® 基底变体

图1显示了本研究中使用的六种基底变体,CPW线路和毫米波FEM是基于这些基底制造的。在Si/SiO2界面,考虑了三种不同的选项:

• POR:这是22FDX®工艺中的标准记录过程(POR)选项,界面电阻率在该参考工艺的某些步骤中设置。此界面选项将从此称为“POR”。

• 增强型(Enhanced):在此选项中,对上述参考工艺进行了优化,以获得一个导电性较低的界面。在这种情况下,仍然存在相当导电的PSC效应,但其导电性低于POR选项。这一界面选项将从此称为“Enh”。

• PN钝化(With PN passivation):在此选项中,采用增强型工艺(而非POR),并在此基础上,在射频(RF)器件下方定义交替排列的P++和N++掺杂区域。这些区域通过植入工艺步骤定义,使用与此FD-SOI技术的背门井定义相同的植入参数(杂质、能量和剂量)。此外,已包含芯片上的互连,以提供PN结的直流偏置。如果没有对PN结应用直流偏置,则此界面选项将标记为“PN”;如果对PN结施加3V反向偏置,则标记为“PN3V”。

在实际操作中,通过在芯片上实现的大值多晶硅电阻器为每个P区和N区施加直流偏置。关键在于,通过对PN结施加反向偏置,可以扩展耗尽区,由于这些区域主导了薄片阻抗,因此增加了界面的有效薄片电阻率。以上三种界面选项均已在22FDX®工艺线中的两种基底晶圆上实现和制造:

• 标准电阻率(Standard resistivity):此块硅的电阻率范围为10–20Ω·cm。该基底选项目前是22FDX®工艺线中的参考工艺的一部分,将从此称为“Std”。

• 高电阻率(High resistivity):使用此选项,块硅的电阻率范围为500–1000Ω·cm。此基底将从此称为“HR”。

III. 基底对CPW线路的影响

图1展示了本文研究中所考虑的器件的BEOL(后端金属层)中的金属层。它包括七层薄铜层(厚度范围为100 nm),分别为M1、M2层以及C1到C5层。在这些层的上方是一个1 µm厚的铜JA层,接着是两层3 µm厚的铜QA和QB层。最后,技术层由一个2.9 µm厚的铝LB层覆盖。

在厚的高层金属QB中制造了一组CPW线路,展示了在不同基底上CPW线路损耗方面能够实现的典型高性能。为了实现50Ω的特征阻抗(Zc),设置了中央信号线的宽度(Wc)为35 µm,外部接地线与信号线之间的间距(S)为20 µm。

测量了两种不同长度的线路(760 µm和2000 µm),以及专用的Thru结构(总长度290 µm)和Open结构。

这些制造的CPW线路在芯片上使用FormFactor公司的100 µm间距的GSG探针和Keysight公司的PNA-X分析仪进行测试,频率范围达到67 GHz。根据[9]中描述的提取程序,去嵌入了垫片的寄生效应,并采用mTRL方法提取了均匀线路的属性,如传播常数和特征阻抗的实部和虚部,最终得出等效线路的RLGC参数。

在提取这些数据之后,比较了不同基底上的CPW线路的线路损耗(α)和基底有效电阻率(ρeff)。后者通过CPW几何形状的共形映射技术计算【10】,如[9]中详细说明。

图2. 不同基底选项上测量的CPW线路(QB金属层)中的有效电阻率(ρeff)和线路损耗(α)。

图2提供了QB CPW线路的提取数据。绘制的曲线突出显示了基底对CPW线路整体性能的影响,在Std-POR基底上,30 GHz时的损耗为1.00 dB·mm。

通过对比不同基底选项,实验结果表明,通过增强界面电阻率过程,与POR参考工艺相比,线路的损耗已大幅度降低。例如,在Std-Enh基底上,CPW线路在30 GHz时的损耗为0.75 dB·mm。这种降低可以通过线路感知到的更高的有效电阻率来解释,界面电阻率从35 Ω·cm增加到47 Ω·cm,原因是界面变得不那么导电。

在HR基底上,HR-POR样品上的线路在30 GHz时的损耗为0.54 dB·mm。与Std-POR基底相比,仅通过修改基片的基础电阻率,损耗降低了0.46 dB·mm,有效电阻率从35 Ω·cm增加到78 Ω·cm。通过使用增强界面工艺选项,损耗进一步降低,HR-Enh样品上的线路在30 GHz时的损耗为0.25 dB·mm,有效电阻率为196 Ω·cm。在这种情况下,界面电阻率由Si/SiO2界面上的PSC效应决定,它主导了线路参数中的G项。通过利用PN结钝化技术,可以进一步增加界面电阻率。这通过在HR-PN样品上的CPW线路的进一步损耗减少到0.18 dB·mm得到验证。

在测量的G和ρeff数据中观察到频率依赖性,这是由导电掺杂区域(N型或P型)与电容性耗尽区域的串联组合引起的。通过反向偏置PN结,可以扩展耗尽区的空间。这会增加界面阻抗并进一步减少线路损耗,正如HR-PN3V标记的CPW数据所示。这些线路与HR-PN线路相同,只是在PN模式上增加了3 V的偏置。

总体而言,在HR-PN和HR-PN3V样品上的线路在30 GHz时的ρeff值分别为360和457 Ω·cm,线路损耗分别为0.18和0.15 dB·mm。仿真结果与测量数据非常吻合,并显示出30 GHz时的线路损耗中有0.13 dB·mm来自于QB层的有限金属电阻,这意味着在HR-PN3V基底上的基底损耗贡献非常低,约为0.02 dB·mm,确认了在这种情况下基底钝化的优异性能。

IV. 基板对螺旋电感的影响

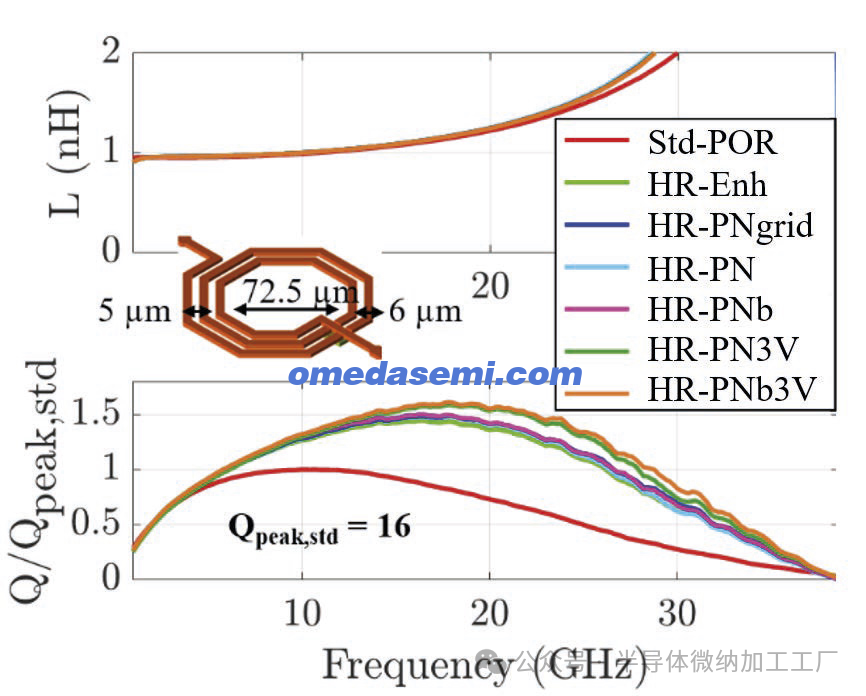

图3. 在不同基板上,具有或不具有界面钝化的5–20 GHz电感器的电感(L)和归一化品质因数(Q)。

本文中,1nH的螺旋电感器在不同基板选项上实现,并从100 MHz到67 GHz进行了测量。电感(L)和品质因数(Q)通过以下公式计算:

L = Im(1/Y11)/Ʒ 和 Q = Im(1/Y11)/Re(1/Y11)。图3显示了在几个基板上1nH电感器的电感和品质因数。

选择用于展示基板影响的电感器在QB层中实现了2.5圈,内径为72.5µm,线圈宽度为6µm,线圈间距为5µm。图3中的插图突出显示了这些尺寸。

这些电感器在上述相同的基板上制造,包括有和没有电阻性基底选项,以及几种界面钝化解决方案的选项。与CPW线路下的PN图案相同(在图3中标记为“-PN”),但在这些电感器下还研究了其他类型的PN图案形状,包括使用不同几何形状的阵列(在图3中标记为“-PNb”)和网格阵列(标记为“-PNgrid”)。这些结果已在[11]中报告,感兴趣的读者可以在该文献中找到有关PN植入的详细信息。

图3中的品质因数是通过标准POR基板上的Q峰值(Qpeak,std = 16)进行归一化的。

随着基底电阻率的提高,从标准基板到高电阻增强基板(HR-Enh)的质量因数大大改善。实际上,Q峰值大约提高了1.5倍(从16到24),并且转移到了更高的频率。通过施加3V反向偏置的PN结,进一步提高了品质因数(从24到26),这显著增加了基板的电阻。

V. 基板对毫米波DC-40 GHz SPDT模块设计的影响

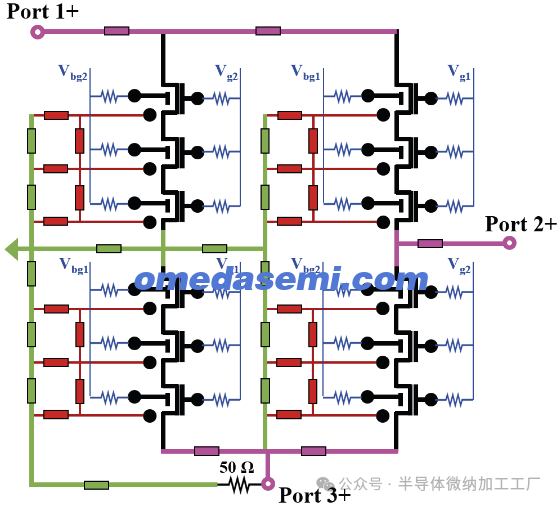

图 4. 毫米波SPDT开关设计。

在22FDX®工艺中,使用与CPW线路相同的Std和HR硅片设计并制造了一个DC-40 GHz SPDT模块。为了获得宽带性能,选择了经典的串联-并联拓扑结构,其布局和原理图如图4所示。该设计采用了20 nm栅长超低阈值电压(SLVT)晶体管,并包括背栅接触,以提供该技术中的最低RonC。

在开关的每个分支中,三个FET串联堆叠以实现接近20 dBm的P1dB。之后,FET的尺寸被调整,以在保持优于20 dB隔离(ISO)的同时,尽可能降低插入损耗(IL),并在DC到40 GHz的频率范围内保持良好的性能。

通过这种设计方法,串联分支中的晶体管宽度被确定为150 µm,旁支分支中的晶体管宽度为33 µm。所有FET都是多指型设备,指宽为3 µm,并通过芯片上的10 kΩ电阻器对前栅和背栅进行偏置。开关的四个DC控制电压,如图4所示,在开启状态时连接端口1和端口2,分别为Vg1、Vbg1、Vg2和Vbg2。开启时,这四个电压设置为0.9 V、3 V、–0.9 V和0 V。在关闭状态下,连接端口1和端口3(并隔离端口1与端口2),这四个电压设置为–0.9 V、0 V、0.9 V和3 V。

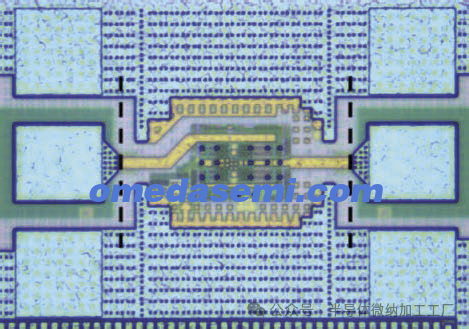

图5.已制造的SPDT模块的显微照片。开路去嵌入后的测量参考平面显示为虚线。

最后,端口3使用集成的精密50 Ω负载在晶圆上实现。图5给出了制造的DC-40 GHz SPDT模块的微观照片。

开关FoM的基板影响测量

在每个基板上实现的SPDT开关都进行了测量和完整的仿真,参考平面设置在GSG探针垫上。对完整的SPDT进行开路垫去嵌入程序,测量(仿真)的开路垫结构的矩阵从测量(仿真)完整SPDT的矩阵中减去。

图6. 所有基板上SPDT的测量和仿真S21参数(开路去嵌入),作为频率的函数,分别显示了开关的开通状态和关断状态。

结果数据然后绘制在图6中,显示了开关在开关状态和关断状态下的S参数结果,测试频率高达60 GHz。

开关满足设计规格,在40 GHz以下提供超过20 dB的隔离(S21 OFF)。在开通状态下,Std-POR基板上的开关在30 GHz时表现出2.10 dB的插入损耗。通过增强界面电阻率(Std-Enh),插入损耗可以改善至1.97 dB。通过同时增强界面特性并增加基体电阻率,HR-Enh样品的插入损耗进一步改善至1.86 dB。在此基础上,添加PN结钝化方案将30 GHz的损耗进一步减少到1.80 dB(HR-PN),通过施加3 V的反向结偏置(HR-PN3V),插入损耗可以降低至1.75 dB。

图7. 在不同基板选项上的测量和仿真SPDT插入损耗(开路去嵌入)。

图7展示了通过增加基板阻抗对插入损耗的改善。总体而言,开关在30 GHz时的插入损耗提高了0.35 dB,分别在10 GHz、20 GHz和30 GHz时提供了0.87、1.24和1.75 dB的损耗值。这一改善得益于通过高电阻率基体和优化界面特性组合,增加了基板网络寄生电阻(通过[12, 13]中的仿真分析显示,寄生电阻会降低FD-SOI技术中的开关性能)。

VI. 基板对毫米波42-67 GHz LNA的影响

LNA设计

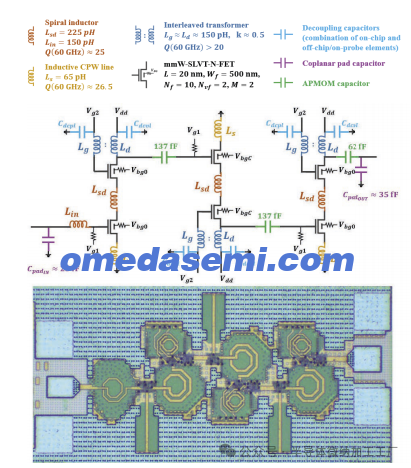

图8. 三级低噪声放大器(LNA)设计原理图和制备电路的显微照片。

图8展示了三阶段LNA的整体电路图和核心布局。LNA设计包含三阶段,每个阶段都是级联拓扑结构,使用退化源电感(Ls和Ld)。多级级联架构的选择旨在实现高增益,同时在此技术中保持低功耗,且使用变压器负载技术来提升增益,并在增益和带宽之间进行权衡【14】。

LNA中的所有晶体管都是20纳米门长的SLVT N-FET,并且它们的尺寸为500纳米的栅宽,这在最小噪声系数(NFmin)和可用增益之间提供了良好的权衡。每个晶体管由四个宽度为5微米的晶体管单元组成,使用10个指尖,并在每个FET上施加0.8V的源-漏电压(Vds)和4.2mA的电流(每阶段对应的Vdd为1.6V)。每个器件中的电流密度为0.21mA/μm,这是最小噪声系数性能下的典型值。

在输入匹配阶段,采用了退化电感Ls,以帮助稳定放大阶段,并调整第一级输入阻抗,使得输入网络可以通过一个单一的串联螺旋电感Lin实现匹配。这个方法最小化了输入匹配网络对LNA总体噪声系数的影响。

在每个放大阶段,Lsd 电感被放置在共源(CS)和共栅(CG)晶体管之间,用以共振去除这些场效应晶体管(FETs)之间节点的电容寄生,并抑制CG晶体管的噪声贡献。

在CG器件的漏极节点上包含了 Ld 电感,用以共振去除漏电容并增强增益,同时在栅极节点上包含了 Lg 电感,以提高每个级联阶段的增益。然而,大值的 Lg 电感倾向于使得 CG 阶段不稳定,但可以通过引入 Lg 和 Ld 之间的耦合来补偿这一点【15】。在设计过程中,Lg 被引入以提升增益,随后通过引入耦合来保证稳定性。此外,Lg 和 Ld 的耦合因子可以调节,以在单一频率下实现增益的峰值,或者实现增益的更平坦的宽带响应【15】。在本工作中,发现使用 150 pH 的 Lg 和 Ld 以及 0.5 的耦合因子之间,可以为放大器实现宽带响应,从 42 GHz 到 67 GHz。

LNA 性能的基板影响测量

使用两种不同的设置对制造的 LNA 进行片上测量。对于噪声因子表征,采用了 Keysight 的 2 Hz 到 110 GHz 的 N9041B UXA 信号分析仪,并配合 60 GHz 的噪声源。对于增益测量,使用了 Keysight 的 500 Hz 到 125 GHz 的 N5291A 向量网络分析仪。

LNA 使用两个六针 DC 探头进行偏置,这些探头以 90° 的配置放置在 RF 探头的南北位置,通过专用的 DC 针脚进行连接。这些探头包含去耦电容,与片上集成的去耦元件共同作用,确保 LNA 的 Vdd 针脚和 GND 针脚之间实现宽带去耦。在此配置下,LNA 的所有阶段在宽带范围内无条件稳定(从 DC 到 110 GHz 已验证)。

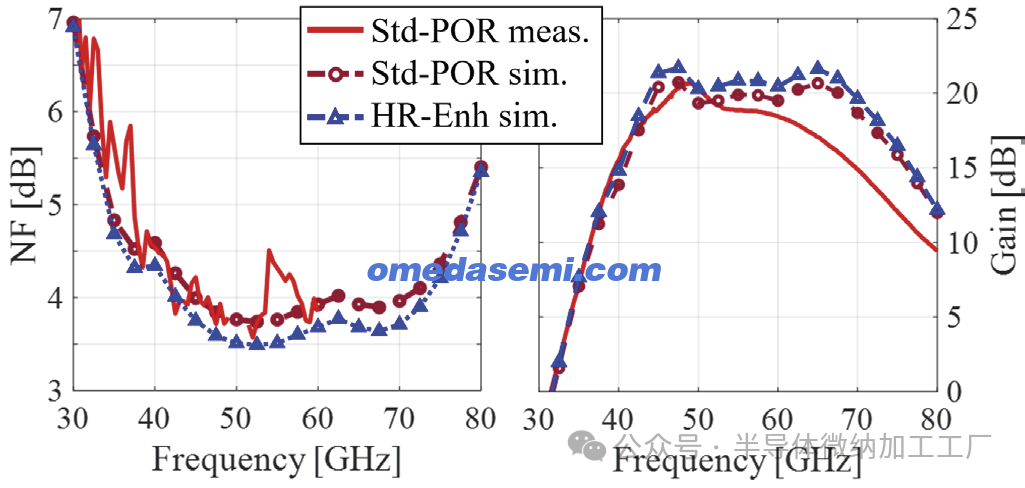

图 9. 测量和仿真性能 - 噪声因子和增益 - 在不同基板选项上制造的设计 LNA。

S 参数和噪声因子测量结果如图 9 所示,在标称偏置条件下进行。根据该偏置条件,三阶段 LNA 的直流功耗为 12.5 mW。测量结果表明,LNA 在 42 到 67 GHz 范围内具有宽带工作性能。在 Std-POR 基板上,LNA 达到了 20.5 dB 的峰值增益,并且噪声因子最小值为 3.7 dB。

仿真结果预测,通过将 LNA 设计转移到更高电阻率的基板上,噪声因子可以降低 0.25 dB,增益可提高 0.95 dB。噪声因子的改善主要归因于输入匹配网络中的损耗减少(主要是在电感 Lin 中),而增益的增加则归因于整个 LNA 的被动元件的损耗减少(主要是所有螺旋电感元件,它们在质量因子方面有显著改善,如第 4 节中讨论和强调)。

VII. 基板对24–43 GHz毫米波功率放大器(PA)的影响

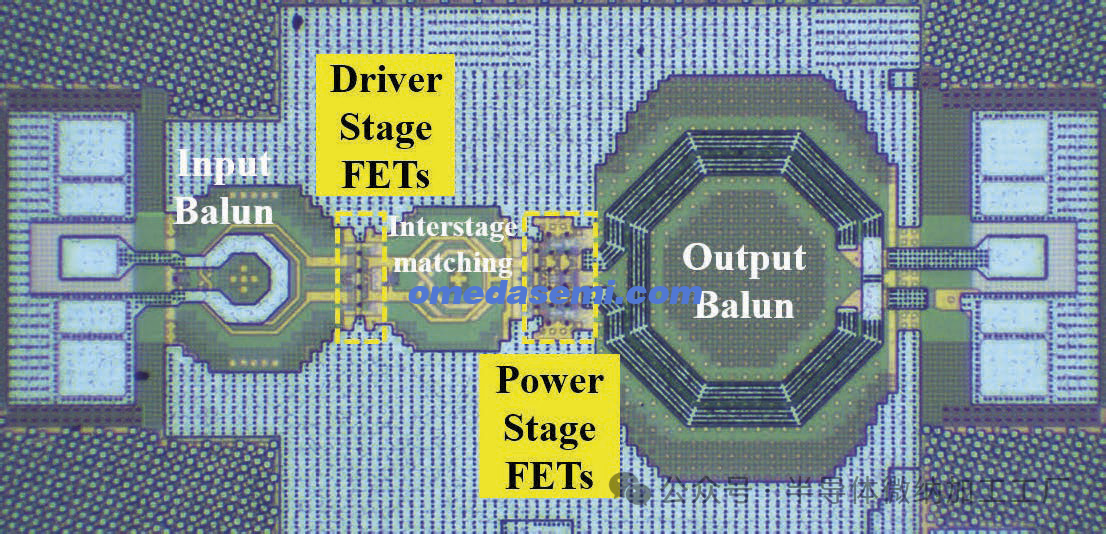

作为PA示范设计,选择了基于分布式输出平衡器的平衡差分多级拓扑结构【16】,以在n257-260频段实现宽带性能和高输出功率。对于VSWR方面,平衡拓扑结构对负载变化具有固有的鲁棒性,并能够增加输出功率【17】。

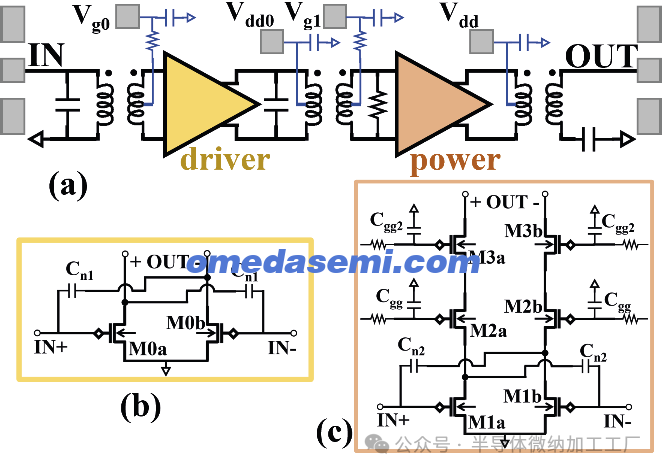

图10. PA1的电路原理图 (a),驱动级 (b) 和功率级 (c)。

所设计的PA依赖于三堆叠FET输出级与分布式平衡器,覆盖24–43 GHz频段。该PA基于伪差分两级配置,电路原理图如图10所示。功率(第二)级使用三堆叠FET差分架构【18】,而驱动(第一)级没有FET堆叠。它们的电路原理图分别显示在图10b和10c中。两级都使用交叉耦合中和电容来稳定差分工作放大器【19】。单端到差分(及其反向)转换通过输入和输出平衡器进行,这些平衡器还实现了所需的阻抗匹配。

一个级间变压器将功率级的输入阻抗转换为驱动级所需的阻抗,以实现最佳的大信号性能。栅极和漏极偏置通过变压器的中心抽头提供给晶体管,如图10a所示。为了提高共模操作的稳定性,在栅极偏置线中添加了大值偏置电阻【19】。所有FET的背栅端子通过大偏置电阻连接到直流垫,以解耦RF和DC操作(图10中未显示)。

功率级设计

输出级使用了nMOSFET超低阈值电压,门长为20nm,所有FET的总宽度为160µm。20nm的门长在高RF性能(截止频率、fₜ和最大振荡频率fₘₐₓ)与可靠性之间实现了良好的折衷,因为其击穿电压并不显著低于其他子30nm门长的FET【1】。总FET宽度在高输出功率(Pout)与宽带输入阻抗变换之间取得了折衷。通过FET级的阶梯型互连,减少了布局寄生效应,以降低电阻性和电抗性元件,从而减少损耗、相位失配,并简化输入/输出阻抗匹配,同时满足电迁移规则。

Vdd偏置电压设置为2.4V,以提供此技术的名义DC电压。每个FET的Vds为0.8V,Vgs选择为0.3V,作为中到高功率操作中第三次谐波电平显著降低的折衷(CMOS基PAs偏置接近B类操作时会有线性区的甜点)和mm-wave频率下所需的增益。背栅电压(Vbg)会改变阈值电压(Vth),Vbg为0V时在此设计中固定(Vgs = 0.3V),但每个FET的背栅端子可以用于补偿Vth工艺变化(Vbg的范围为-240至+40mV,分别对应Vbg = -0.5V至3V)。

驱动级的设计与功率级相似,但采用了仅共源FET,宽度为80µm(为功率级宽度的一半)。

输出巴伦设计

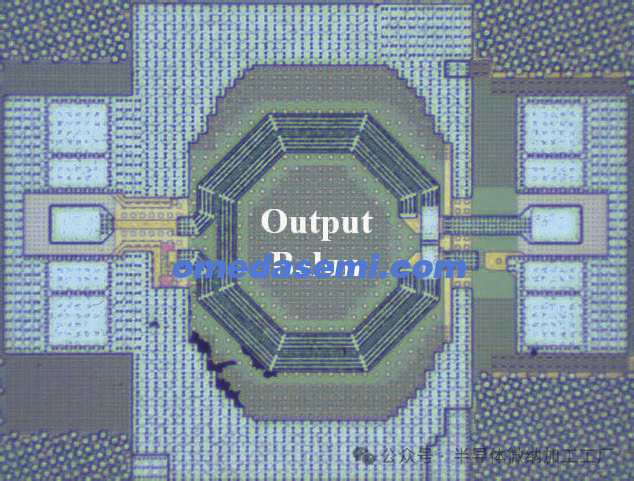

图11. 制造的独立输出巴伦的显微照片。

输出级的负载拉取仿真显示,一个由45.5欧姆和74fF并联组成的等效阻抗(对于每个分支)最大化了输出级的大信号性能,并且在宽带范围内达到最佳负载阻抗。输出巴伦基于耦合传输线元件设计,采用与[16]类似的方法,以准确描述宽带行为。结果是分布式巴伦被集成为一个独立结构,用于彻底的特性化,该被动器件的显微照片如图11所示。

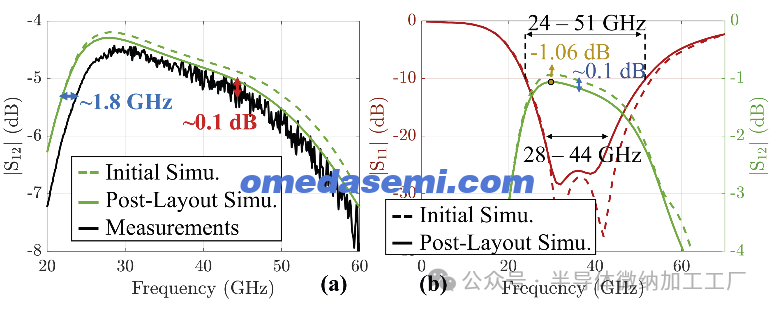

图12.(a) 在Std-POR上,独立输出巴伦的模拟(绿色)和测量(黑色)。

(b) 在Std-POR上,输出匹配网络的模拟。

图12展示了与初始和后布局仿真结果的测量,拟合独立分布式巴伦的测量结果。图12b显示了输出匹配网络作为PA集成后的仿真性能(包括输出RF焊盘)。

在24–45 GHz的整个频段内,超宽带阻抗变换得到了良好的实现。在Std-POR衬底上,该输出匹配网络的插入损耗在该频段内为1–1.5 dB。

图13. 完整的两级功率放大器设计的显微照片。

图14. 在不同基板选项上制造的设计功率放大器(PA)的测量性能——输出功率(Pout)和功率附加效率(PAE)。

图13显示了完整的两级功率放大器(PA)的显微照片。该功率放大器在24 GHz到43 GHz的所有频率范围内,在大信号连续波测量条件下进行了片上表征,结果在图14中以35 GHz为例进行了绘制。结果表明,通过将PA设计迁移到更高电阻率的基板上,峰值功率附加效率(PAE)从25.1%提高到26.6%,且在峰值PAE时输出功率从17.8 dBm增加到18.1 dBm。

VIII. 结论

表1

基板对研究的毫米波设备主要性能指标的影响

本文介绍了基板特性对各种毫米波被动和主动电路性能的影响。所涉及的器件包括CPW传输线、螺旋电感器、DC-40 GHz SPDT开关、42–67 GHz低噪声放大器(LNA)和24–43 GHz功率放大器(PA),这些器件都在GlobalFoundries的22 nm FD-SOI节点上设计并制造,采用了多种基板,包括标准(低)和高体电阻的硅片,并配备了多种界面钝化选项。主要结果总结在表1中,并强调了这些器件在其覆盖的20–60 GHz频段内,关键指标上大约为0.3–1.0 dB的性能提升。通过将10 Ω·cm基板材料替换为具有适当界面钝化的高电阻(>500 Ω·cm)硅体,展示了以下器件指标的提升:

(i) CPW线的线性损耗从30 GHz时的1.00 dB/mm(60 GHz时1.26 dB/mm)改善为0.15 dB/mm(0.29 dB/mm)。

(ii) 20 GHz螺旋电感的峰值品质因子从16.0提高到24.5。

(iii) 宽带DC-40 GHz SPDT开关模块的插入损耗从30 GHz时的2.10 dB降低到1.75 dB。

(iv) 三级42–67 GHz LNA设计(共源拓扑,基于变压器的增益提升负载)的增益和噪声系数分别从19.90 dB和3.76 dB提高到20.85 dB和3.51 dB(在55 GHz时)。

(v) 宽带差分双级24–43 GHz PA的峰值功率附加效率和峰值输出功率在35 GHz时分别从25.1%和17.8 dBm提高到26.6%和18.1 dBm。