#FinFET器件 #soi晶圆 #Cavitysoi晶圆 #FDSOI晶圆 #厚膜SOI晶圆 #热氧化硅片摘要

演示了使用顶层FD-SOI器件和底层大块FinFET器件的3D顺序堆叠。通过功能性3D通孔链、3D CMOS单反相器以及由顶层和底层晶体管构建的反相器链,验证了3D集成和上下层互连。研究并比较了三种不同的硅层转移流程,包括低温Smart CutTM,针对顶层平面器件进行电气性能比较。展示了双轴拉伸硅的转移,顶层nMOS器件相比未拉伸硅器件有60-80%的性能提升。进一步优化低温Smart CutTM转移流程,使顶层器件的电子和孔迁移率得到了显著恢复。还研究了堆叠对底层FinFET器件的影响,针对不同的底栅堆叠进行研究。

引言:

3D堆叠CMOS晶体管为进一步扩展标准单元和SRAM缩放提供了机会,使其成为延续摩尔定律的有前景的晶体管架构。其与异质共集成通道材料和器件架构的兼容性,使其在超越摩尔的应用中也非常有吸引力【1】。3D顺序堆叠依赖于通过粘接将单晶材料层转移到底层处理过的器件上,然后再进行顶层制造。为了避免底层结构的退化,顶层器件的整体热预算以及层转移处理需要保持较低,通常低于500˚C。我们展示了具有顶层平面器件和底层大块FinFET的3D堆叠器件,并进行了电气互连层验证。研究了三种不同的低温层转移工艺,比较了转移层的材料和电气性能。我们还展示了通过优化低温Smart CutTM转移工艺条件,可以显著恢复迁移率损失【2】。最后,我们研究了堆叠对底层器件的电气影响。

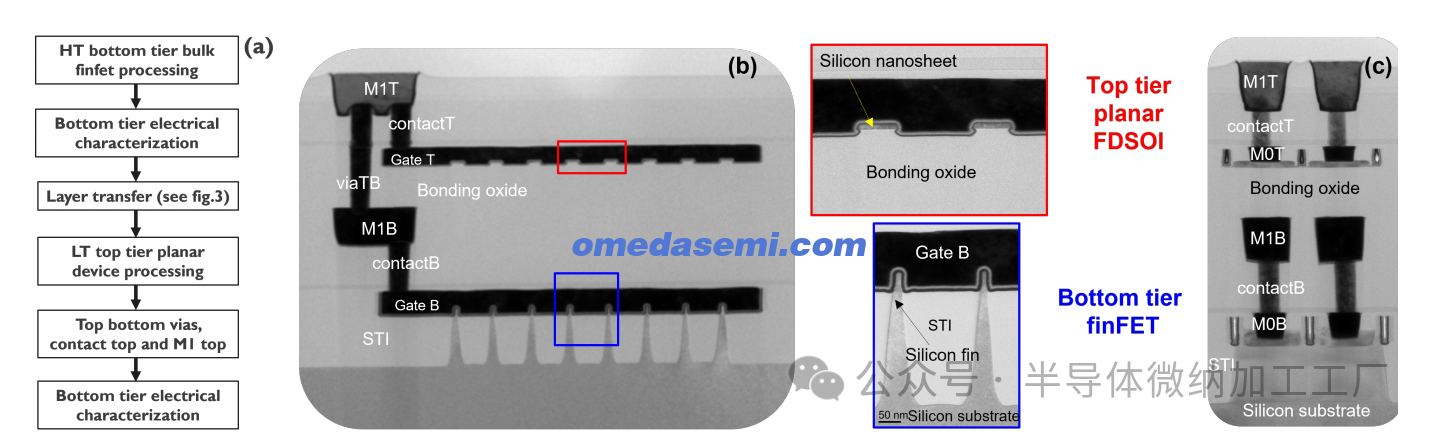

图1. (a) 3D工艺流程示意图与3D顺序堆叠器件的TEM横截面 (b) 沿栅极方向 (c) 横跨栅极方向

3D堆叠演示:图1展示了3D顺序工艺流程和最终堆叠器件及互连的TEM图像。

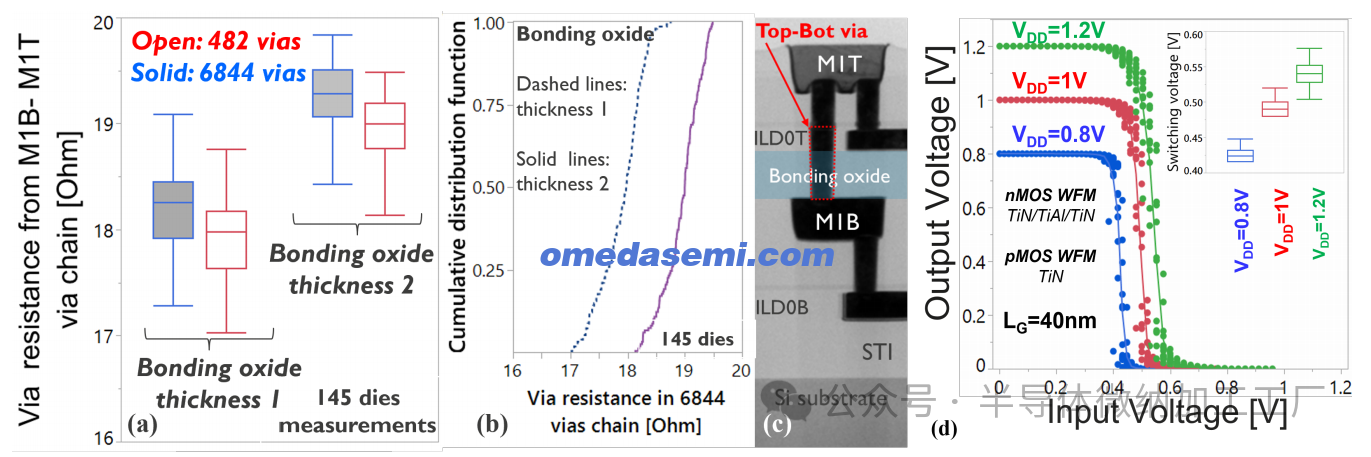

图 2. 层间 M1T-M1B 过孔链(a)电阻、(b)CDF、(c)TEM 和(d)3D CMOS 逆变器的电压传输曲线和提取的开关电压。

通过大尺寸的上下通孔链功能(图2a-c),以及使用顶层nMOS平面器件和底层pMOS FinFET制造的功能性单反相器(图2d)和81级反相器链,验证了层间的电气互连的良好产率和可重复性。

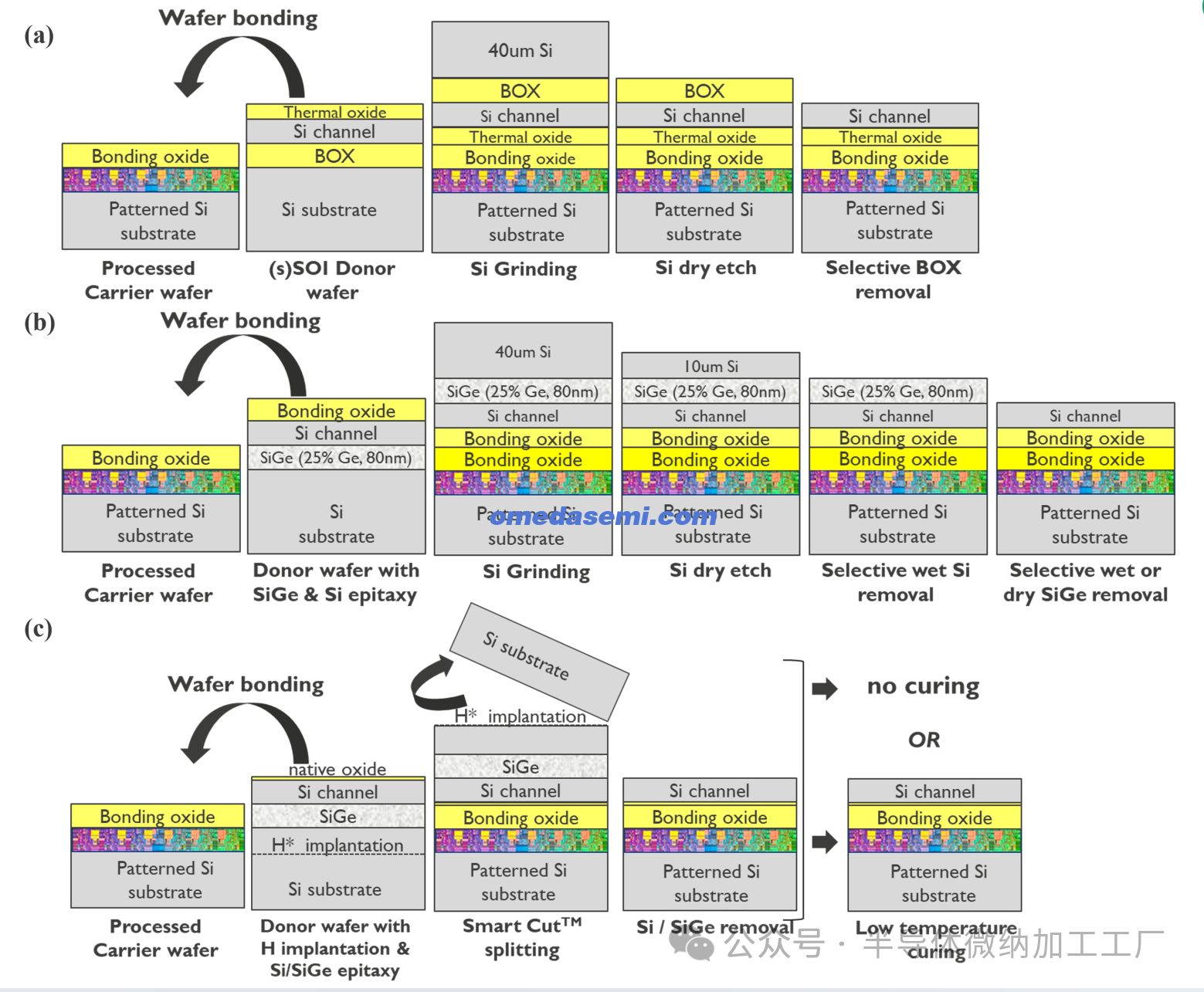

图 3. 层转移流程描述:(a) SOI,(b) SiGe ESL,(c) LT Smart CutTM。SiGe ESL 工艺条件经过优化,外延生长出厚度 80nm 的全应变 Si0.75Ge0.25 层,厚度高于理论临界值,随后生长出厚度约 20nm 的高平滑度 Si 外延层 [4]。SiGe 选择性蚀刻采用干法或湿法化学方法。LT Smart CutTM 流程采用低温固化或无需固化。

层转移工艺对顶层器件的影响:研究了三种基于粘接的层转移技术(图3):(1)使用(s)SOI供体晶圆的(s)SOI流程,和(2)使用Si0.25Ge0.75刻蚀停用层的SiGe刻蚀停用层(SiGe ESL)流程,都是通过研磨和Si刻蚀去除衬底,而(3)SOITEC低温(LT)Smart CutTM流程使用工程化的大块供体晶圆进行薄层分割。从成本角度来看,LT Smart CutTM工艺由于可以重复使用供体晶圆,是最有效的解决方案。根据我们的内部成本模型,SiGe ESL流程的成本比SOI流程低约50%,而LT Smart CutTM流程比SiGe ESL流程进一步降低了16%的成本【3】。然而,不同转移流程对转移硅层的材料和电气特性的影响,对于保持顶层器件的良好性能至关重要。

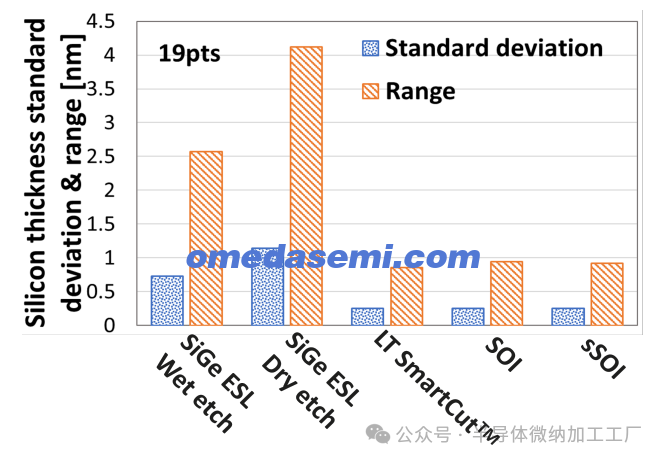

图4. 层转移后Si厚度均匀性比较。

经层转移后的硅层厚度均匀性(范围<1nm)在(s)SOI和LT Smart CutTM流程中得到了非常好的控制,而SiGe ESL流程由于Si研磨后的硅厚度不均匀性和Si与SiGe刻蚀化学选择性的差异,表现出显著的退化【5】(图4)。

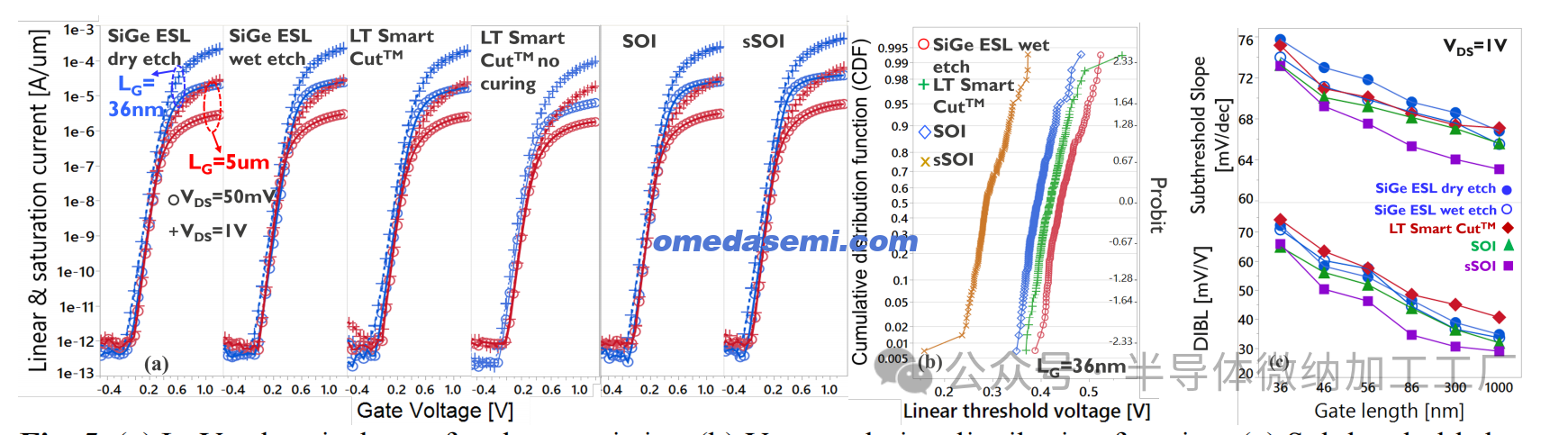

图5. (a) ID-VG电气传输特性, (b) VT累积分布函数, (c) 亚阈值斜率和DIBL,比较不同的层转移流程。

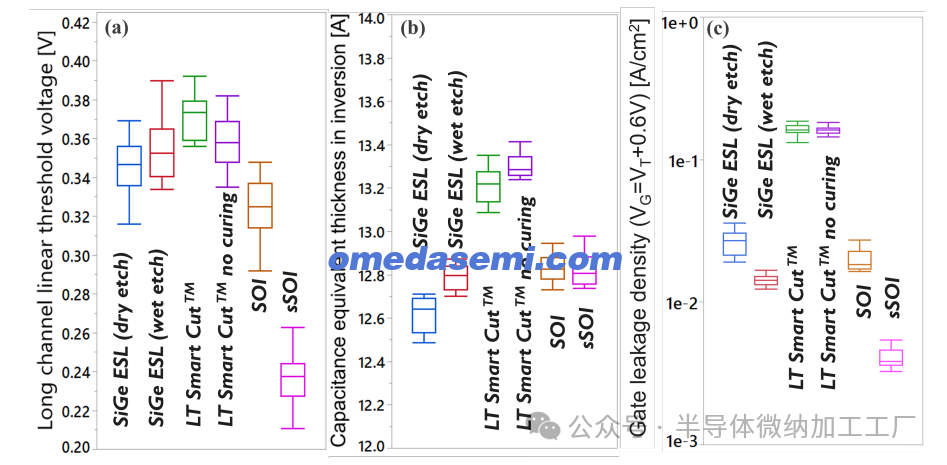

图 6. (a) 阈值电压,(b) 反转电容等效厚度,(c) 不同层转移的栅极漏电密度。

使用不同流程转移的未拉伸硅上的顶层nMOS器件的电气特性(图5和6)总体表现相似,除了LT Smart CutTM流程下VT、CET和JG略有升高。SOI和SiGe ESL流程的电子迁移率(图7d,e)几乎相同,而LT Smart CutTM流程则表现出较低的迁移率。尽管缺乏固化导致更大的迁移率退化,但该工艺具有较低的成本和热预算,可能适用于特定应用,如BEOL晶体管。拉伸硅转移(sSOI)导致电子迁移率的大幅提升,与理论一致,确认拉伸在转移和顶层器件加工后得以保持。由于拉伸相关的子带能级变化和重新填充,VT和栅漏电流(图6a,c)也显著降低。

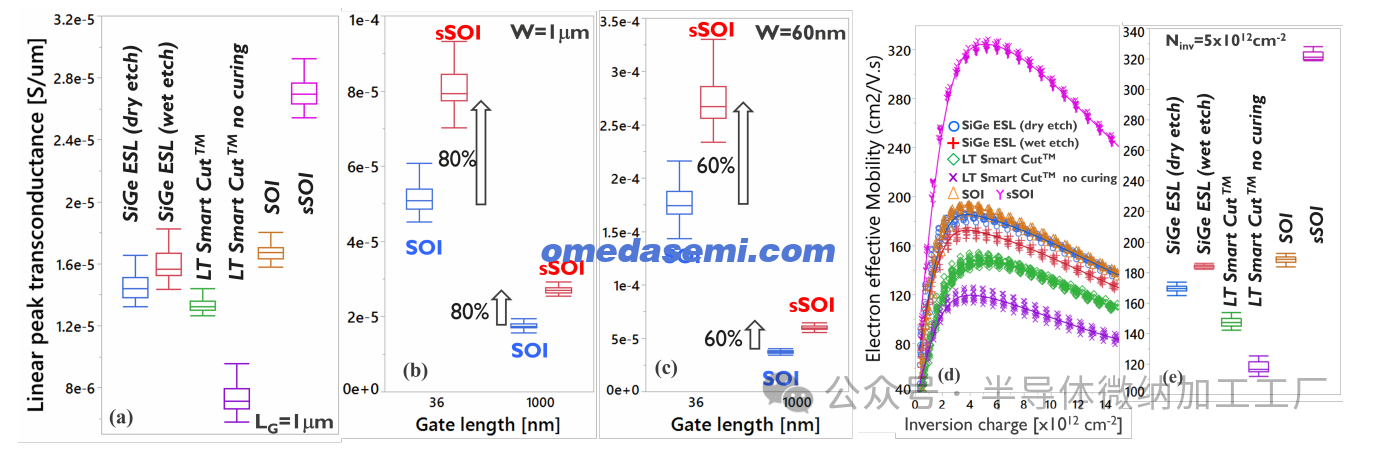

图 7. 线性峰值跨导:(a) 长沟道器件;(b) 宽沟道器件;(c) 窄沟道器件;

无应变和应变器件,LG=36nm &1mm;(d) 电子有效迁移率(分离 CV 方法);(e) 反转电荷为 5x1012cm-2 时提取的电子有效迁移率。

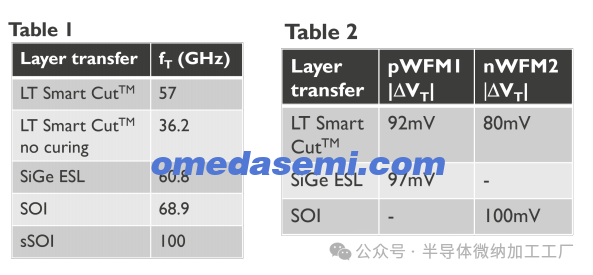

器件的线性跨导峰值(图7a)以及射频转换频率(fT)(表1)与载流子迁移率趋势直接相关。拉伸硅的跨导增益在宽器件中约为80%,在窄器件中降至60%(图7b,c)。

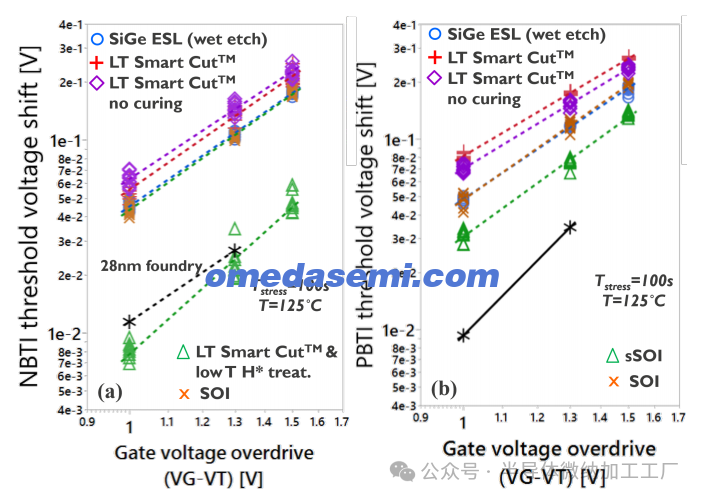

图 8. 顶层器件(a)NBTI 和(b)PBTI 阈值电压漂移。

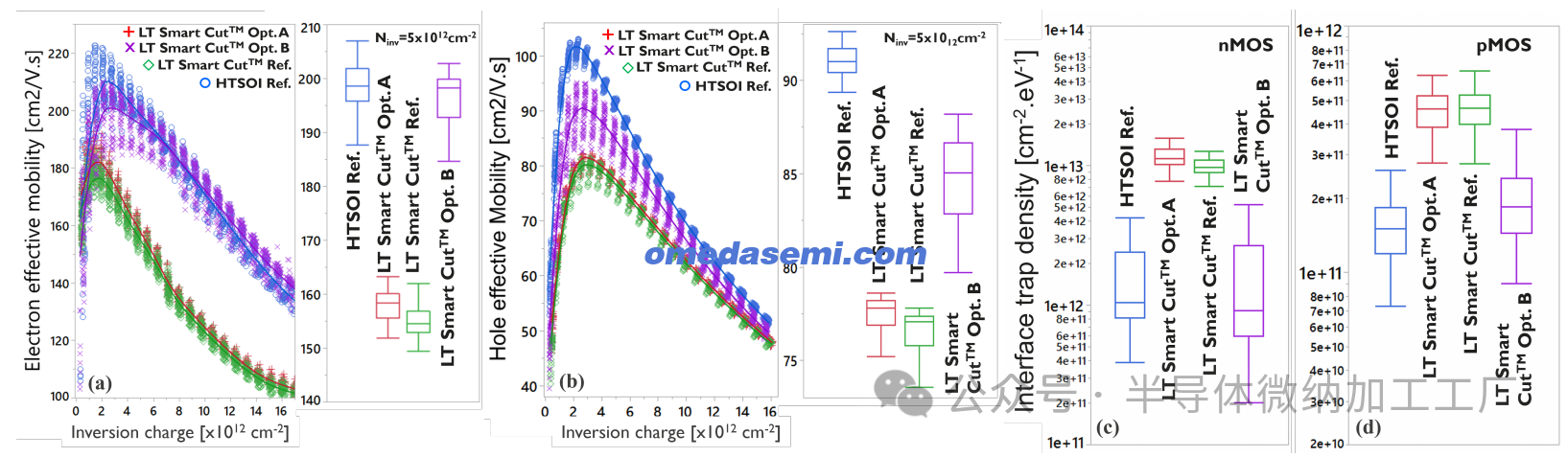

BTI测量(图8)表明,由于低温顶层处理过程中缺乏可靠性退火,VT发生了较大偏移。SOI和SiGe ESL器件表现相似,而Smart CutTM器件则略微退化。对于nMOS,sSOI通过应变相关的Ec降低和能带偏移改善了BTI性能【6】。通过在Si界面使用偶极子,还可以进一步改善【7】。对于pMOS,采用低温原子H处理后再进行H2烧结,用于钝化IL SiO2中的氢氧基E'孔陷阱【8】。通过改变分割注入(opt.A)或固化(opt.B)条件优化LT Smart CutTM工艺,成功制造SOI晶圆,随后进行顶层器件加工。Opt.B可以恢复迁移率损失,达到HT Smart CutTM SOI迁移率的电子值。

图9. (a) 电子和(b) 空穴有效场迁移率与反转电荷的关系,在5x10 12cm-2 Ninv处提取,用于SOI LT Smart CutTM层转移,比较优化和参考工艺条件,(c)、(d) Dit分别在f=100kHz时采用峰值电导法(Gp/w)提取,nMOS和pMOS中

载流子迁移率与界面陷阱密度(Dit)(图9)密切相关,直接影响VT和JG。

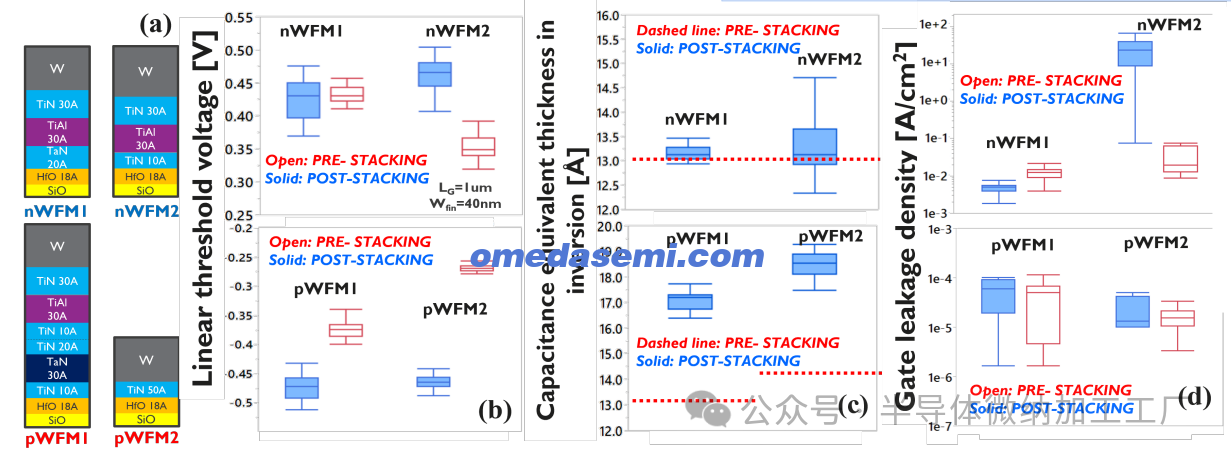

图10. 3D堆叠前后nMOS和pMOS底层长沟道电学参数(a)堆叠描述,(b)VT,(c)CET和(d)JG。

堆叠对底层器件的影响:由于与顶层器件和/或层转移处理相关的额外热预算,3D堆叠对底层器件的长通道VT、CET和JG产生了影响,这一影响在很大程度上取决于底层金属栅堆叠(图10)。对于大多数金属栅堆叠,经过堆叠后,有效功函数(WFM)往往迁移到中间能隙,导致nMOS(pMOS)阈值电压的增加(降低)【9】。在所研究的nWFM下,当使用TiN金属屏障时,堆叠后栅漏电流增加,但当使用TaN金属屏障时,则被抑制,可能是因为TaN更好地阻挡了Al的扩散。使用TaN屏障的nWFM在堆叠后没有VT偏移,而CET对于两种nWFM在3D堆叠后保持稳定。对于pWFM,CET大幅增加,而栅漏电流没有变化。此外,VT的偏移对于不同的层转移流程是相似的(表2),这表明LT Smart CutTM转移流程的热预算不是总的3D堆叠热预算的主导因素。由于顶层热预算,可以在不进行可靠性退火的情况下达到BTI规范。

表 1:不同层转移流程下顶层平面器件 (LG=45nm) 的 RF 参数。

表 2:不同层转移流程下底层 finFET 阈值电压在 3D 堆叠前后的变化。

结论:展示了使用不同层转移流程的全3D器件堆叠。SiGe ESL和SOI流程对器件性能没有影响,但成本较高。通过使用新开发的优化工艺条件,LT Smart CutTM流程以更具成本效益的方式实现了相同的器件性能。

文章名:Demonstration of 3D sequential FD-SOI on CMOS FinFET stacking featuring low temperature Si layer transfer and top tier device fabrication with tier interconnections作者:A. Vandooren, N. Parihar, J. Franco, R. Loo, H. Arimura, R. Rodriguez, F. Sebaai, S. Iacovo, K. Vandersmissen, W. Li, G. Mannaert, D. Radisic, E. Rosseel, A. Hikavyy, A. Jourdain, O. Mourey*, G. Gaudin*, S. Reboh**, L. Le Van-Jodin**, G. Besnard*, C. Roda Neve*, B-Y. Nguyen*, I. Radu*, E. Dentoni Litta and N. Horiguchi. 单位:imec, Kapeldreef 75, 3001 Leuven, Belgium *SOITEC, Parc Technologique des Fontaines, 38190 Bernin, France **CEA, LETI, Université Grenoble Alpes, 38000 Grenoble, France