工艺路线:超薄SOI晶圆(4.5nm-2um-525um)上MBE生长8nmSTO,然后退火把4.5nm的si热氧化为SIO2,然后在sto上mbe分子束外延bto,再pvdbto,这样带有电光系数的 bto薄膜晶圆就得到了,不用做键合,衬底去除等外延层的出去等工艺 本文展示了无需复杂的晶圆键合工艺,即可在厚SiO2上制造外延超薄SrTiO3 (STO)。所得的过渡金属氧化物(TMO)-玻璃层堆栈类似于传统的硅绝缘体(SOI)晶圆,其中SOI的晶体设备硅层已被晶体功能性TMO层替代。制造过程从超薄体SOI开始,在其上通过分子束外延(MBE)生长晶体STO。随后,通过外部高温干燥氧气退火将设备硅层完全氧化,经X射线光电子能谱(XPS)、X射线反射率(XRR)和高分辨率电子显微镜确认这一过程。STO在退火后保持与载体硅基底的外延配对,并未观察到STO晶体质量因TMO-玻璃制造过程而退化的迹象。无需晶圆键合工艺即可轻松制造TMO-玻璃平台,将促进基于TMO的电子和光子器件的快速发展。#0:10mm-10mmsto衬底-bto薄膜(300nm厚度可定制)

#1:sto外延片

2寸 外延 sto 2-20nm(可定制)- 2um Sio2(可定制) -Si(可定制)

#2:a向 bto外延片

2寸 外延 a-向 bto(300nm或者500nm,或者定制)-sto 8nm(可定制)- 2um Sio2(可定制) -Si(可定制)

#3:C向 bto外延片

2寸 外延 c-向 bto(150nm或者300nm,或者定制)-sto 8nm(可定制)- 2um Sio2(可定制) -Si(可定制)

#离子注入铒代工

#6寸DUV步进式光刻代工,最小线宽180nm,超高性价比,可以只曝光

#快速氮化硅硅光铌酸锂流片 #高性价比 #低成本

#提供8寸 8umSiO2热氧片,6寸15um热氧片 10um热氧片 8寸10um热氧片

室温低损伤@GCIB抛光代工@束斑小(4-5mm)更均匀

#降低硬质材料化合物晶圆等绝大多数材料的表面粗糙度,比如金刚石 ,磷化铟,砷化镓,碳化硅

#提高复合衬底和镀膜膜层的器件层膜厚均匀性,

比如SOI LNOI LTOI SICOI 等 SMARTCUT得到的薄膜

或者镀膜所得到的膜层 ,比如镀了一层氮化硅,但是由于是cvd镀膜所得到的,表面的膜厚精度很差,粗糙度很差,可以通过粗糙度初步降低粗糙度,然后通过GCIB团簇离子束抛光来修整整面的膜厚均匀性 到0.5%以下举例:

未经过Trimming 工艺的 6寸LN/LTOI晶圆 数据:

Range:100-200A

经过Trimming 工艺的 6寸LN/LTOI晶圆 数据:

Range:60A以内

SOI晶圆:--220nm薄膜/ 3um厚膜-3umSIO2-675umALOOI晶圆;--氧化铝薄膜晶圆,键合工艺和镀膜工艺

TAOOI晶圆--氧化钽薄膜晶圆,镀膜工艺

SINOI晶圆--超低损耗氮化硅薄膜晶圆,210nm-300nm-400nm-800nm

SICOI晶圆;新型量子光学平台500nm-700nm-1um

6寸LTOI晶圆批量供应;铌酸锂的有力的竞争对手,薄膜钽酸锂晶300600

8寸LNOI晶圆;8寸LNOI助力更大规模薄膜铌酸锂产品量产

LN/LT-SOI/Si/SIN W2W&D2W异质集成

流片: 6寸 氮化硅 铌酸锂 硅光 超高性价比流片, 1个BLOCK的价格买一整片晶圆

划重点--全国产-超高性价比-6 寸硅光-氮化硅-铌酸锂流片白皮书

我们为客户提供晶圆(硅晶圆,玻璃晶圆,SOI晶圆,GaAs,蓝宝石,碳化硅(导电,非绝缘),Ga2O3,金刚石,GaN(外延片/衬底)),镀膜(PVD,cvd,Ald,PLD)和材料(Au Cu Ag Pt Al Cr Ti Ni Sio2 Tio2 Ti3O5,Ta2O5,ZrO2,TiN,ALN,ZnO,HfO2。。更多材料),键合(石英石英键合,蓝宝石蓝宝石键合)光刻,高精度掩模版,外延,掺杂,电子束光刻等产品及加工服务(请找小编领取我们晶圆标品库存列表,为您的科学实验加速。

请联系小编免费获取原文

文章名:Epitaxial Oxides on Glass: A Platform for Integrated Oxide Devices作者:J. Elliott Ortmann,† Martha R. McCartney,‡ AghaPosadas,† David J. Smith,‡and Alexander A. Demkov*,†1Department of Physics, The University of Texas, Austin, Texas 78712, United States2Department of Physics, Arizona State University, Tempe, Arizona 85287, United States

引言

允许在硅上外延沉积过渡金属氧化物(TMO)薄膜的工艺发展是集成器件领域的一个重大成就【1-8】。通过将晶体TMO薄膜与硅结合,TMO薄膜及其薄膜异质结构所展示的众多新兴现象【9-13】突然成为一种技术相关的平台。此后,许多研究已考察了在硅上外延生长TMO薄膜的异质结构,用于器件制造【14】,包括平面电子器件【15-17】,微电机械系统【18,19】和光子集成电路【20-23】。

尽管TMO薄膜的硅兼容性对制造实用器件至关重要,但许多TMO-硅器件通过将其集成到高绝缘性的SiO2上,往往能获得更大的好处,因为与半导体硅相比,SiO2具有更优越的电气和光学隔离性。实际上,当前最先进的基于TMO的光子器件已经在SiO2上而非直接在硅上制造【24-28】。然而,SiO2的非晶性质使得在SiO2上直接外延沉积晶体TMO薄膜变得不可能,因此必须开发替代的制造方法,如液态金属反应【29,30】或复杂的晶圆键合工艺【26】,以实现所需的层堆栈。这些晶圆键合工艺比直接外延沉积要复杂得多,并且在许多实验室中无法实施,限制了能够访问这种异质结构的研究小组数量。开发一种可靠、简单的制造途径对于推动基于TMO-玻璃平台的创新技术具有重要意义。

在这项工作中,我们开发并展示了一种通过直接沉积在SiO2上制造外延晶体TMO薄膜的工艺。通过X射线光谱和衍射测量以及电子显微镜表征,我们成功地展示了在厚SiO2上制造超薄外延SrTiO3(STO)。因为许多有前景的TMO基器件的制造,如使用BaTiO3【22,23,26,31,32】、EuO【33,34】和STO/LaAlO3超晶格【35-38】的器件,依赖于超薄STO缓冲层与硅的集成,所以这项工作中的结果将促进在STO缓冲SiO2平台上创建广泛的创新集成器件。没有发现因TMO-玻璃制造工艺而导致的STO降解。值得注意的是,完成此工艺所需的工具在大多数实验室和洁净室中都可以获得,这使得更多的研究人员可以使用已在实际集成技术中找到应用的最先进的TMO-玻璃层堆栈。

硅的热氧化是一个众所周知的工艺,最早由Deal和Grove在1960年代描述【39】,至今仍广泛应用于现代微电子工业。最近,Guo等人将Deal和Grove的模型扩展到硅下埋藏一层外延STO的热氧化过程,主要受到STO缓冲硅在集成TMO器件研究中的普遍性的推动【40】。他们的结果建议了一种制造STO缓冲SiO2的工艺:首先在薄硅层上外延沉积超薄STO,然后完全氧化下方的硅。虽然类似的硅氧化过程已经通过在高温下退火较长时间在厚TMO薄膜下进行过【41】,但由于STO/硅界面在高温下可能发生破坏性反应,尚不确定超薄外延STO是否能承受这样的过程。然而,在此,成功实现了这种工艺并进行了展示。

实验部分

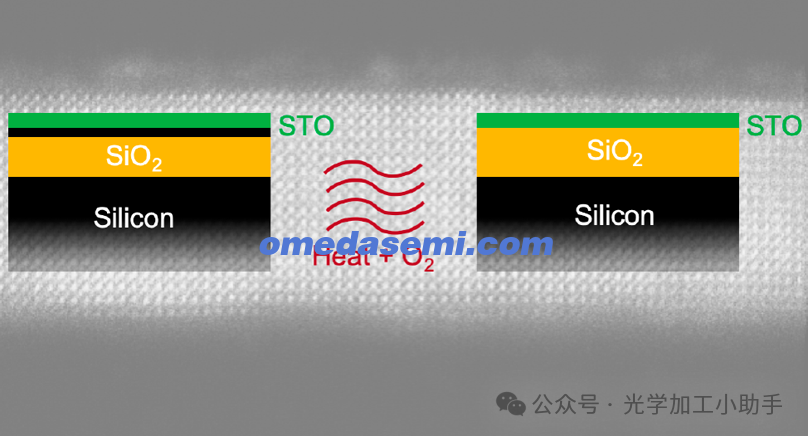

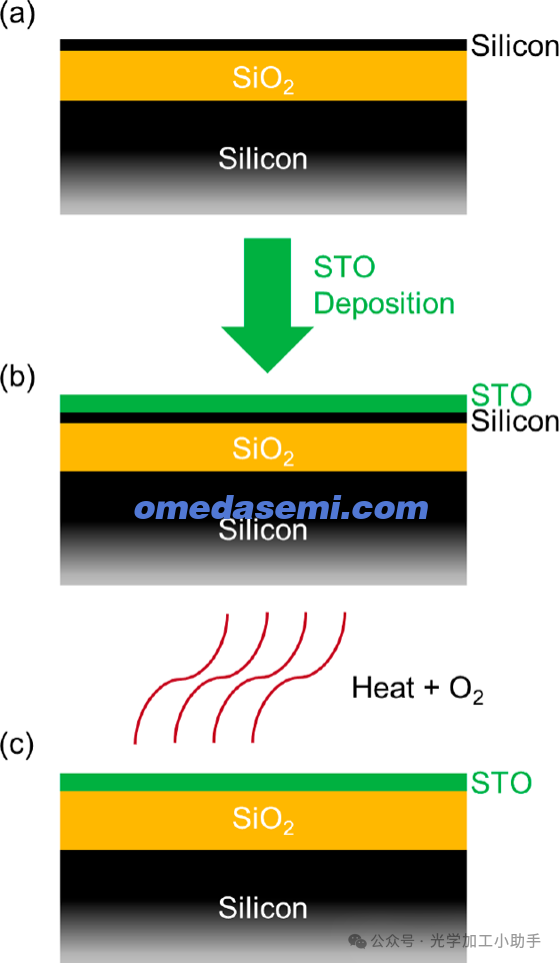

图1. 用于制造外延TMO薄膜在SiO2上的工艺示意图

该工艺从超薄体SOI晶圆开始(a)。接着,通过MBE在超薄体SOI上外延沉积STO(b)。然后,将样品从真空中取出并在O2气氛中退火,导致器件硅层的后沉积氧化。结果,形成的层叠结构(c)具有外延的晶体STO,并且位于厚SiO2上,能够实现功能性TMO层与硅基底之间的优异电气和光学隔离。

薄膜生长: 样品的制造从超薄体SOI晶圆开始(图1a)。超薄体SOI可以通过多种工艺制造【42】,包括纳米分离【43】和Soitech的Smart-Cut技术【44,45】,并且已经在多种器件中得到了应用,包括完全耗尽场效应晶体管【46】和光子传感器【47】。本工作中使用的超薄体SOI晶圆由Soitech提供,具有45 Å厚的器件硅层和650 Å厚的埋氧化物(BOX)SiO2层。从理论上讲,BOX层的厚度可以调整以满足预期器件结构的规格。

在沉积之前,每个20 × 20 mm²的超薄体SOI基片首先在丙酮、异丙醇和去离子水中超声清洗,每种溶液清洗10分钟。去油后,基片被浸入20:1的缓冲氧化物蚀刻液中30秒,以去除本征氧化层。清洗并蚀刻后的基片在去除本征氧化层后的3分钟内转移到真空环境中,然后引入生长室,使用一个定制的DCA 600分子束外延(MBE)系统,基压为5 × 10−10 Torr。

当基片装入生长室后,基片在超高真空(UHV)条件下(室内压力约5 × 10−9 Torr)被缓慢加热到600°C,以去除氢终端层。为了确保超薄器件硅层不会因热应力而损坏,采用了相对较慢的加热和冷却速率(10°C/min)。当基片温度稳定在600°C时,使用热电偶进行测量,向表面沉积1/2单层(ML)的锶,以形成Zintl层,供后续的氧化物沉积【1,2,48】。Zintl层的形成通过反射高能电子衍射(RHEED)现场观察到的2 × 1表面重构确认。形成Zintl层后,将基片温度降低至200°C,以准备STO沉积。

当基片温度稳定在200°C时,慢慢打开氧气阀,让分子氧流入MBE系统,室内压力升高至大约7 × 10−8 Torr。压力稳定后,锶和钛在基片上以大约1 ML/min的速度共同沉积,沉积速度通过石英晶体监测器(QCM)进行测量。金属沉积是通过从蒸发源中蒸发进行的。大约沉积2分钟后,氧气压力稳步增加,持续3分钟,最终压力达到5 × 10−7 Torr。沉积5分钟后,关闭氧气阀,停止沉积,得到五个单位晶格(u.c.)的STO沉积在硅上。当在如此低温下沉积时,STO是无定形的。随后将样品加热至550°C,在UHV中退火,使STO薄膜晶化,晶化过程通过RHEED确认。晶化后,每个样品在UHV中以550°C退火10分钟,然后冷却至200°C。随后使用相同的重晶化过程再沉积10个单位晶格(u.c.)的STO,最终得到15个单位晶格(u.c.)的外延STO(图1b)。

器件硅氧化: 完成STO沉积后,样品被从UHV中取出,并在管式炉中以800°C的温度、流动的干氧气中退火2小时。Guo等人发现这些条件可以完全氧化亚表面的器件硅层,而不会降解顶部STO层的质量【40】。最终得到的样品具有15个单位晶格的外延晶体STO,覆盖在约750 Å的无定形SiO2层上(图1c)。

样品表征: 使用VG Scienta工具进行原位X射线光电子能谱(XPS)测量,使用铝KαX射线源,基压约为5 × 10−10 Torr。X射线衍射(XRD)和反射率(XRR)测量使用Rigaku Ultima IV衍射仪,采用铜Kα辐射。透射电子显微镜(TEM)样品通过使用FEI Nova 200聚焦离子束(FIB)铣削制备。高分辨率TEM图像使用带有图像校正的FEI Titan 80-300机型,在300 keV下操作拍摄,而畸变校正的环形暗场扫描透射电子显微镜(STEM)图像则使用JEOL ARM-200F机型,在200 kV下操作拍摄。束流聚焦角度设为20 mrad,采集角度设为90-150 mrad。

结果与讨论

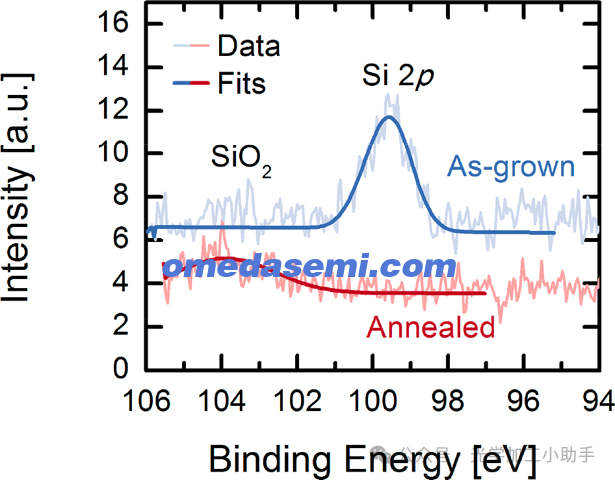

图2. 在Si 2p核心能级附近的生长后(浅蓝色)和退火后(浅红色)STO-on-SOI样品的XPS光谱。元素硅2p峰在退火后消失,这是由于器件硅层的氧化,且可以在稍高的结合能处观察到对应于非晶氧化硅的宽Si 2p峰。数据拟合分别用深蓝色(生长后)和深红色(退火后)表示。

器件硅层的氧化通过比较退火前后硅2p核心能级的XPS光谱得到了确认(图2)。XPS光谱清晰地显示出在氧化样品中元素硅2p峰的消失。在退火后的样品光谱中,可以看到一个宽的低强度峰,位于比元素硅2p峰更高的结合能位置,这个峰来自STO薄膜下的非晶氧化硅(图2)。非晶材料的XPS核心能级通常比晶体的更宽。需要注意的是,图2中的光谱是从同一样品中获得的,分别是在O2退火前后获得的。硅核心能级的相对较弱信号是由于光电子从埋在STO下方的硅层中逸出的深度有限【49,50】。

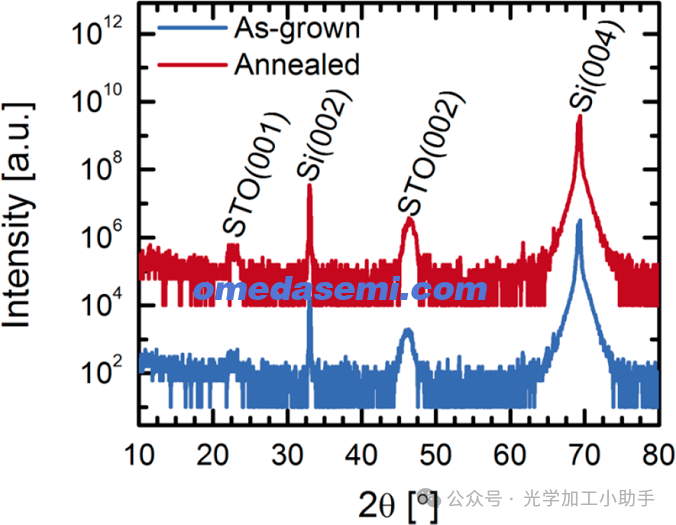

图3. 生长后(蓝色)和退火后(红色)样品的面外θ/2θ XRD测量。为了清晰展示,光谱进行了偏移。仅观察到STO薄膜的一个晶格面,表明在器件硅层氧化前后,STO薄膜与底层硅基板之间存在外延关系。

虽然O2退火预计会氧化器件硅层,但由于STO/硅界面可能发生破坏性反应,超薄晶体STO层的存活并非理所当然。因此,进行XRD和XRR测量以确认STO晶体结构在整个制造过程中的持续性。出射平面θ/2θ XRD测量(图3)确认了STO薄膜与下层硅之间的外延关系,既在生长后的样品中,也在退火后的样品中。两种光谱中仅观察到STO薄膜的(00l)峰,其中l是整数米勒指数。STO的外平面晶格常数在生长后的样品中测量为约3.94 Å,在退火后的样品中测量为3.92 Å,表明STO晶格常数在后沉积退火过程中部分放松,趋向于其体积值。

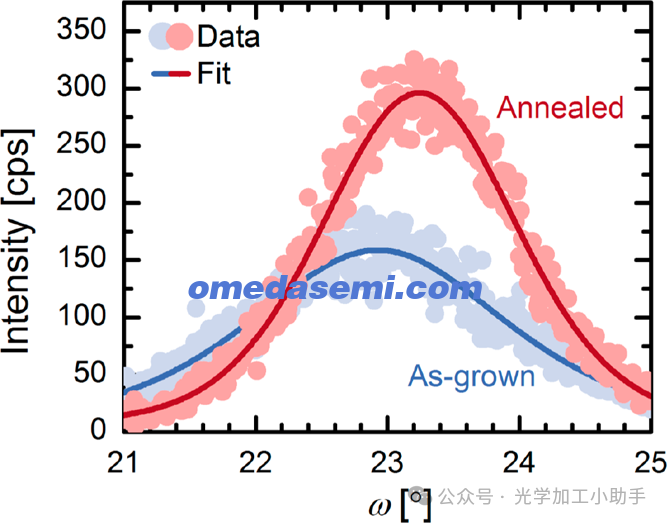

图4. 生长后(蓝色)和退火后(红色)样品的STO(002)晶格峰值的摇摆曲线。实心圆点表示数据,实线为对数据的拟合。

通过收集生长后和退火后样品的STO(002)峰值的X射线摇摆曲线(图4),表明退火后STO的晶体质量得到了改善。退火样品的摇摆曲线半高宽(FWHM)相较于生长后样品减少了大约25%,这一结果是通过用Pearson VII函数(实线,图4)拟合摇摆曲线得出的。由于STO必须在高度还原的条件下沉积在硅上,以确保晶体硅表面的完整性适合外延生长,因此STO晶体质量的改善很可能主要是由于STO内部氧空位的修复以及相关晶体缺陷的减少。此外,由于STO与硅的热膨胀系数不匹配所产生的热应变可能在硅层氧化后得到了缓解【51】。

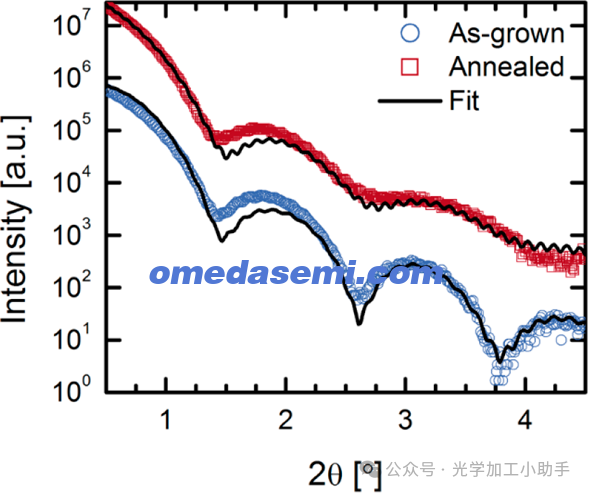

图 5. 生长后样品(蓝色圆圈)和退火后样品(红色方块)的 XRR 测量。为了清晰起见,谱图已偏移。数据以离散的数据标记显示,拟合曲线以实线表示。短周期的振荡是由 BOX 层的厚度引起的。

XRR 测量(图 5)也在设备硅层氧化前后进行了收集。使用 GenX 软件对谱图进行拟合,并提取了材料参数进行比较。STO 的厚度在样品之间是一致的,约为 69 Å,符合拟合误差范围。所测得的厚度略大于名义厚度约 59 Å,这可能是由于 QCM 校准中沉积速率的高估。35 此外,生长后样品的表面粗糙度约为 4.2 Å,而退火后样品的表面粗糙度约为 3.4 Å。两者表面粗糙度之间的小差异表明,设备硅层的氧化对 STO 表面粗糙度没有显著影响。

XRR 谱图之间的主要区别在于,退火样品的振荡幅度相比生长后样品有所减小。振荡幅度的减小是由于 STO 和 SiO2 之间的密度对比小于 STO 和硅之间的密度对比。53 因此,XRR 谱图证实了在 O2 退火后设备硅层的氧化,这与 XPS 结果(图 2)一致。

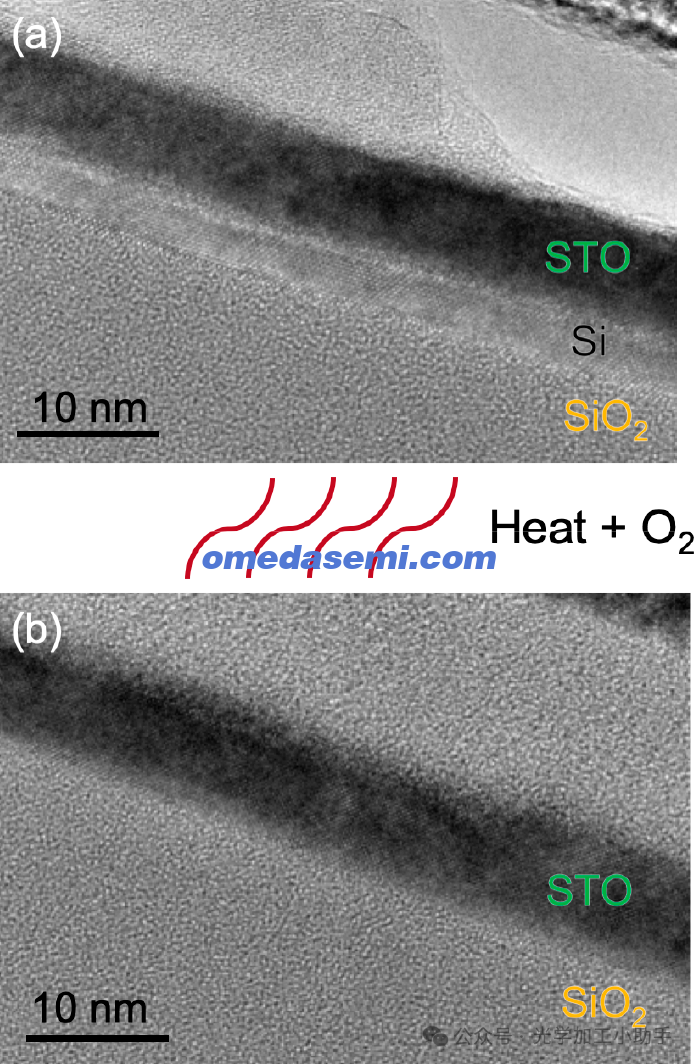

图6. 横截面HREM图像:(a) 生长后的样品和(b) O2退火后的样品。HREM图像确认了O2退火后设备硅层的完全氧化。

通过横截面高分辨率电子显微镜(HREM)可以直接观察退火前后样品的局部微观结构。对于生长后的样品,HREM 图像确认了薄的晶体设备硅层上生长了 STO 薄膜(图 6a)。在 STO 和设备硅之间还可见到一层薄的无定形中间层,这在 STO 生长在硅上的情况下是常见的【20,21,26,37,51】。在退火样品的 HREM 图像中(图 6b),设备硅层已经不存在,这与 XPS 和 XRR 结果一致(分别见图 2 和图 5)。因此,HREM 测量确认了通过 O2 退火成功氧化了整个设备硅层。此外,从 HREM 图像中测得的 STO 厚度约为 70 Å,与 XRR 拟合结果一致(图 5)。

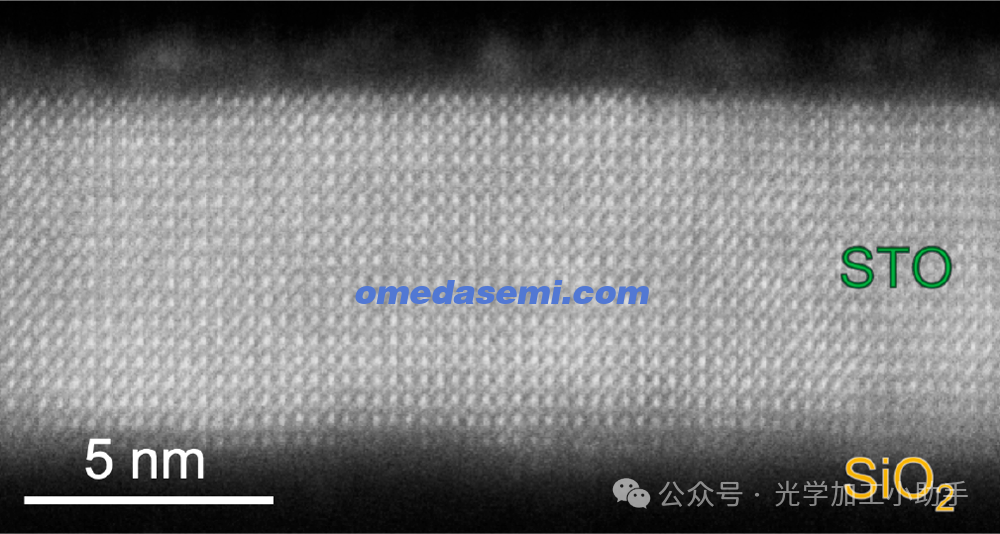

图7. 在环形暗场模式下捕获的TMO-on-glass层叠结构的原子分辨率AC-STEM图像,展示了外延超薄STO薄膜的优异晶体质量,以及设备硅层的缺失。该图像是沿STO [100]区轴拍摄的。

高温O2退火后STO晶体质量的保持已经通过像差修正扫描透射电子显微镜(AC-STEM)进一步确认(图7)。从AC-STEM图像中没有观察到STO晶体晶格的退化,且在成像视场中几乎没有明显的缺陷。此外,STO薄膜与SiO2层之间的界面并未显示出在高温退火过程中STO薄膜与设备硅层之间发生化学反应的迹象。相反,整个薄膜在TMO-on-glass制造过程中得以保留,提供了一个平滑、高度晶化的模板,适合进一步的薄膜沉积和设备图案化。

结论

总之,我们展示了通过直接沉积成功制造TMO-on-glass层叠结构。所得样品具有外延超薄STO层,且位于厚SiO2层之上,形成了STO缓冲的SiO2伪衬底。这里展示的STO缓冲SiO2伪衬底具有广泛的潜在应用,主要得益于其制造过程的简便性。STO缓冲SiO2与多种功能性TMO材料的外延兼容性将促进在电气和光学隔离平台上制造新型TMO器件。例如,使用TMO-on-glass平台构建平面TMO基电子器件将确保去耦埋层半导体硅基底的面内电子响应,使得任何测量响应都能明确归因于TMO薄膜和界面本身。此外,还可以基于TMO-on-glass平台开发TMO基光子器件,防止受限的光模式泄漏到硅基底中。这里描述的TMO-on-glass平台应为许多新型TMO器件的制造和研究打开大门,通过提供更大的层叠结构的可接入性,并促进对功能氧化物本身的研究,从而使其与生长衬底解耦。