摘要:声光集成技术拥有众多应用,包括低损耗微波信号处理、非互易光传播、频率梳生成以及宽带声光调制。目前最先进的声光系统主要采用内部制造工艺实现,尽管性能优异,但通常成品率较低,且不兼容代工工艺的量产。本文,我们展示了基于硅光子代工工艺集成的各种基于AlScN的声光调制器 (AOM),从而能够在同一基板上高成品率、低成本地批量生产AOM以及其他光子和电子器件。采用不同孔径长度和指状对数量实现的表面声波换能器表现出高效的宽带调制性能,并探讨了不同设计参数对AOM效率的影响。在94 MHz带宽上实现了-14.6 dB的调制效率,据我们所知,这是目前已报道的硅基声光调制器中效率和带宽组合最高的,与最先进的CMOS兼容声光调制器相比,其品质因数提高了约一个数量级BW(VπL)-1。本研究开发的单片集成声光平台将为低成本、微型微波滤波器、真时间延迟器、频率梳以及其他具有代工厂集成光子电路先进功能的信号处理器奠定基础。

关键词:声光调制、氮化铝钪、光弹性、硅光子学、表面声波

#6寸DUVKRF流片--SIN/铌酸锂晶圆级流片

#利用现有掩膜版提供流片好的SIN晶圆做键合工艺调试

*近化学计量比 Z切 X切 Stoichiometric_LNOI/LTOI 薄膜铌酸锂 和钽酸锂晶圆 -----量子应用#高电光系数和非线性光学系数 #更少的短波吸收 #更小的矫顽场SLT和SLN与其对应的同成分相比电光系数和非线性系数都有比较大的提高,有利于电光器件的制作。对于制作周期极化结构,其畴结构的变化和矫顽场的降低,制作的周期结构更加容易和质量更好。由于SLT折射率差值变得更小,Ppslt更容易在量子光学上得到应用。SOI晶圆--220nm薄膜/3um厚膜,顶层器件层为高阻硅,具有更好的光学效果ALOOI晶圆;--氧化铝薄膜晶圆,键合工艺和镀膜工艺

SINOI晶圆;--超低损耗氮化硅薄膜晶圆,

SICOI晶圆;新型量子光学平台

6寸LTOI晶圆批量供应;铌酸锂的有力的竞争对手,薄膜钽酸锂晶圆

8寸LNOI晶圆;8寸LNOI助力更大规模薄膜铌酸锂产品量产

LN/LT-SOI/Si/SIN W2W&D2W异质集成

流片: 6寸 氮化硅 铌酸锂 硅光 超高性价比流片, 1个BLOCK的价格买一整片晶圆

划重点--全国产-超高性价比-6 寸硅光-氮化硅-铌酸锂流片白皮书

引言

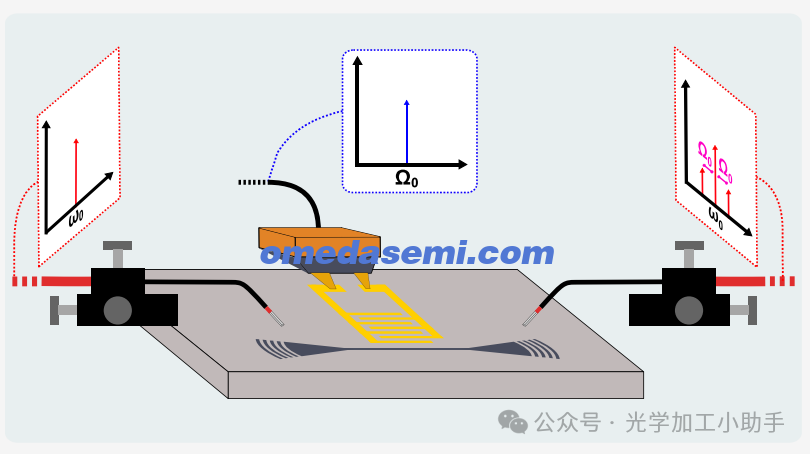

利用声子-光子相互作用的声光系统在微波光子学、光频移、非互易光子学、传感、光谱学和量子信息控制等许多应用领域取得了显著进展。1-4 将机械波技术与集成光子系统相结合,可以实现用于射频 (RF) 和光信号处理的先进设备。3,5,6 一个重要的例子是声光调制器 (AOM),它是声学和光域之间信息转换的关键组件。传统上,声光调制器使用体晶体材料实现,尽管性能优异,但通常体积大、价格昂贵,并且由于声波限制较弱而不适用于大规模集成应用。2,6,7 基于表面声波 (SAW) 的调制器在结构表面提供高度的声波限制,并且可以与同一表面上的光子器件共集成平台。5,7-9 SAW调制器的工作原理依赖于光弹效应,10其中使用压电层实现的叉指换能器(IDT)发射的机械波与光波导相互作用并调制波导介质的折射率由于施加的应变。11由于高度的限制和声场与光场之间的较大重叠,可以在小尺寸内实现高效的基于SAW的AOM。7,8,12,13此类调制器已经通过使用不同的材料系统来实现。铌酸锂平台具有强大的压电和电光特性,已用于实现基于 SAW 的 AOM。6、8、9、14-17 尽管效率出色,但铌酸锂与硅之间的晶格不匹配使得此类设备与硅光子学和互补金属氧化物半导体 (CMOS) 电子器件的大规模集成具有挑战性。12 同样,基于 PZT 的 AOM 提供了很高的声光调制效率11,但与 CMOS 平台不兼容。氮化铝 (AlN) 是另一种压电材料,已用于在硅光子芯片上集成 SAW 换能器,7、13、18-20 尽管与 CMOS 工艺兼容,但 AlN 相对较弱的压电响应限制了基于 AlN 的 AOM 的效率。通过合金化(生成AlScN)可以改善AlN的压电响应,同时保持其与CMOS和硅光子集成的兼容性。12,21-25迄今为止,与光子系统集成的基于AlScN的SAW换能器完全基于内部光子制造工艺,尽管这些工艺方法创新,但仍存在产量有限、成本高昂以及无法大规模生产等问题。本文,我们展示了几种基于AlScN的声学换能器,它们基于商用工艺制造的SOI芯片。已实现的器件用于研究指状对数量(N)和孔径长度(L)对调制器响应的影响,探索高效宽带调制器的设计空间。据我们所知,与其他已报道的CMOS兼容硅基声光调制器相比,本研究实现了最高的测量声光调制效率,并且工作带宽提高了两倍多。 AOM 器件是通过在使用先进微铸造厂 (AMF) 绝缘体上硅 (SOI) 光子多项目晶圆 (MPW) 工艺制造的光子结构上进行后处理来实现的。在实现的调制器中,在具有 20 个指对的 190 μm 长的器件上,在 3 dB 带宽 94 MHz(约 5.6 GHz)上实现了 0.93 Vcm 的最小 VπL。相应的效率-带宽组合导致 BW(VπL)−1 品质因数比目前最先进的硅基 CMOS 兼容 AOM 高出约一个数量级的改进。在 CMOS 兼容的商用光子工艺上集成高效宽带声学器件,可以在同一芯片上大规模生产高产量、低成本的声学、光子和 CMOS 器件,从而实现复杂的电-声-光子系统和计算。此外,我们器件提供的宽带操作除了信息处理和微波-光转换之外,还可能为通信应用打开大门。

■ 结果

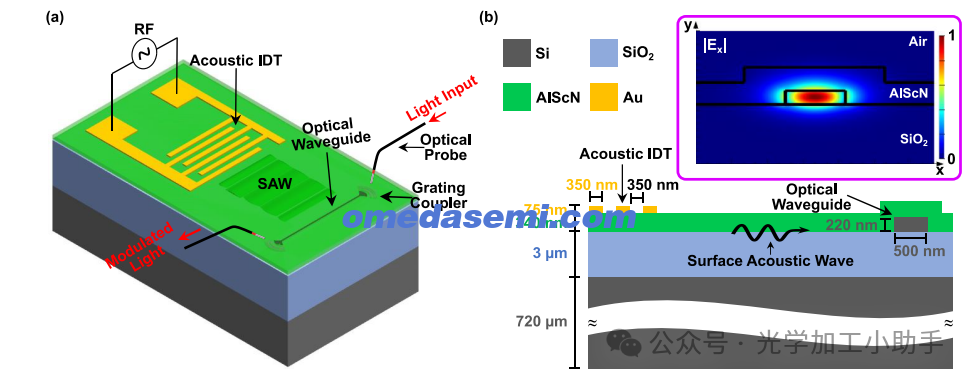

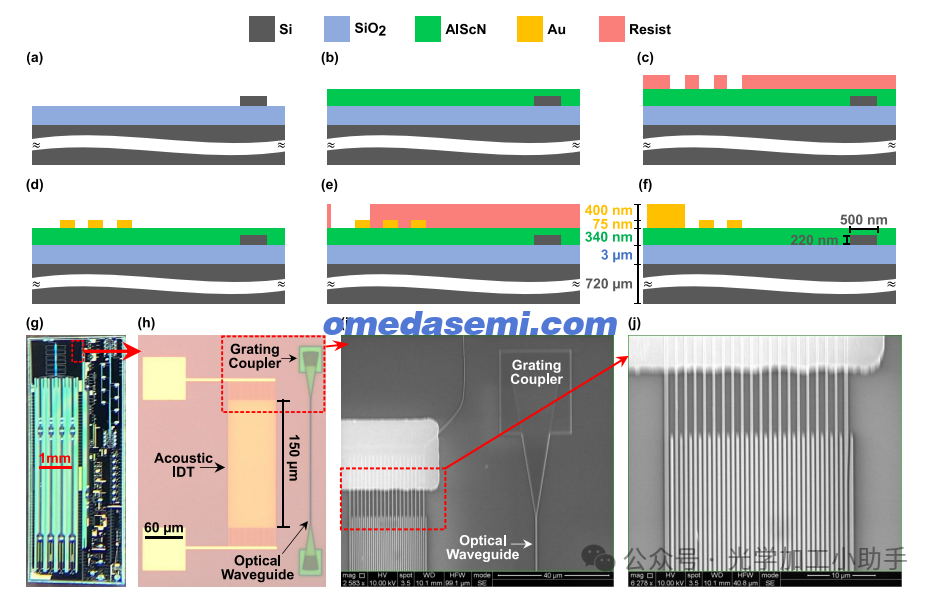

图1. 已实现的声光调制器的(a)结构和(b)横截面图。由声学叉指换能器发射的表面声波(SAW)在入射到光波导时传播并产生应变。应变引起的折射率变化导致光波的相位调制。IDT:叉指换能器。插图:由顶部沉积有AlScN的Si波导支撑的基模模式分布。

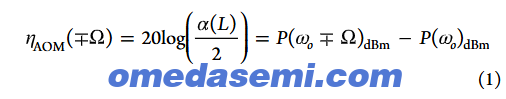

所实现的声光调制器的示意图和横截面分别如图 1a 和 1b 所示。AOM 结构由采用 AMF SOI 工艺制造的单模光波导和使用与 CMOS 兼容的内部后处理步骤在光波导旁边制造的声换能器组成。声换能器的实现方式是,首先在 SOI 的埋氧层 (BOX) 上沉积一层 AlScN 压电薄膜芯片,然后在AlScN层上制作Au交错指状电极。尽管由于AlScN的折射率大于SiO2,AlScN的沉积会使光学模式略微向上移动,但该模式仍然很好地限制在Si芯中,如图1b插图所示。当将射频信号施加到声换能器时,会发射SAW,该SAW在BOX表面传播并与光波导相互作用。结果,光波导发生应变,导致波导的折射率发生与声波强度成比例的变化。这种声学引起的折射率变化调制了在波导内传播的光波的相位。因此,在光载波周围出现了声光相位调制边带。第一个上边带或下边带的功率与载波功率的比率定义为声光调制效率(ηAOM),写为

其中,ωo、Ω = 2πf、f、α(L) = −2πΔneffLλ0⁻¹、λ0、L 和 Δneff 分别表示光波的角频率、射频信号的角频率、射频信号的频率、由声光调制引起的光相位位移量、光波的波长、相互作用长度以及声致有效折射率变化。

此处的声光调制本质上是一个模态内散射过程,其中弹性波与光波之间的相互作用将部分光能转移到由同一波导模式引导的斯托克斯和反斯托克斯带中。动量守恒使得声光散射过程中的相位匹配成为必要,这需要:

其中 β 和 q 分别对应于光波和声波的波矢。利用公式 2,声波波矢可以近似为

其中,vg是光模在ω0附近的群速度。在声波垂直于光传播方向的配置中,轴向声波矢量为零,这意味着相位匹配条件并未完全满足。然而,只要ΔqL/2 = (Ω/2vg)L ≪ 1,散射过程即可实现准相位匹配。图2a展示了通过AMF工艺制备的光子芯片横截面。为实现声光调制器,首先采用脉冲直流物理气相沉积(PVD)系统26−29在光子芯片的SiO2层暴露硅表面上溅射了340 nm厚、含30% Sc的AlScN层(图2b)。随后通过旋涂和电子束光刻在芯片上图案化叉指电极(图2c)。接着蒸发并图案化75 nm厚Au层(以10 nm Ti作为粘附层),通过剥离工艺制备IDT电极(图2d)。IDT指条间距700 nm经过优化,用于激发5.5 GHz的声表面波(SAW)。通过旋涂光刻胶并图案化形成声换能器的低电阻总线及焊盘。最后蒸发400 nm厚Au层(以10 nm Ti作为粘附层),通过剥离工艺制备声换能器的总线与焊盘。

图2. (a) 采用AMF代工工艺制造的带氧化物开口的芯片横截面。(b) 在芯片上溅射AlScN。(c) 电子束光刻胶的沉积和图形化。(d) 使用剥离工艺蒸发和图形化金叉指结构。(e) 用于金总线和焊盘的光刻胶旋涂和显影。(f) 图形化金总线和焊盘。(g) 使用AMF SOI平台制造的芯片的显微照片。

(h) 在芯片上靠近光波导的位置制造了20对、150 μm长的声换能器,用于声光调制。(i) 声换能器和光波导的扫描电子显微镜(SEM)图像。(j) 金叉指换能器的放大视图。

图2g,h分别展示了制备的150 μm长、具有20对指条的声光器件显微图及其放大视图,对应的SEM图像见图2i,j。AlScN沉积质量分析详见支持信息第1节。

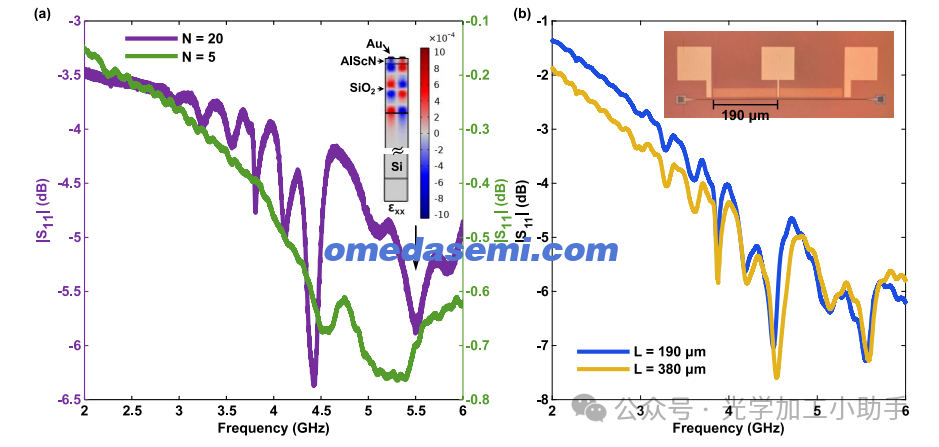

通过矢量网络分析仪(VNA)对商用光子芯片上的声换能器进行表征。使用空气共面探头进行2-6 GHz单端口频率扫描。测试前通过开路-短路-负载校准VNA至探头尖端。图3显示了声换能器的电反射系数(S11)随频率变化的响应,其中射频功率向声波的转换表现为反射功率谱中的凹陷(对应激发SAW的频率)。

图 3. (a) 为比较指状对数量而制造的器件的 S11 响应。紫色和绿色曲线分别对应长度为 150 μm、指状对数为 20 和 5 的器件的响应。插图:有限元 (FEM) 模拟显示谐振频率在 5.5 GHz 左右时的应变分布(适用于所有换能器)。由于应变较大,预计 5.5 GHz 模式的声光调制器 (AOM) 效率更高。指状对数为 5 的换能器的响应带宽更大;然而,指状对数为 20 的器件与源阻抗的匹配性更好。(b) 为研究相互作用长度而制造的器件的 S11 响应。蓝色曲线显示长度为 190 μm 的 IDT 响应,而黄色曲线显示长度为 380 μm 的 IDT 响应。两个器件均具有 20 个指状对。插图:用于相互作用长度分析的制造器件的显微照片。较短的器件使用放置在左侧和中间焊盘上的 SG 探针进行测量,而较长的 IDT 则使用放置在三个焊盘上的 GSG 探针进行测量。

如图3所示,换能器在约4.5 GHz和5.5 GHz处呈现两个显著响应,符合预期的sin(x)/x分布30−32。通过COMSOL Multiphysics对IDT的传播模式进行仿真(图3a),结果验证了这两个主模的存在。由于硅波导中5.5 GHz模式的应变强度高于4.5 GHz模式(应变场局限于芯片的Au/AlScN/氧化物层堆叠中),且IDT间距p = λ/2 = v/2f(v为介质声速,λ为声波长)32,33针对5.5 GHz设计,因此该模式下更强的应变将产生更显著的声光调制效应。SAW速度通过COMSOL仿真计算后用于优化IDT间距,5.5 GHz模式下硅波导内应变分布详见支持信息第2节。声传播损耗通过制备不同传播距离的声延迟线结构表征,分析细节见支持信息第2节。

为研究IDT指对数(N)对声光调制带宽的影响,制备了两种150 μm长、不同指对数的SAW换能器。图3a的S11测量表明,20指对的IDT相比5指对器件具有更好的源阻抗匹配,但后者带宽更大,符合SAW换能器带宽与指对数反比的预期31,32,34。这一对比清晰展示了声波强度与带宽在指对数间的权衡,详细分析见支持信息第3节。

除指对数差异外,还制备了不同孔径长度的IDT以研究其对声光响应的影响。图3b展示了190 μm和380 μm互作用长度的20指对器件的S11响应。因焊盘布局差异,测试时分别采用信号-地(SG)探头(中心与左侧焊盘)和地-信号-地(GSG)配置(380 μm器件),测试配置影响见支持信息第4节。

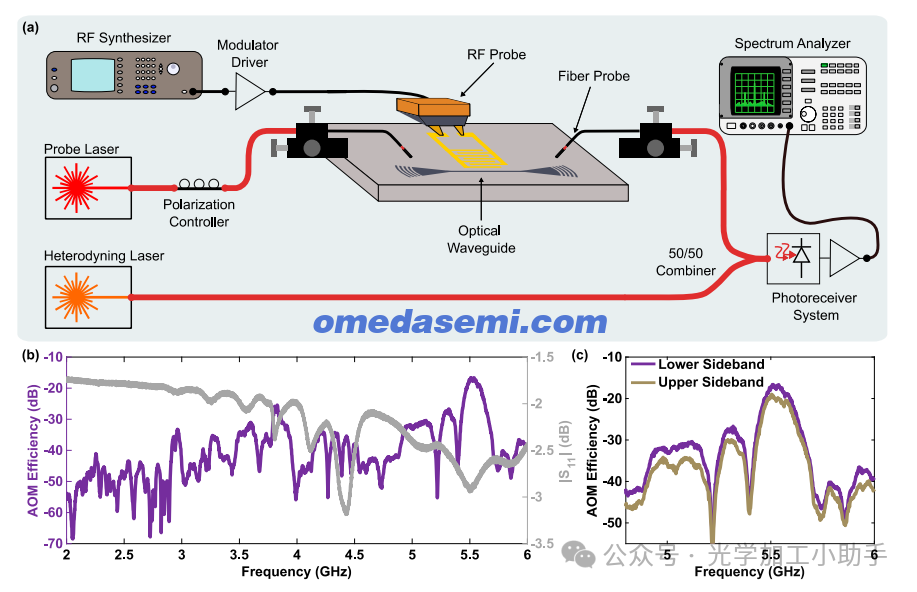

图 4. (a) 用于测量声光调制器 (AOM) 效率的异差装置。探测激光器通过光纤探针和光栅耦合器耦合到芯片。

射频合成器的输出被放大,用于驱动叉指换能器 (IDT)。芯片的光输出通过 50/50 光纤合束器与异差激光器(工作波长略有不同)的输出进行合束。合束器的输出由光接收系统进行光电探测和放大。最后,使用频谱分析仪对调制信号进行分析。原理图中,红线和黑线分别表示光路和电路。(b) 调制器的下边带声光调制器 (AOM) 效率(输出功率以拍音功率为标准)的频谱,以及 150 μm 长、20 个指对的叉指换能器 (IDT) 器件的 S11 响应。 (c)对于具有 20 个指状结构对的 150 μm 长器件,谐振峰附近的下边带(紫色)和上边带(棕色)信号的声光调制效率。

采用外差检测方案(图4a)测量调制效率:可调谐激光器(Agilent 81642A,1550 nm,5 dBm)输出经偏振调整后通过光栅耦合器入片,射频合成器信号经调制驱动器放大后驱动声光调制。调制光经另一可调谐激光器(Agilent 81682B)拍频后由光接收系统(Thorlabs RXM40AF)探测。设置两激光器波长差使拍频约7 GHz,扫描射频频率(2-6 GHz)并通过频谱分析仪(HP8563E)监测拍频功率与调制边带,选取目标边带进行分析。图4b显示了20指对150 μm器件的归一化下边带效率(射频功率23.2 dBm),主谐振峰位于5.5 GHz。图4c显示谐振峰附近上下边带效率对称分布,微小差异源于实验系统频率相关损耗(边带频差为2f,f为声波频率)。

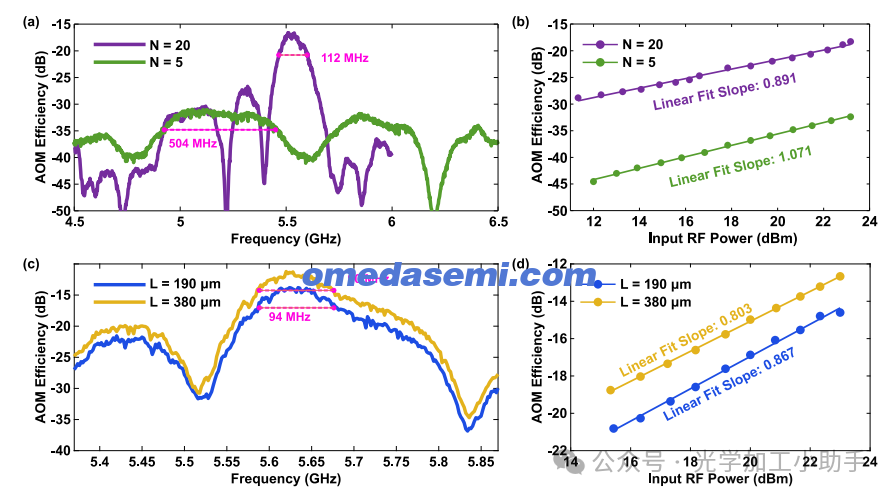

图 5. (a) 150 μm 器件(指对数分别为 20 和 5)的 AOM 响应比较。紫色和绿色线分别表示

指对数为 20 和 5 的器件谐振点附近的 AOM 效率。粉色虚线表示 3 dB 带宽。(b)

下边带 AOM 效率随射频信号功率变化的特性。紫色和绿色圆圈分别表示 150 μm 长 IDT 器件(指对数分别为 20 和 5)的 AOM 效率测量值,紫色和绿色线分别表示数据的线性拟合。斜率 ∼1 表示测得的效率与施加的输入射频功率之间存在线性关系。(c) 20 指对器件(相互作用长度分别为 190 和 380 μm)的 AOM 响应比较。蓝线和黄线分别表示相互作用长度为 190 μm 和 380 μm 的 20 指对器件在谐振点附近的声光调制器 (AOM) 效率。粉色虚线表示 3 dB 带宽。(d) 孔径长度为 190 μm 和 380 μm 的 20 指对器件的输入射频功率扫描结果。蓝色圆圈和黄色圆圈分别表示相互作用长度为 190 μm 和 380 μm 的器件的声光调制器 (AOM) 效率测量值,蓝线和黄线分别表示数据的线性拟合。

对比20指对与5指对150 μm器件的性能(图5a),后者以峰值效率下降为代价实现更高带宽:去嵌线缆损耗后,20指对器件在23.2 dBm射频功率下峰值效率-18.3 dB(带宽112 MHz),5指对器件峰值效率-32.2 dB(带宽504 MHz)。射频功率扫描显示下边带效率随功率线性增加(图5b),据此估算20指对与5指对器件的有效折射率变化分别为4×10−4与8×10−5,对应VπL分别为1.12 V·cm与8.48 V·cm。

对比190 μm与380 μm孔径的20指对器件(图5c,d),在23 dBm射频功率下,190 μm器件效率-14.6 dB(3 dB带宽94 MHz),380 μm器件效率-12.7 dB(带宽90 MHz),对应Δneff分别为4.8×10−4与3×10−4,VπL分别为0.93 V·cm与1.1 V·cm。效率提升受器件阻抗变化与测试方案影响,详见支持信息第4节。

■ 结论

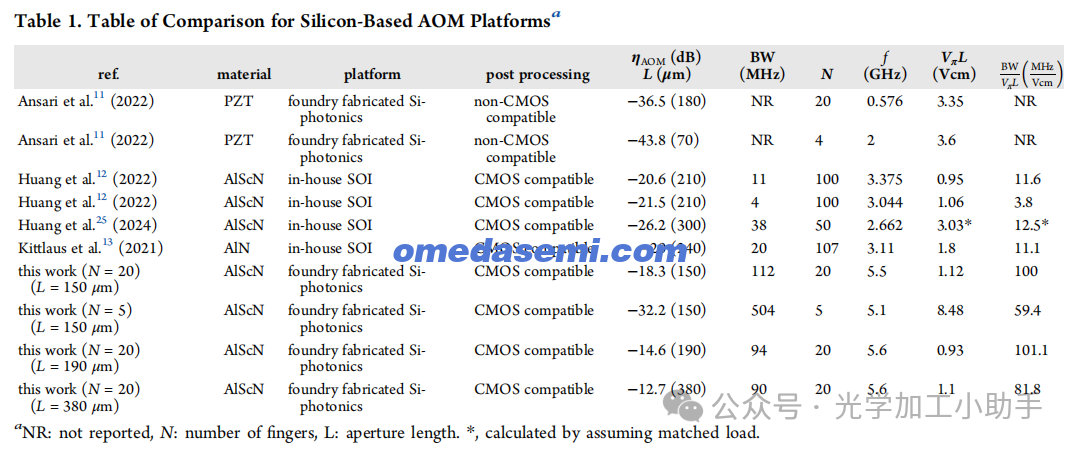

表1对比了本研究器件与同类工作的性能:380 μm长20指对IDT实现-12.7 dB效率(表内最高);150 μm长20指对器件带宽112 MHz(CMOS兼容工艺器件的两倍以上);5指对器件带宽较其他工作提升超一个量级;工作频率(~5.5 GHz)显著高于其他报道(0.576-3.375 GHz)。本集成AOM平台是唯一采用CMOS兼容工艺在代工厂芯片上集成声换能器的方案。

电光调制器的重要优值VπL综合了效率、功耗与尺寸,但未涵盖带宽这一窄带AOM关键指标。本研究表明SAW基声光调制器中效率与带宽存在明确权衡,因此提出更适用于AOM的优值FOM II = BW/VπL,其综合效率、功耗、尺寸与带宽,且不受指对数与孔径长度影响(支持信息第3、4节)。本工作所有器件的FOM II均超其他工作四倍以上,190 μm长20指对器件优值提升近一个量级,凸显了器件优越性。

器件性能优势源于制造质量与设计优化:高质量AlScN沉积于代工光子芯片上(支持信息详述),结合Sezawa模式激发(图3a插图示5.5 GHz模式在Si波导层所在的SiO2-AlScN界面处应力最大35),实现强声光互作用。未来可通过声反射器实现单向换能器提升效率36,或增加匹配网络改善射频转换效率12。本工作开发的商用硅光工艺AOM平台为高性能、高良率CMOS兼容声光调制器发展奠定基础,助力硅基光电平台实现先进声信号处理能力。

作者;Mertcan Erdil,† Izhar,† Yang Deng, Ella Klein, Zichen Tang, Mohamad Hossein Idjadi, Farshid Ashtiani,Firooz Aflatouni, and Roy H. Olsson, III*