云计算和人工智能的快速发展推动了数据中心对更快光学元件的需求达到前所未有的水平。该领域的一项关键进步是将多个光子元件集成到单个芯片上,从而提高了光收发器的性能。得益于成熟的制造工艺,硅光子学在学术研究和工业应用中都获得了突出地位。该平台将调制器、开关、光电探测器和低损耗波导集成在单个芯片上。然而,1600ZR+ 等新兴标准可能超出了硅基调制器的能力。为了解决这些限制,薄膜铌酸锂已被提议作为硅光子的替代品,它具有低电压长度积和出色的高速调制特性。最近,首次演示了薄膜钽酸锂电路,解决了铌酸锂的一些缺点,从而降低了偏置漂移并增强了对光损伤的抵抗力。

云计算和人工智能的快速发展推动了数据中心对更快光学元件的需求达到前所未有的水平。该领域的一项关键进步是将多个光子元件集成到单个芯片上,从而提高了光收发器的性能。得益于成熟的制造工艺,硅光子学在学术研究和工业应用中都获得了突出地位。该平台将调制器、开关、光电探测器和低损耗波导集成在单个芯片上。然而,1600ZR+ 等新兴标准可能超出了硅基调制器的能力。为了解决这些限制,薄膜铌酸锂已被提议作为硅光子的替代品,它具有低电压长度积和出色的高速调制特性。最近,首次演示了薄膜钽酸锂电路,解决了铌酸锂的一些缺点,从而降低了偏置漂移并增强了对光损伤的抵抗力。

*8寸 X切 Z切薄膜铌酸锂、6寸Z切 X切薄膜钽酸锂 *LNOI-SIN:Wafer to wafer 8 inch *LNOI-SIN:Die to wafer 8 inch *近化学计量比 Z切 X切 Stoichiometric_LNOI/LTOI 薄膜铌酸锂 和钽酸锂晶圆 -----量子应用ALOOI晶圆;--氧化铝薄膜晶圆,键合工艺和镀膜工艺

TAOOI晶圆--氧化钽薄膜晶圆,镀膜工艺

SINOI晶圆;--超低损耗氮化硅薄膜晶圆,

SICOI晶圆;新型量子光学平台

6寸LTOI晶圆批量供应;铌酸锂的有力的竞争对手,薄膜钽酸锂晶圆

8寸LNOI晶圆;8寸LNOI助力更大规模薄膜铌酸锂产品量产

LN/LT-SOI/Si/SIN W2W&D2W异质集成

流片: 6寸 氮化硅 铌酸锂 硅光 超高性价比流片, 1个BLOCK的价格买一整片晶圆

划重点--全国产-超高性价比-6 寸硅光-氮化硅-铌酸锂流片白皮书

因此,它成为下一代光子平台的有希望的候选者。

然而,这种平台的一个持续存在的缺点是锂污染,这使得与 CMOS 制造工艺的集成变得复杂。在这里,我们首次展示了将钽酸锂集成到硅光子芯片上。这种集成是在不修改标准硅光子工艺设计套件的情况下实现的。我们的设备实现了低半波电压(3.5 V)、低插入损耗(2.9 dB)和高速运行(> 70 GHz),为下一代应用铺平了道路。通过最大限度地减少钽酸锂材料的使用,我们的方法降低了成本,同时利用了现有的硅光子技术进步,特别是支持超快单片锗光电探测器和成熟的工艺设计套件。

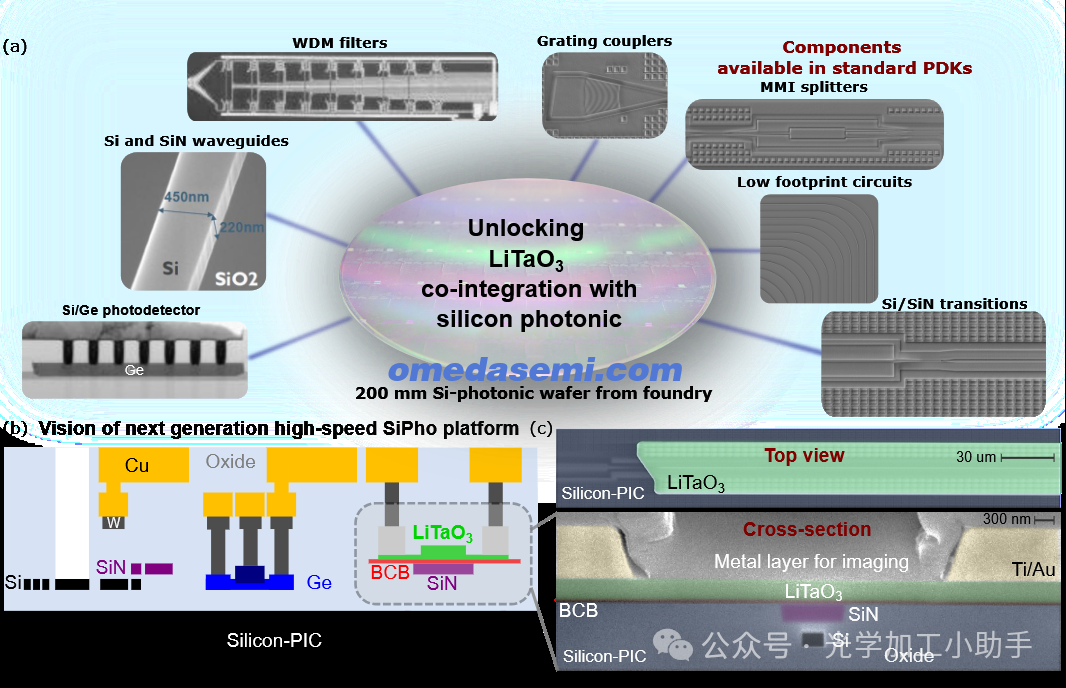

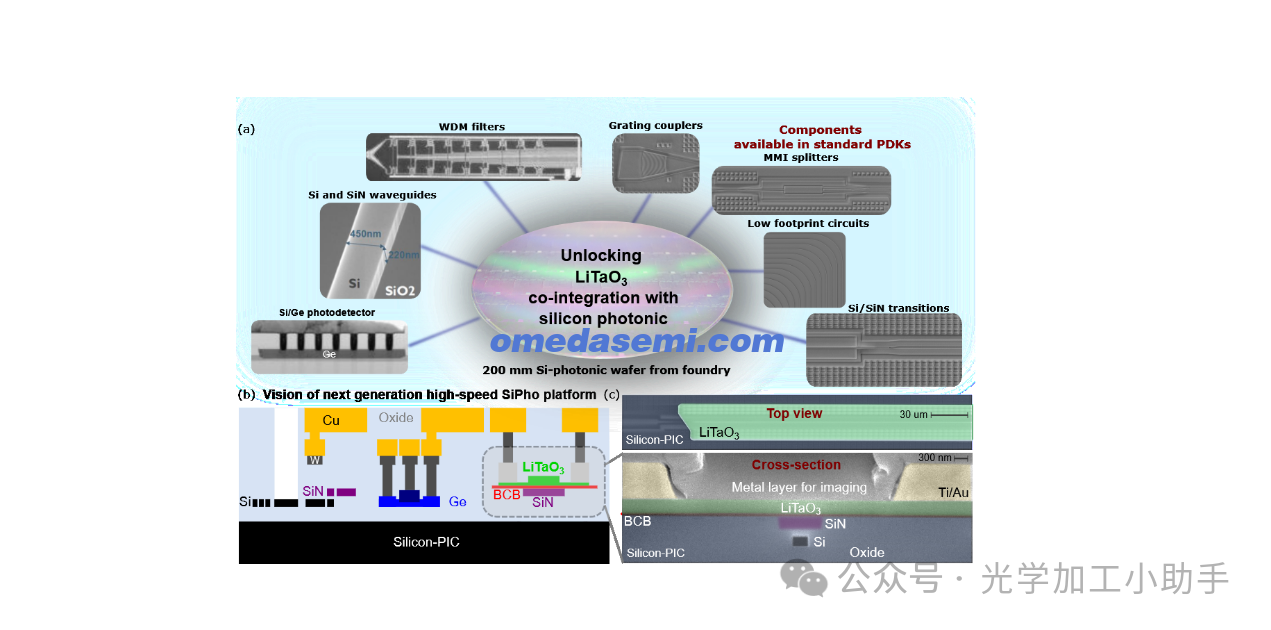

图 1. 下一代高速硅光子平台。(a)最先进的 Si-PIC 平台及其基本组件的通用视图。(b)高速 Si-PIC 横截面的视图:除了已经提供的组件外,还需要集成钽酸锂调制器。(c)在 Si-PIC 上集成 LiTaO3 后的 SEM(彩色)图片和 Si-PIC 上异质电光设备的 FIB 横截面(彩色)。

数据网络流量的指数级增长导致数据中心的功耗水平难以持续。为了应对这一挑战,光纤为这些数据中心内部和之间的数据传输提供了有效的解决方案。光子集成最初是在磷化铟1上开发的,最近在硅光子平台上开发,它显著增强了数据流的扩展,同时最大限度地降低了功耗2。硅光子集成电路 (Si PIC) 能够密集集成复杂的功能,利用与 CMOS 兼容的制造工艺实现大批量、高产量和低成本生产。典型的硅光子平台(见图 1)集成了几个关键组件,包括用于高速调制的掺杂硅波导、用于高效低速热调谐的加热器、用于低损耗传播和高质量滤波的氮化硅 (SiN) 层以及锗光电探测器。后者已证明带宽超过 200 GHz3。然而,新兴标准(如 1600ZR+4)可能需要超过 200 GBd 的波特率,这超出了当前 Si 光子调制器的性能极限。

为了克服这一限制,各种替代平台正在研究中,新型电光 (EO) 材料的异质集成引起了广泛关注。钛酸钡 (BTO) 是一种很有前途的选择,因为它能够在 Si 层上直接生长,并且与 CMOS 制造工艺兼容5。虽然已经实现了高速操作,但高介电常数色散和恒定偏置要求等挑战仍然存在。替代方法包括有机材料6、等离子体7-9、III-V 半导体10,11 和石墨烯12-16 的集成。然而,薄膜铌酸锂 (TFLN) 已成为一种出色的材料,它兼具低光学损耗和强大、快速的 EO 系数 17。在演示中,已实现超过 100 GHz18 的带宽。此外,铌酸锂 (LiNbO3) 已异质集成到 Si 和 SiN 平台上:已成功采用晶圆键合19,20 和微转印印刷等技术21。

最近,钽酸锂 (LiTaO3) 已成为 LiNbO3 的替代品 22–25。该材料具有与 LiNbO3 相似的 EO 系数。然而,它显示出更弱的光折变效应和更高的损伤阈值。直流稳定的 LiTaO3 EO 调制器已被证明26。到目前为止,只展示了单片平台上的演示。然而,与单片 LiNbO3 光波导平台一样,由于锂造成的污染,在 CMOS 工厂实现大批量生产的途径尚不明确27。

此外,目前还不清楚其他组件(如高速探测器)的集成情况。

在这项工作中,我们首次展示了 LiTaO3 到 Si-PIC 的异质集成。

集成调制器与 Si PIC 的工艺设计套件 (PDK) 兼容,确保与平台组件完全兼容并实现其最佳功能。利用现有的 PDK,我们实现了 EO 组件的无缝集成,而不会损害现有组件的性能。

使用基于微转移印刷的后端集成方法,我们确保与整个晶圆堆栈的兼容性,从而促进与加热器、滤波器和锗光电探测器等关键组件的共同集成。概念图如图 1 所示。

此外,印刷技术允许反转极化轴,从而可以实现复杂的电极设计,从而实现差分驱动,例如接地信号-信号-接地 (GSSG),这在单片 LiNbO3 平台或晶圆键合设备上几乎不可能实现。

因此,由于偶数阶谐波的消除,此类调制器可以由具有改进线性度的差分驱动器驱动28。此外,这些差分驱动器还具有更好的对电磁干扰 (EMI) 或电源噪声的耐受性,这在多通道设备中尤为重要。本文提出的非平衡 Mach-Zehnder 调制器 (MZM) 实现了超过 70 GHz 的测量带宽(受测量设备限制),估计可以达到 90 GHz。它还表现出 2.3 V´cm 的电压长度积,与单片 LiTaO3 平台的最新结果相当24。通过优化混合 SiN/LiTaO3 横截面,可以进一步提高性能。此外,Mach-Zhender 臂中的混合相位调制器的总插入损耗为 2.9 dB,主要由制造错位(1.6 dB)造成的金属损耗引起。最后,成功演示了高达 190 GBd 的数据调制,突出了这种方法在下一代高速光子应用中的潜力。

结果

LiTaO3 MZM 的设计和制造

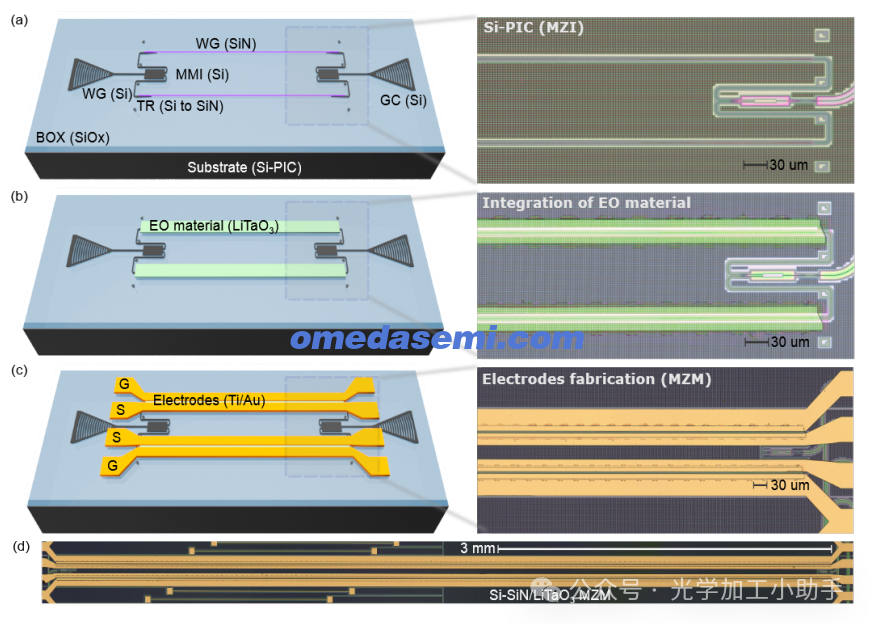

图 2. LiTaO3 在 Si-PIC 上的集成流程。(a) 无源 Si 和 SiN 电路的架构和相应的光学显微镜图片。WG:波导,BOX:埋层氧化物,TR:过渡,GC:光栅耦合器,MMI:多模干涉仪,

MZI:马赫-曾德干涉仪。(b) LiTaO3 集成后的混合调制器架构和相应的光学显微镜图片。(c) 电极制造后的马赫-曾德调制器架构和相应的光学显微镜图片。G:接地,S:信号。(d) 7 毫米长的异质 Si 和 SiN/LiTaO3MZM 的概览。

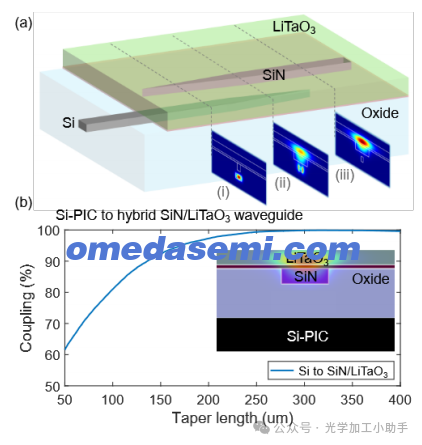

图 3. 从 Si 波导到混合调制器的过渡。(a)三层绝热过渡示意图:

添加了感兴趣区域中的模式分布。(b)从完全蚀刻的 Si 波导到混合 SiN/LiTaO3 相位调制器的预期传输(插图)和 MZM 臂的无源堆栈的横截面。

该器件架构依赖于在尖端 Si-PIC 平台 (imec iSiPP200) 上实现的 MZM。商业平台的子集用于器件布局和电路布线。这里只处理硅和硅氮化物波导层。从具有 220 nm 器件层的绝缘体上硅 (SOI) 晶片开始,Si 层采用两种蚀刻深度 (70 nm 和 220 nm) 进行图案化。接下来,将晶片平坦化并沉积厚度为 300 nm 的 SiN 层。对该层进行图案化 (完全蚀刻 300 nm),并覆盖氧化物,之后将晶片平坦化。调制器的布线和分割在硅氮化物波导层中完成。 MZM 中的 50:50 分光器和合光器是 1x2 多模干涉仪 (MMI),可在 PDK 中使用。使用光栅耦合器 (GC) 将光耦合进和耦合出芯片,并通过包含在 PDK 中的单模波导进行路由。图 2a 描绘了无源器件架构的示意图和制造电路的光学显微镜图片。在后端异质集成步骤中,X 切割薄膜 LiTaO3 被整合到 MZI 的两个臂上,从而实现混合相位调制器。这种 EO 材料的集成是使用微转移印刷技术实现的29,30。微转移印刷工艺允许转移具有大长宽比的薄膜。在这里,使用商用 LTOI 晶圆作为转移源,在其上制备悬浮的 LiTaO3 膜。这些膜的厚度为 300 nm,宽度为 30 µm,长度为 7 mm。悬浮膜的制造工艺流程和后端集成的详细信息在方法部分提供。然后,在芯片上涂上一层 50 nm 厚的 BCB 作为粘合剂后,使用商用微转移打印机将这些膜转移到光子芯片上。源晶圆上的高膜密度允许在 4 英寸晶圆上制造超过 12000 个膜(7 mm x 30 µm),展示了对昂贵电光材料的有效利用。图 2b 显示了该装置的示意图以及在平台上成功集成 LiTaO3 后的相应光学显微镜图片。利用微转移印刷方法的多功能性,调制器以推挽配置运行,印刷的 LiTaO3 膜彼此成 180° 角。这允许使用具有差分输出 28 的集成电子驱动器。集成后,最终的金属化步骤包括使用剥离工艺沉积 20 nm 的钛 (Ti) 层,然后沉积 1 µm 的金 (Au) 层。此步骤是必需的,以在设备臂顶部形成以接地-信号-信号-接地 (GSSG) 排列的金属电极。图 2c 显示了最终 MZM 的示意图以及详细的光学显微镜视图。图 2d 显示了整个调制器。该器件的一个关键特性是将来自 Si 波导的光有效耦合到 MZM 的混合 EO 部分。这种耦合是通过绝热过渡实现的。在设计中,Si 光子平台的 Si 层和 SiN 层均用于最大限度地减少进入 EO 结构的耦合损耗。图 3 显示了耦合结构的示意图以及每个感兴趣区域的光学模式曲线。通过 Si/SiN/LiTaO3 的垂直三层堆叠,过渡被设计为能够抵抗制造几何变化,例如 SiN 和 LiTaO3 的层厚度或波导尺寸。图 3.b 中所示的模拟传输效率是使用商业软件 Ansys Lumerical MODE 中实现的特征模式扩展 (EME) 方法计算的,适用于一系列锥度长度,并表明在这种混合结构中耦合效率几乎可以达到 100%。方法中提供了有关绝热过渡设计的更多详细信息。排除耦合部分,有源 EO SiN/LiTaO3 波导的有效长度减少到 6.6 毫米,而调制器臂的原始长度为 7 毫米,因为选择了 200 微米的过渡长度。调制器的性能制造的 MZM 具有光学和电光特性。初步表征涉及 O 波段的传输波长扫描,范围从 1300 nm 到 1325 nm。使用可调激光器将连续波 (CW) 光功率耦合到芯片。

通过光纤和偏振控制器,横向电 (TE) 模式通过光栅耦合器在波导中激发。使用功率计记录通过 MZM 传输的光功率,同时在同一结构组上,进行参考波导传输扫描以考虑光栅耦合器的贡献和Si 布线。

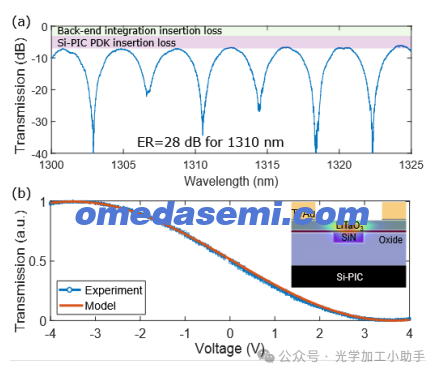

图 5. 调制器的准直流特性。(a) 调制器传输随波长变化的测量(b)调制器随施加电压和模拟响应变化的归一化传输,以及(插图)MZM 臂全堆栈的横截面。

得到的归一化 MZM 透射光谱绘制在图 5.a 中,其中干涉图样显示了光谱干涉图样,其自由光谱范围 (FSR) 为 4 nm,消光比 (ER) 在波长 1310 nm 处为 28 dB。然而,除了平台 PDK 定义的 MZM 结构的 3.8 dB 插入损耗之外,高速电光调制部分还引入了额外的 2.9 dB 插入损耗,包括耦合 (0.6 dB) 和传播损耗 (0.7 dB)。剩余的损耗归因于最终金层约 0.6 µm 的错位,这引入了额外的 1.6 dB 光损耗。有关 MZM 损耗的更多详细信息,请参阅方法部分。

接下来,该设备在准直直流调制实验中运行。传输的连续波(CW)光信号在低电频下进行调制,以表征半波电压(Vπ)。该设备由一个频率为100 kHz的射频(RF)三角波驱动,该信号由射频信号发生器生成,同时选择1309.26 nm的光波长,与调制器的四分之一操作点相对应,使得调制器能够在线性调制模式下工作。电信号通过射频探针应用到设备上,设备传输的光功率通过光电探测器和示波器记录。然后,将结果作为施加电压的函数绘制出来。结果如图5.b所示,显示单相移器(MZM的一个臂)的Vπ为7.0 V,对应于推拉幅度调制配置中3.5 V的电压(MZM的两个臂)。这导致了一个电压-长度乘积(VπL)为2.3 V·cm,符合近期关于在LiTaO3-on-insulator(LTOI)平台上制造的LiTaO3 MZM的报告。此外,将这一结果与使用有限元法(FEM)仿真结合分析模型计算的预期Vπ曲线进行比较,显示出与测量结果的良好一致性,如图5.b中的重叠部分所示。关于Vπ仿真更多的信息,请参见方法部分。

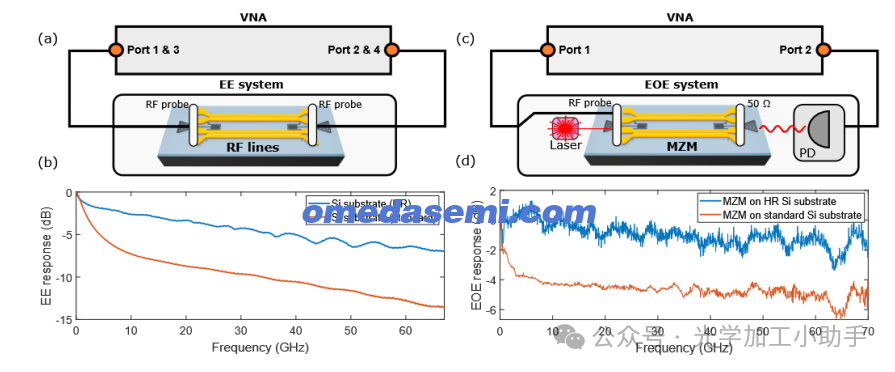

设备的高速响应通过两种方式进行表征:首先,通过执行电到电(EE)测量来表征电极,然后测量完整的电到光到电(EOE)响应。EE响应使用连接到芯片的一组GSSG探针的矢量网络分析仪(VNA)进行测量,如图4.a所示。该测量在两个不同的芯片上进行。在第一个芯片上,射频线路被放置用于驱动一个制造在常规硅基片上的MZM。在第二种情况下,使用了高电阻硅基片。图4.b中呈现的两条线路的比较显示,使用高电阻硅基片时,由于射频波在基片中的吸收损失较低,射频带宽得到了明显的增强。

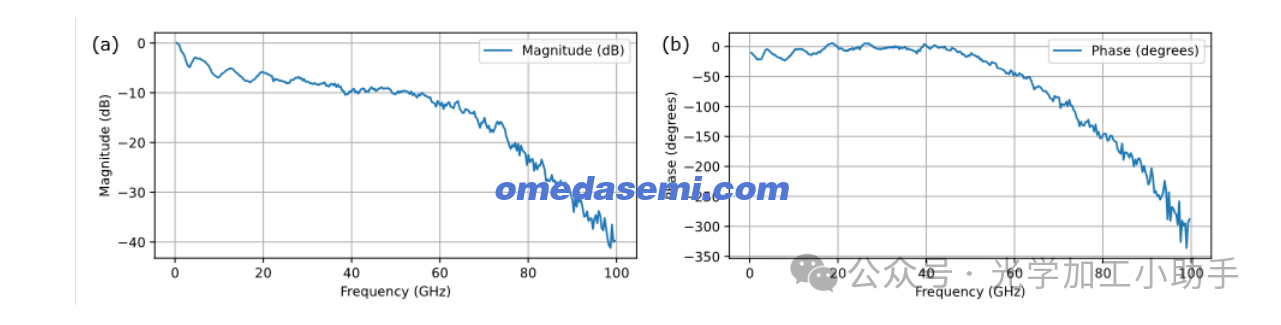

图 4. 调制器的高速特性。(a)用于 RF 线频率响应特性的测量装置(EE 系统)。(b)结果显示使用常规 Si 衬底和高电阻率衬底的比较。(c)用于调制器频率响应特性的测量装置(EOE 系统)。(d)结果显示使用常规 Si 衬底和高电阻率衬底在平台上集成的调制器的比较。

然后,使用类似的实验设置(图4.c)测量在标准和高电阻硅基片上制造的MZM的EOE响应。设备通过GS探针连接到VNA的一个端口,设备的另一端则通过50 Ω负载终端,以防止远端的电反射。连续波光功率通过光纤从激光器耦合到硅光子集成电路(Si-PIC),经过MZM传输,出耦并通过高速光电探测器转换为电信号。最终信号在VNA的第二个端口接收。图4.d中展示了两种调制器类型的EOE频率响应。再次,使用高电阻基片的设备显示出超过70 GHz的明显更高的3-dB截止频率,这一频率受到实验设置(VNA和光电探测器带宽)的限制。

数据传输

图 6. 数据传输实验。(a)眼图测量的测量设置。(b)NRZ(蓝色)和 PAM4(红色)测量信号的传输位序列中的误码率 (BER)。水平虚线表示前向纠错 (FEC) 的阈值,开销为 15%。(c)112 GBaud NRZ、(d)180 GBaud NRZ、(e)112 GBaud PAM4、(f)140 GBaud PAM4 的眼图,所有图均在发射机端使用校正,在接收机端使用 64 抽头 FFE,但是,没有进行离线数字后处理

作为示范,该设备用于一个链路中传输数据,实验设置如图6.a所示。通过256 GS/s的任意波形发生器(AWG)生成差分信号,使用GSSG探针将其应用于设备。第二个探针用于在传输线的另一侧终端设备,连接两个50 Ω负载,以防止电反射。光信号通过掺钕光纤放大器(PDFA)放大,然后由高速光电探测器检测。检测到的信号随后通过采样示波器记录。为了优化传输,对链路进行了表征,以便平衡AWG生成的信号。因此,清晰的眼图被生成。附加数据图3展示了数据传输链路的测量频率响应(幅度在a中,相位在b中),该响应在AWG处进行了补偿。链路表征中大约70 GHz处观察到明显的性能下降,归因于电缆、射频探针、高速光电探测器和AWG的带宽限制。所有传输信号基于标准化的伪随机比特序列(PRBS-15)。

在接收端应用了一个64位前馈均衡(FFE)算法,使用采样示波器的软件增强接收信号。图6.b展示了从生成的眼图中推导出的比特误码率(BER),采用非归零(NRZ)和脉冲振幅调制4级(PAM4)格式。虚线表示具有15%开销的前向纠错(FEC)算法的BER阈值。图的下限为3×10^-4,表示在此误码率阈值以下,由于演示中传输的比特数量有限,无法进行统计显著性的评估。图6还包括了代表性的眼图,所有图都结合了FFE。

讨论

性能提升

高速混合电光/硅光子集成电路(EO/Si-PIC)调制器被设计用于集成到数据通信系统中,包括数据中心间和数据中心内的链路,以实现大规模数据传输。在这种系统中,功耗是一个关键参数。所展示的设备在这方面展示了显著的优化潜力,特别是通过减少电驱动功率来实现优化。

最近,已演示了高质量的LiTaO3刻蚀过程。通过采用这种刻蚀工艺,混合调制器中的LiTaO3层可以进行图案化。图案化的LiTaO3层可以提供更好的约束,因此由于电极间距可以减少,光电效应变得更强(见方法部分)。因此,间隙可以从5.5 µm减少到3.4 µm,导致更强的射频场和模拟的更低Vπ值(2.7 V),对应于模拟的电压-长度乘积为1.8 V·cm。如方法部分所述,在这种配置下,可以在平台上制作高效的绝热耦合器,允许超过99%的高耦合效率。此外,合理的设计允许在LiTaO3脊波导的横向错位高达0.5 µm时,仍能保持非常高的耦合效率(>99%)。这些错位仍然在晶圆级微转印工具的对准精度规范内。

结论

成功实现了锂钽酸盐在硅光子平台上的异质集成,并且插入损耗最小。我们的方法在标准的200毫米Si-PIC平台上实施,确保了与现有平台PDK组件的无缝集成,同时保持其性能。通过利用后端集成,我们保持了整个晶圆堆栈的兼容性,使得与波导、加热器、滤波器和锗光电探测器等关键组件的高效共同集成成为可能。制造的MZM实现了超过70 GHz的带宽,受限于测量设置,并且展现出与已展示的LTOI平台相当的2.3 V·cm的电压-长度乘积。MZM臂中的混合相位调制器引入了额外的2.9 dB插入损耗。最后,进行高速传输实验,达到190 Gbaud(NRZ)的符号速率和超过320 Gbit/s(PAM4)的数据速率。

这些结果标志着向高速、高性能混合锂钽酸盐光子平台迈出了重要一步。它们为可扩展的、与行业兼容的电光集成铺平了道路,用于低能耗的数据通信链路,并且能够大规模生产。

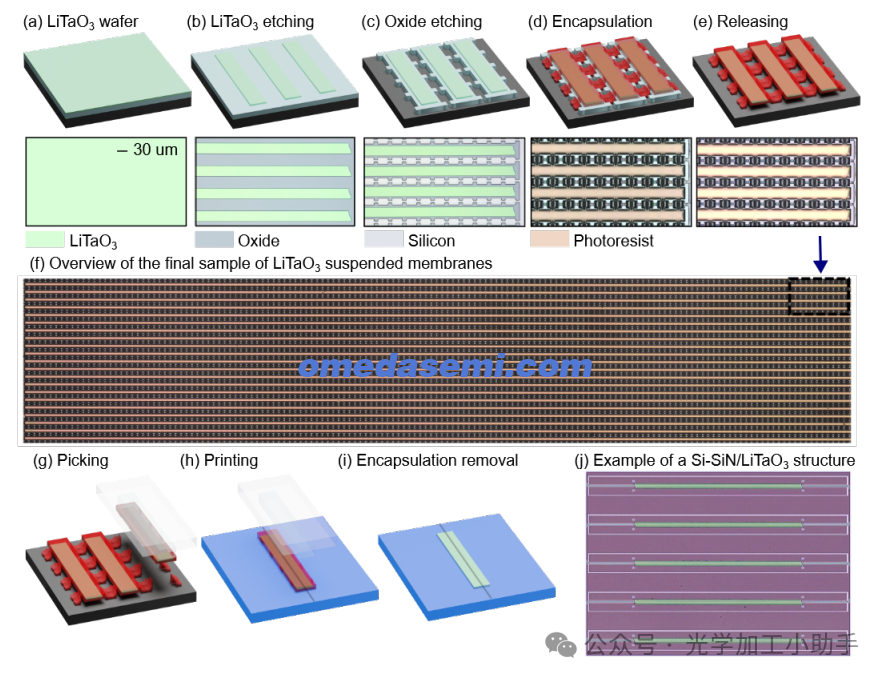

异质 LiTaO3 集成工艺流程

悬浮 LiTaO3 膜的制造始于在 Si 衬底晶片上放置 2 µm 氧化物上的 300 nm LiTaO3(补充数据图 1.a)。使用适合于氩气 (Ar) 基反应离子蚀刻 (RIE) 的非晶硅 (aSi) 硬掩模,利用紫外光刻技术将 LiTaO3 图案化为 30 µm x 7 mm 的矩形。然后在氢氧化钾 (KOH) 溶液中去除 aSi 硬掩模(补充数据图 1.b)。作为第二步,使用紫外光刻技术和 RIE 对氧化物层进行图案化,然后将氧化物蚀刻到 Si 衬底上(补充数据图 1.c)。然后添加机械封装层,该层由使用紫外光刻技术曝光的光刻胶层组成,随后进行显影。光刻胶封装中的图案是为了定义从 Si 基板到 LiTaO3 膜的机械连接而制作的,从而允许在释放器件时悬浮 LiTaO3(补充数据图 1.d)。最后一步是在湿蚀刻剂中释放 LiTaO3 膜:缓冲氢氟酸 (BHF)(补充数据图 1.e)。补充数据图 1.f 中的图片显示了最终样品的概览。在此图中,21 个 30 µm x 7 mm 的膜位于 2 mm x 7 mm 的样品上。膜密度为 1.5 个膜/mm2,对于 4 英寸晶圆,膜的总数将超过 12 000 个。

补充数据图 1。制造和印刷悬浮 LiTaO3 膜的连续步骤描述。

(a)LiTaO3(300 nm)/氧化物(2 µm)/Si 晶片(基板)起点。(b)LiTaO3 膜的图案化。(c)氧化物释放层的图案化。(d)光刻胶机械封装结构。(e)切割(释放)氧化物层,使结构悬浮。(f)带有悬浮 LiTaO3 的最终样品的概览。(g)拾取悬浮的 LiTaO3。(h)在预处理的外部芯片上打印 LiTaO3。(i)封装去除。(j)一些成功印刷的 LiTaO3 膜的概览。

在此步骤中,薄膜准备好集成到不同的基板上。它们通过聚合物PDMS印章拾取,印章由商业微转印打印工具驱动(补充数据图1.g)。为了更好的附着力,在打印前向目标基板施加了BCB缓冲层。然后将薄膜放置在宿主基板上,撤回印章,使薄膜停留在最终位置(补充数据图1.h)。随后,使用RIE氧等离子体去除光刻胶封装层(补充数据图1.i),之后在280°C下固化BCB层,时间为90分钟。补充数据图1.j展示了一个Si芯片的示例,该芯片上有一个1毫米长的LiTaO3级联结构,用作插入损耗测试结构。

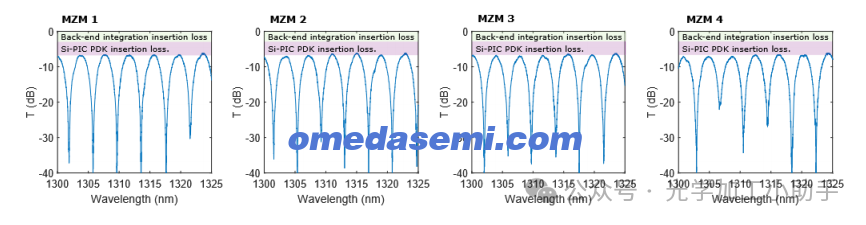

在损耗表征测试结构的基础上,LiTaO3薄膜的集成用于四个MZM设备。为了说明工艺流程的稳定性,记录并展示了设备的波长传输特性,结果如补充数据图2所示。四个设备,总共集成了八个LiTaO3薄膜,显示出相似的结果,1310 nm附近的峰值ER>25 dB。补充数据图2中的波长扫描通过减去光栅耦合器和MZM外部的波导进行了归一化。

损耗表征

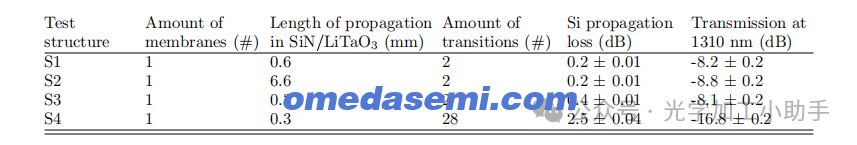

补充数据表。I. 确定 LiTaO3 板的传播损耗和转换损耗所需的所有测试结构的描述和测量传输。

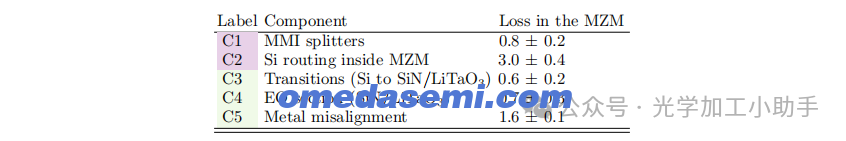

补充数据表。II. 测量 MZM 各组件的损耗,以便提取 Si-PIC PDK(C1 和 C2)和后端集成过程(C3、C4 和 C5)对插入损耗的贡献。

可以区分两种光损耗贡献:通过混合SiN/LiTaO3波导的传播损耗,以及将光从Si波导耦合到混合SiN/LiTaO3波导的耦合或过渡损耗(有关此过渡的更多细节,请参见绝热耦合)。为了确定传播损耗,制造了不同长度的混合SiN/LiTaO3波导。这些波导在补充数据表I中标记为S1和S2,分别具有0.66 mm和6.66 mm的传播长度。对于过渡,准备了两个结构,一个只有两个过渡(一个进,一个出),另一个有28个过渡。它们在补充数据表I中标记为S3和S4,总体上具有相同的传播长度。通过比较所有结构的传输,并考虑Si波导中的传播损耗,可以推导出传播损耗为1.0 ± 0.5 dB/cm,每个过渡的过渡损耗为0.3 ± 0.1 dB。

补充数据图 2. 四个制造的 MZM 的传输 (T) 测量。光栅耦合器和外部布线的损耗被移除。Si-PIC 组件(补充数据表 II 中的 C1 和 C2)的插入损耗贡献和后端集成过程(补充数据表 II 中的 C3、C4 和 C5)的贡献在图表顶部描述。

MZM内部所有组件的损耗也列在补充数据表II中。MMI分路器(C1)和Si波导(C2)的损耗是通过相同芯片上的工艺控制结构测量的。Si到SiN/LiTaO3的过渡(C3)和通过混合SiN/LiTaO3的传播(C4)是通过上面描述的损耗测试结构提取的。此外,LiTaO3上方引入的金属线条(C5)也会引入额外的损耗。观察到约600 nm的错位,可以在FIB切割中看到。由于没有可用的测试结构来量化这一损耗,因此在COMSOL中进行了有限元法仿真,以确定其贡献为1.6 dB。

从Si平台到混合LiTaO3调制器的绝热耦合

优化了一个绝热锥形结构,以高效地将光从Si波导耦合到电光部分。以下段落阐明了描述已制造芯片时提到的锥形部分的设计(混合SiN/LiTaO3-on-Si调制器)。

在过渡开始时,尽管引入了LiTaO3层,但由于两种材料之间显著的折射率对比,如图3.a所示,光仍然被局限在Si波导中。在此阶段,相关的材料堆栈由380 nm x 220 nm的Si波导构成,波导被500 nm厚的氧化层包覆,并且在其上方有一个30 µm x 300 nm的LiTaO3层。在过渡结构中,引入了一个300 nm厚的SiN层,位置位于Si的150 nm上方和LiTaO3的70 nm下方(见图3.a.(i))。在这一点上,SiN波导从狭窄的尖端(150 nm)逐渐展开,确保光模式主要保持在Si中,SiN锥形尖端的影响最小。随后,SiN波导经历了绝热宽度扩展,然后Si波导收缩到150 nm,促进了光模式从Si到混合SiN/LiTaO3配置的渐进过渡(图3.a.(ii))。然后,SiN宽度被调整到其最终值900 nm,以实现混合模式的最佳约束(图3.a.(iii)),这一尺寸是通过在LiTaO3层内尽可能多地保持光以最小化Vπ,并通过实现足够的约束来减轻随后的金属引起的损耗之间的权衡确定的。在此配置下,LiTaO3与Si/SiN波导的横向对准对过渡效率的影响不大。通过在Lumerical中使用EME求解器优化锥形尺寸,最终得到的锥形长度为200 µm。

半波电压计算

Vπ 模拟是使用 COMSOL 中的多个 FEM 模拟和分析模型的组合完成的。

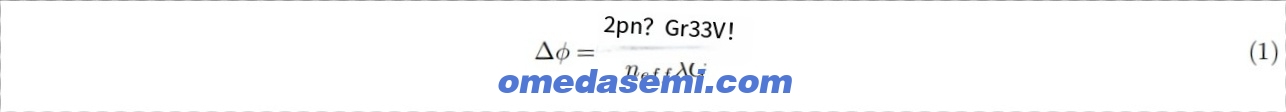

推挽配置中的 MZM 所经历的 EO 相移 (∆ϕ) 由以下表达式控制:

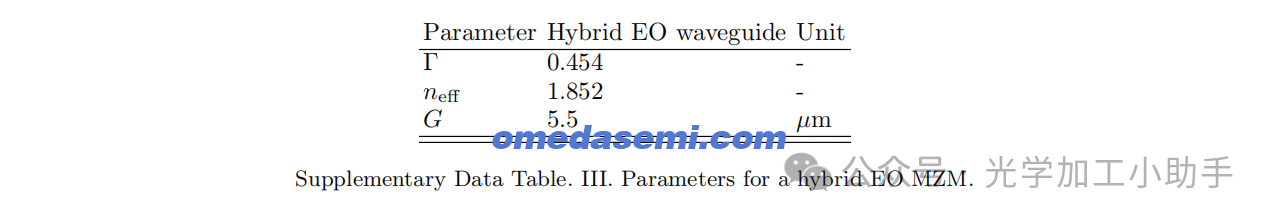

其中,ne = 2.1269 为非常折射率,Γ 表示 RF 模式与光学模式之间的重叠因子,r33 = 30.5 pm/V 为 LiTaO3 的 EO 系数,V 为施加的电压,L = 6.6 mm 为一个调制器臂的有效长度,λ = 1310 nm 为光波长,nef f 为光学模式的有效折射率,G 表示电极间隙。模拟参数(Γ、nef f 和 G)列于补充数据表中。III.

利用该方程和模拟结果,计算得出长度为 6.6 毫米的 EO 段的 Vπ 理论值,对于平板推挽配置,为 3.6 V,这与测量结果高度一致。

补充数据图 3。数据传输链路特性。(a)数据传输链路的幅度和(b)相位特性,用于生成眼图。

作者:Margot Niels1,2,∗,†, Tom Vanackere1,2,∗,†, Ewoud Vissers1,2, Tingting Zhai1,2, Patrick Nenezic1,2, Jakob Declercq2,3,

C´edric Bruynsteen2,3, Shengpu Niu2,3, Arno Moerman2,3, Olivier Caytan2,3, Nishant Singh2,3, Sam Lemey2,3, Xin

Yin2,3, Soe Janssen2, Peter Verheyen2, Neha Singh2, Dieter Bode2, Martin Davi2, Filippo Ferraro2, Philippe Absil2,

Sadhishkumar Balakrishnan2, Joris Van Campenhout2, G¨unther Roelkens1,2, Bart Kuyken1,2,∗, Maximilien Billet1,2.∗

单位:

1

Department of Information Technology (INTEC), Photonics Research Group, Ghent University–imec, 9052 Ghent, Belgium.

2

imec, Kapeldreef 75, 3001 Leuven, Belgium.

3

Department of Information Technology (INTEC), IDLab, Ghent University–imec, 9052 Ghent, Belgium.

†

These authors contributed equally to this work.

云计算和人工智能的快速发展推动了数据中心对更快光学元件的需求达到前所未有的水平。该领域的一项关键进步是将多个光子元件集成到单个芯片上,从而提高了光收发器的性能。得益于成熟的制造工艺,硅光子学在学术研究和工业应用中都获得了突出地位。该平台将调制器、开关、光电探测器和低损耗波导集成在单个芯片上。然而,1600ZR+ 等新兴标准可能超出了硅基调制器的能力。为了解决这些限制,薄膜铌酸锂已被提议作为

云计算和人工智能的快速发展推动了数据中心对更快光学元件的需求达到前所未有的水平。该领域的一项关键进步是将多个光子元件集成到单个芯片上,从而提高了光收发器的性能。得益于成熟的制造工艺,硅光子学在学术研究和工业应用中都获得了突出地位。该平台将调制器、开关、光电探测器和低损耗波导集成在单个芯片上。然而,1600ZR+ 等新兴标准可能超出了硅基调制器的能力。为了解决这些限制,薄膜铌酸锂已被提议作为