摘要:随着器件小型化发展到极限,下一代封装技术作为解决方案的重要性日益凸显。为了突破这一瓶颈,对2.5D和3D互连间距的需求日益增长。这旨在最大限度地减少信号延迟,同时满足小尺寸、低功耗和高I/O数量等要求。由于传统焊料凸点在小型化方面的限制以及高温工艺下的可靠性问题,混合键合技术作为其替代方案正日益受到关注。近年来,SiCN的研究日益活跃,旨在克服和增强Cu/SiO2结构的局限性。本文介绍了Cu/SiCN相较于Cu/SiO2结构的优势,并考虑了各种沉积条件,包括前驱体、沉积温度和基板温度。此外,本文还深入探讨了SiCN的核心机理,例如悬挂键和OH基团的作用以及等离子体表面处理的影响,这些因素解释了SiCN与SiO2的区别。通过本次讨论,我们旨在最终展示应用Cu/SiCN混合键合结构所能实现的优势。

关键词:3D IC封装,混合键合,SiCN电介质,Cu/SiCN

12寸 PECVD

SICN SIN SIO2镀膜代工 代工

12寸混合Cu/SICN键合代工,EVG机台

12寸cu/sicn图案片,用于混合键合调试

用于混合集成,超高的生产效率,颗粒度过关,膜厚均匀

引言

与TCB方式相比,混合键合在低温环境下能够进行加工,这使其在制造对高温敏感的DRAM和高带宽存储器等方面具有优势。此外,Cu-Cu和氧化物-氧化物界面可以同时实现,因此具有较高的加工效率。在这种混合键合结构中,绝缘层作为支撑Cu的加强层,直到Cu-Cu区域形成优异的电气连接,起到了促进Cu有效扩散的作用,因此是非常重要的因素。然而,普遍使用的SiO2不仅容易受到Cu扩散的影响,而且在后端工艺中的化学机械抛光(CMP)过程中,可能会出现腐蚀等缺陷问题。

与此相对,SiCN在机械强度上比SiO2高,能够更好地抵抗CMP工艺中的物理力,并且能够有效地抑制Cu的扩散,因此作为SiO2的替代材料受到了关注。此外,由于SiCN的物质成分比例和等离子体表面处理会导致键合能量的变化,许多相关研究也正在进行中。本论文旨在通过回顾SiCN薄膜的键合特性研究结果,提供对低温Cu混合键合中SiCN绝缘膜特性的更深入理解。

2.1. Cu/SiO2与Cu/SiCN混合键合工艺

Cu/SiO2结构是目前最常用的混合键合结构,属于定义为DBI技术的混合键合领域。在Cu/SiO2混合键合中,CMP工艺的重要性非常高,因为它决定了表面粗糙度和平坦度以及Cu的溶解度。

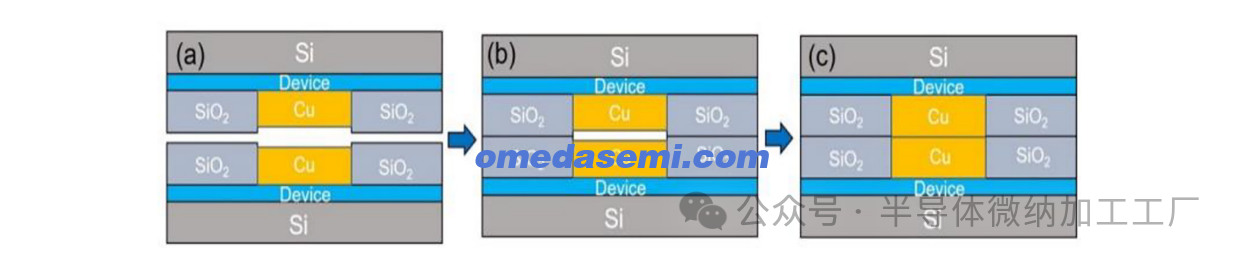

图 1. Cu/SiO2 混合系统理想键合机制示意图。(a) SiO2 通孔中带有 Cu 凸块的侧面。Cu 凸块的高度略低于周围的 SiO2 层。(b) 室温下 SiO2 与 SiO2 之间的对准和键合。

(c) 加热以缩小凹陷间隙并在 Cu 凸块内产生压力。该压力是由于 Cu 的热膨胀系数较大而产生的。第三阶段无需外部压力。2)

如图1所示,在Cu混合键合的CMP工艺之后,最终Cu的高度略低于包围Cu的SiO2薄膜。

通过这种结构,键合时首先发生SiO2-SiO2的结合,然后在退火处理后,由于Cu的热膨胀系数大于SiO2,内部应力使两个Cu表面之间的间隙得到填补,通过Cu之间的相互扩散形成强的键合界面。为了实现高质量的键合界面,调节Cu的溶解度非常重要。如果溶解度过低,Cu的膨胀会对SiO2层造成过大的压力,可能导致SiO2层破裂。反之,如果溶解度过大,Cu的膨胀无法克服pad之间的间隙,可能无法实现Cu-Cu的结合。溶解度的形成过程会受到所施加温度的影响,高温环境下Cu的膨胀较为明显,有助于缓解溶解度的缺口。

然而,在高温环境下进行键合时,可能会出现Cu氧化、扩散到绝缘层或者底层元器件的热损伤等一系列可靠性问题。通常,非存储器元件的工艺环境要求低于350°C,存储器元件的工艺环境要求低于250°C。

3-4) 此外,在高温环境下可能会加剧翘曲和热应力,因此低温键合工艺的重要性变得更加突出。然而,在低温环境下,Cu膨胀不足,难以克服较小的溶解度缺口,这意味着Cu溶解度控制的要求更加严格。为了满足这一要求,需要优化CMP工艺,但由于影响溶解度和表面粗糙度的工艺参数较多,因此控制非常困难。

基于这种背景,针对低温环境和高键合强度的需求,已有研究开始探索新的绝缘材料作为SiO2的替代物。如前所述,在Cu/Oxide混合键合中,绝缘层的作用非常关键。为了形成高质量的Cu-Cu界面,绝缘层之间的键合强度必须足够强。完成晶圆键合后,经过退火处理,Cu-Cu区域会形成适当的键合能量,这一能量大约与硅破坏能量2.5 J/m2相当。

然而,SiO2对于Cu的扩散非常脆弱,且在超过300°C时,必须提供更高的温度才能达到所需的键合强度,这在热预算和可靠性方面有明确的限制。对此,IMEC的F. Inoue研究小组等人报告称,SiO2-SiO2键合在450°C以上退火时,尽管界面内观察到了部分空洞,但SiCN-SiCN则形成了没有缺陷的界面。

此外,SiCN不仅在250°C以下的低温环境中表现出比SiO2更高的键合强度,而且能够有效抑制Cu的扩散。IMEC的L. Peng研究小组等人发现,在250°C退火条件下,SiCN-SiCN的键合强度为2.3 J/m2,而同一工艺条件下SiO2-SiO2的强度为1.9 J/m2,显示出显著的差异。

这些研究小组根据ESR信号观测结果指出,这一差异的原因是碳悬挂键(Dangling Bond)。9-10) 在200°C和250°C退火处理的SiCN-SiCN样品中,悬挂键的密度明显较高。相反,SiO2-SiO2的样品在退火后几乎没有悬挂键,这表明SiO2-SiO2界面上的悬挂键形成效应较弱。

这一结果表明,SiCN中提高键合强度的因素是悬挂键的存在。一般而言,后端工艺(BEOL)中的纳米技术推荐在绝缘体表面使用屏蔽金属薄膜,以完全阻止SiOx基绝缘体的扩散。

因此,如果没有屏蔽金属,在两个Cu/SiOx表面键合时,Cu扩散引起的可靠性问题可能会带来风险,特别是在实现1μm以下的微小间距混合键合时,面临相当大的挑战。此外,当键合界面小于1μm时,可能会增加对准误差的概率,从而导致Cu与绝缘层接触的区域增多,进而减少形成实际电气连接的Cu-Cu区域。

因此,IMEC的Eric Beyne研究小组等人关注到SiCN的优点,并在现有的Cu/SiO2结构中加入SiCN薄膜,演示了具有数百nm级Cu pad和间距的Cu-Cu界面。

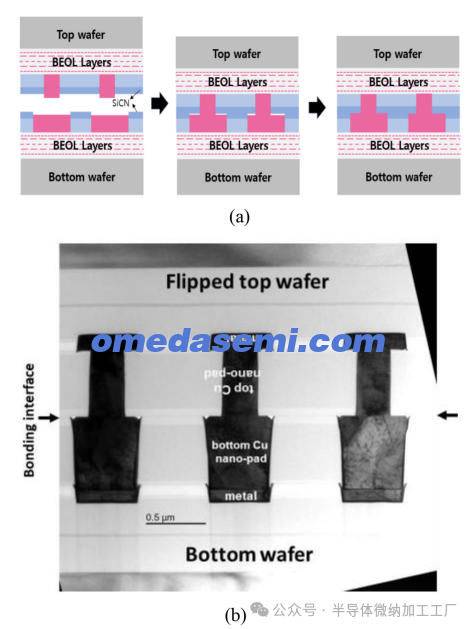

图 2. (a) 为直接混合键合设计的新型结构。突出的顶部 Cu 焊盘与较大的底部 Cu 焊盘对齐,从而补偿了对准误差,并提高了直接混合键合的精度。14)(b) Cu/SiCN 到 Cu/SiCN 混合键合界面的 TEM 观察。12)

12-13) 如图2(a)和(b)所示,通过增大顶部与底部pad的尺寸,最小化了浪费的区域,并且通过在SiO2上采用PECVD(等离子体增强化学气相沉积)方式沉积了100-150nm厚的SiCN薄层,形成了具有更高键合强度的界面。此外,针对传统结构中的溶解度问题,研究人员通过优化的CMP工艺技术,制作了一种具有突出的Cu表面的结构,以有效消除溶解度缺口。

14-15) 这意味着,为了获得突出的Cu表面,需要采用氧化物高度减小技术等优化的CMP工艺。

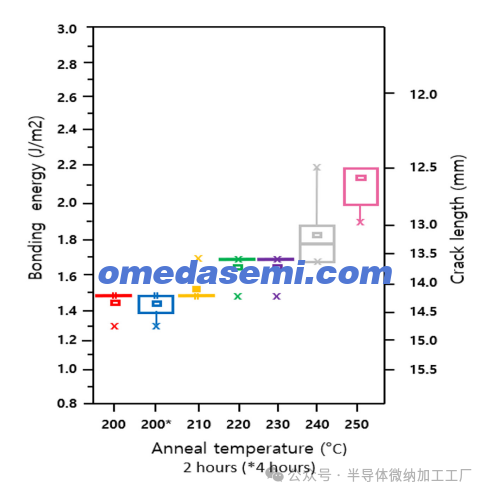

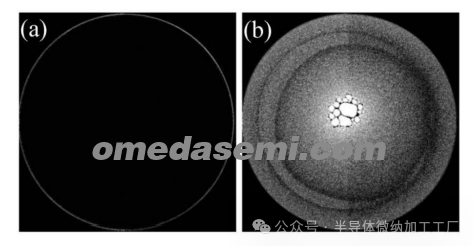

IMEC的Soon-Wook Kim研究小组等人报告称,这种Cu/SiCN结构的W2W混合键合与传统的Cu/SiO2结构相同,经过对准后,晶圆中心发生接触并形成初步键合。此外,经过初步接合后,进行退火处理时,SiCN表面在250°C的低温环境下展现出比SiO2更优越的键合质量(见图3)。14,16)

图3. 300mm SiCN-SiCN晶圆W2W键合能的测量结果。可以观察到,在250°C退火工艺后,键合能显著增加。14)

2.2. SiCN薄膜的特性与成分及沉积方式

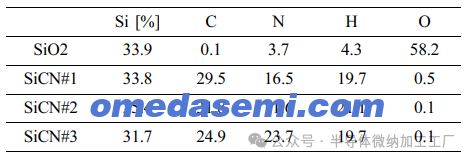

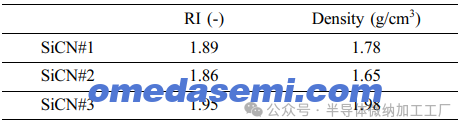

与SiO2相比,PECVD沉积的SiCN薄膜具有独特的特性,其中之一就是其氢含量显著较高(见表1)。这种氢含量使薄膜能够形成孔隙,从而能够吸附水分子。

Panasonic的Ueda研究小组等人报告了当SiCN薄膜应用于Si wafer与TEOS-SiO2之间时,水分子被吸附后,退火后产生的空洞明显减少的现象。通常情况下,TEOS-SiO2在高温退火处理中,TEOS中包含的水分子会以高压形式释放,导致界面内产生空洞。然而,该研究小组提出的结构中,暴露的水分子会氧化SiCN,并防止高压水分子释放气体,从而抑制了空洞的形成。

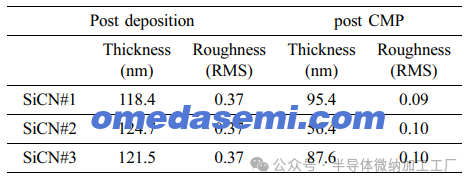

这种SiCN薄膜的成分会因沉积条件而有所不同,IMEC的L. Peng研究小组等人为更好地了解SiCN薄膜中的各组成成分,通过调节前驱体的压力来展示不同薄膜成分的结果。

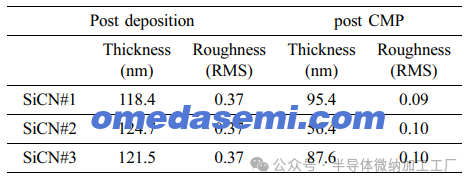

表 1. SiO2 和 SiCN 薄膜的 ERD 分析结果18)如表1所示,SiCN#2中含有最多的碳,而SiCN#3则比SiCN#1含有更多的氮。表3. 沉积和CMP工艺后测得的SiCN薄膜层厚度和粗糙度18) 此外,通过表2可以看出,SiCN#2的密度低于SiCN#1,这主要是因为碳含量较高的SiCN#2具有更多的孔隙。这一结果与National Taiwan University的S. Chattopadhyay研究小组等人的发现一致,他们报告了SiCN中碳成分比例越高,热扩散率值和密度越低的现象。

此外,通过表2可以看出,SiCN#2的密度低于SiCN#1,这主要是因为碳含量较高的SiCN#2具有更多的孔隙。这一结果与National Taiwan University的S. Chattopadhyay研究小组等人的发现一致,他们报告了SiCN中碳成分比例越高,热扩散率值和密度越低的现象。

这些薄膜的密度也会影响CMP工艺的处理结果,如表3所示,密度最低的SiCN#2表现出最高的去除率。也就是说,当SiCN薄膜中的碳含量过高时,在CMP工艺中可能会出现问题。相反,如果碳含量过低,Si-C键合断裂,形成的Dangling Bond数量减少,可能会导致初始键合能量变弱。此外,氮含量的增加会增强抑制Cu扩散的特性,正如之前提到的,这也是在混合键合结构中,能够提高可靠性和电气性能的关键因素。然而,氮含量的增加也意味着相对的碳含量减少,可能会导致Dangling Bond的减少。因此,适当调整薄膜成分比例是SiCN薄膜中一个重要的因素。

在表面粗糙度方面,无论是沉积后还是CMP工艺处理后,薄膜成分的密度特性似乎并未对其产生影响,得到了相似的值。这是SiCN的另一个特性,即其平滑表面,使得它在晶圆键合中作为一个重要的变量,具有优势。

KU Leuven的F. Nagano、IMEC的S. Iacovo研究小组等人通过研究沉积温度对SiCN薄膜密度的变化,保持其他工艺条件不变,在200°C和370°C条件下进行沉积。ERD分析显示,370°C沉积的SiCN薄膜仅包含Si、C、N和H,而200°C沉积的SiCN样品则检测到氧的存在,同时碳的含量略有增加,并被识别为SiCNO。此外,370°C沉积的薄膜只在表面出现氧化现象,而200°C沉积的薄膜则在整个体积内发生氧化,这与200°C沉积环境下低密度导致大气中的氧分子更容易渗透到薄膜内部的结果一致。FT-IR分析表明,200°C沉积的薄膜在800-1200 cm-1区域的Si-O峰强烈出现,表明空气中的氧或水分与密度较低的SiCN薄膜中的Si原子反应。

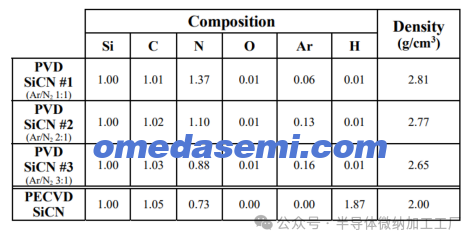

这些SiCN薄膜通常通过PECVD方式沉积。然而,传统PECVD的沉积温度通常超过350°C,这可能会对器件的可靠性产生负面影响。为了克服这一问题,前文提到的将温度降至200°C的方法会导致氢含量增加,从而使薄膜的密度降低,失去SiCN薄膜的一个重要优势——较高的机械强度。为了防止这种情况发生,需要通过热处理过程提高薄膜密度,但这也需要高温环境,并可能引发由于出气等原因的可靠性问题。因此,最近的研究正在进行PVD(物理气相沉积)沉积方法的研究,以解决沉积温度和薄膜密度的问题,Intel的Xavier F.Brun、Evatec AG的Patrik Carazzetti等人也报告了PVD和PECVD SiCN薄膜的研究结果。如表4所示,在PVD工艺中,气体混合物中N2:Ar比例的增加导致薄膜中氮的含量增加,而氧和氢的含量则减少到可忽略的水平。此外,随着PVD SiCN薄膜中氮含量的增加,薄膜的密度也相应增加,这有助于改善空洞或较高CMP薄膜去除率的问题,但如果密度过高,会导致其吸湿性能降低,因此需要适当调整气体比例。相对而言,PECVD SiCN的氢含量要高得多,相应地,密度也较低。因此,从薄膜密度质量和器件可靠性的角度来看,PVD沉积方式相比PECVD具有优势。

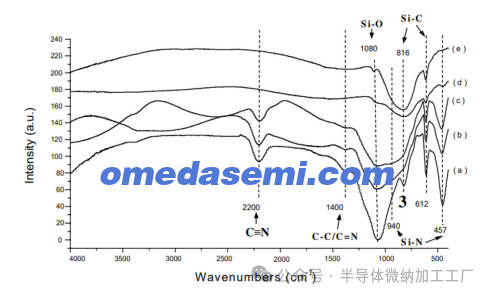

图 4. (a)室温、(b)400°C、(c)700°C、(d)1000°C、(e)1200°C 沉积的 SiCN 薄膜的红外光谱。23)兰州大学的Ziwei Ma、中央佛罗里达大学的Sundaram、通用汽车研发中心的Xingcheng Xiao等研究小组在CVD工艺下沉积薄膜时,使用SiH4–CH4–NH3–H2混合气体作为反应气体,并关注添加氢气现象,报告了在不同基板温度下(如常温、400°C、700°C、1000°C、1200°C)SiCN薄膜的研究结果。如前所述,SiCN薄膜中所含的氢会在退火时产生空洞,因此降低氢含量非常重要。研究结果表明,在RF溅射过程中,高纯度氮气被送入溅射腔体,并从分解的N2中生成氮原子。通过这些反应,氮原子与硅和碳原子反应,最终在样品中不会存在氢元素。这与PECVD方式沉积的SiCN薄膜有明确的区别。此外,通过不同基板温度下的IR光谱分析,SiCN薄膜的特征Si–C和Si–N键的峰分别出现在2200、612和457 cm-1,而Si≡C、Si≡N和Si≡O的键峰分别出现在816、940和1080 cm-1(见图4)。2.3. 等离子体表面处理效果

SiCN的一个关键因素是等离子体表面处理。通过适当的表面处理,正如前面提到的,Dangling Bond会形成,从而在常温环境下也能形成足够的键合界面。

这种等离子体处理可以增强粘附力,并形成10nm以下的薄SiOx层,许多研究表明,SiOx层具有亲水性表面,并且由于PECVD沉积过程中的硅醇基团等,它被认为是具有典型绝缘特性的材料。

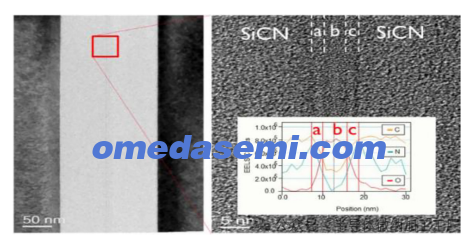

图 5. SiCN-SiCN 界面的 TEM 和 EELS 分析结果。该界面由厚度约为 4 nm 的 SiCO、N 耗尽区域 (b) 和两个相邻的混合成分区域 (a) 和 (c) 组成,每个区域的厚度为几纳米。14)

图 6. STEM-EELS 分析研究 SiCN-SiCN 键合界面处化学键性质的演变。14)

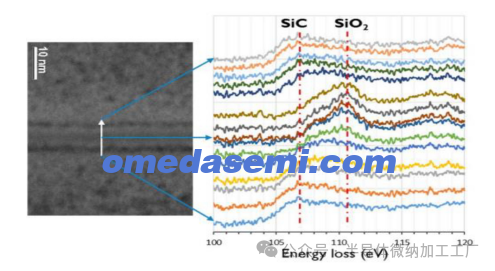

IMEC的E. Beyne研究小组等人指出,SiCN-SiCN界面表现出独特的特性,具有富含氧并且氮含量较低的界面层,在界面附近观察到Si-O和Si-C的键合(见图5和6)。当对SiCN表面进行等离子体处理时,Si-O和Si-C的键会被断开,形成Dangling Bond,从而使其具有比SiO2更高的键合能量。

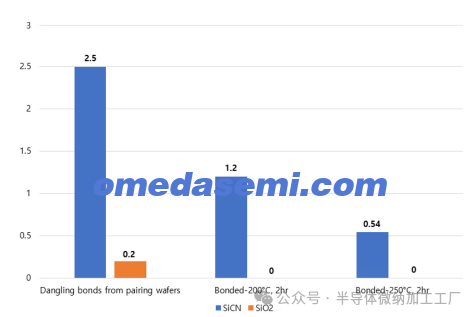

在键合后的晶圆上测得的总Dangling Bond密度,SiCN与SiO2之间存在较大差异,SiCN为2.4 × 10¹⁴/cm²,SiO2键合为0.2 × 10¹⁴/cm²。

在键合之后,SiCN-SiCN键合样品的Dangling Bond密度在200°C和250°C退火处理后有所下降,分别测得为1.2 × 10¹⁴/cm²和0.54 × 10¹⁴/cm²。相反,SiO2-SiO2界面的Dangling Bond贡献几乎为零。一个重要的点是,当SiCN样品在200°C条件下退火处理时,Dangling Bond密度发生变化,表明在键合和退火过程中,Dangling Bond的减少主要发生在SiCN-SiCN界面(见图7)。

图 7. 不同退火条件下 SiCN 和 SiO2 键合前后的悬挂键密度。33)比较晶圆键合强度的结果可以看到,在250°C条件下获得的键合强度明显高于200°C条件下的强度,这同样表明显著的Dangling Bond减少在促进键合反应中起到了重要的化学作用。

同时,国立台湾大学的L.C Chen研究小组等人通过XPS分析SiCN薄膜中的Si(2p)、C(1s)、N(1s)峰时,发现与Si-N和C-N峰不同,Si-C峰未被检测到,这表明了一种特殊的趋势。

尽管这种现象的明确原因尚未找到,但它是理解SiCN薄膜的键合敏感性及其机制的一个重要现象。此外,国立台湾大学的C.C. Huang研究小组等人报告称,当没有NH3气体时,沉积薄膜中的Si(2p)谱图显示Si-C键最强,而当NH3气体流量缓慢增加时,显著的相变被观察到。随着NH3流量的增加,薄膜中的主要部分转化为Si-N键。相反,Si-C峰完全消失,并且在100.3eV处没有与Si-C键相关的峰,这与前面提到的结果一致。

此外,在晶圆键合的初始接触阶段,表面生成的OH基团通过氢键作用形成接合。

国立台湾大学的C.C. Huang研究小组等人还报告称,通过CVD方法沉积薄膜时,大多数情况下,薄膜内的氢含量无法避免。

这种氢含量有助于C-H、N-H和Si-H键的形成,最终导致Dangling Bond的去除。

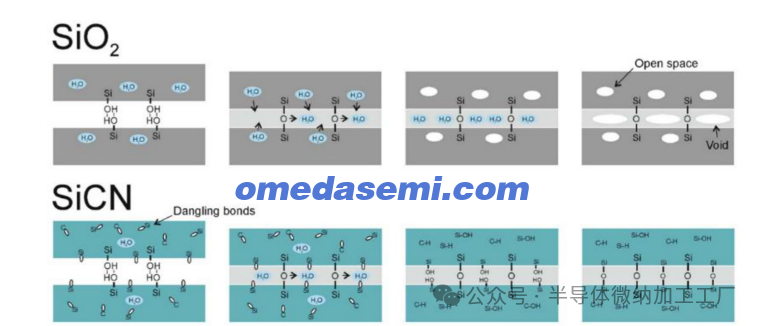

因此,整理SiCN-SiCN键合的机制,可以得出以下结论:首先,在等离子体表面处理过程中,绝缘体表面上的OH基团被激活。然后,当晶圆对在常温下结合时,表面的Si-OH基团通过氢桥键合捕获界面内的水分子,固定的水分子随着时间的推移,会向界面外部移动或扩散。此外,当Si-OH基团相遇时,硅醇键会形成,水分子被释放,并发生化学反应。以下是该反应的化学式:

Si - OH + OH - Si → Si - O - Si + H₂O

因此,SiO2-SiO2和SiCN-SiCN都具有由OH基团引起的亲水性表面,因此在界面上会发生类似的反应。然而,KU Leuven的F. Nagano研究小组等人指出,SiCN在抑制空洞生成方面比SiO2更为有效,并且通过研究结果表明,这一差异源于SiCN相较于SiO2具有更多的Dangling Bond(悬挂键)(见图8)。换句话说,研究结果表明,SiCN-SiCN的高键合能量是由上述的Dangling Bond和表面OH基团引起的。

图8. SiO2和SiCN空洞形成机理模型示意图。37)

三星电子的Chung-Sun Lee研究小组等人分析了对SiCxNy薄膜分别施加Ar、N2、O2等离子体处理后,测得的亲水性表面及其相应的键合强度。亲水性表面通过接触角分析得到了确认,结果显示SiCxNy的表现根据所用的等离子气体类型差异较大。最终,O2和N2气体比Ar气体更有效地断开SiCxNy表面上的碳氢化合物键,并转化为氢气。同时,最大的键合能量是在O2等离子体处理下得到的2.4 J/m²,并且在所有其他等离子体条件下,SiCxNy表现出比其他绝缘体更高的键合能量。

图 9. SiCxNy 薄膜 SAM 图像 (a) 室温键合,未经等离子处理 (b) 250°C、2 小时退火后的结果(界面气泡)。7)

此外,这样键合的晶圆在进行研磨等后续工艺时,必须具有足够的键合能量,否则可能会出现问题。因此,还需要进行额外的退火工艺。然而,与其他绝缘体不同,在未进行等离子体处理的SiCxNy薄膜中,退火过程中观察到了界面气泡缺陷现象。图9(a)展示了退火处理前在常温下初始键合形成的SiCxNy-SiCxNy界面的扫描声学显微镜(SAM)图像,未出现空洞和气泡缺陷。然而,如图9(b)所示,在250°C、2小时退火处理后,界面内出现了气泡。研究小组推测,高温下形成气泡缺陷的主要原因是由碳化物形成的疏水性表面。

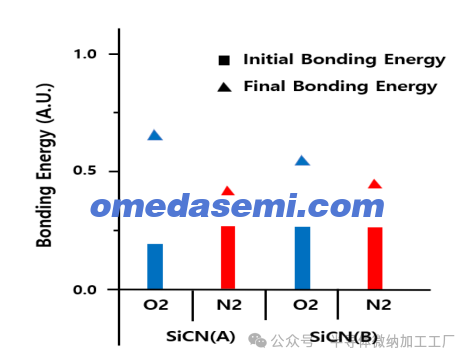

三星电子的Seongmin Son,成均馆大学的Geun Young Yeom等人分析了两种碳含量不同的SiCN薄膜(SiCN(A)和SiCN(B))在分别进行N2和O2等离子体处理后的效果。键合能量可大致分为两类:一是晶圆键合后的初始键合能量,二是退火后形成的最终键合能量。

研究结果表明,SiCN(A)的初始键合能量在N2等离子体处理的晶圆上高于O2等离子体处理的晶圆。而SiCN(B)则几乎没有受到等离子气体类型的影响。另一方面,在最终键合能量方面,退火处理后,最终的键合能量比初始键合能量高出1.6到9.3倍,显示出与初始键合能量截然不同的趋势。也就是说,O2等离子体处理的SiCN-SiCN键合的最终键合能量高于N2等离子体处理的键合,且表现出与初始键合能量相反的趋势。

图10. SiCN薄膜的初始键合能随等离子体类型的变化以及退火后的最终键合能。39

此外,通过比较O2等离子体处理的SiCN(B)和SiCN(A)的最终键合能量,发现SiCN(B)的最终键合能量比SiCN(A)低约15%。这表明,沉积的SiCN薄膜的特性会受到等离子体引起的表面氧化的影响。SiCN(B)的表面氢含量比SiCN(A)高,这也表明在N2等离子体处理时,晶圆表面形成了单一的OH基团,从而提高了最终的键合能量。然而,在O2等离子体处理时,氢气与氧气反应生成水,最终导致退火后界面内的空洞生成,从而降低了最终键合能量(见图10)。

本文介绍了SiCN绝缘体的特性以及当前的研究趋势。在混合键合中,为了确保退火处理后Cu垫之间能够良好地形成电气连接,如前所述,需要在绝缘体键合区域提供足够的键合能量。SiCN具有能够克服当前SiO2面临的可靠性问题、实现低温环境以及具有更高键合强度的优势,因此在未来混合键合领域中,SiCN将成为一个非常关键的因素。为了实现优良的Cu/SiCN混合键合,需要适当调整碳、氮、氢等元素的含量比,以优化CMP工艺中的薄膜密度。沉积于高温下的薄膜,由于其致密的结构特性,可以防止在CMP处理中薄膜去除超过目标厚度,并抑制内部氧化层的形成等优点。然而,这也会由于热预算的增加而损害下层器件的特性,因此,研究能够在低温下确保优秀薄膜特性的沉积技术同样重要。此外,在实现高键合强度时,Dangling Bond和OH基团的化学反应非常重要,这些反应受沉积温度、成分比例、前驱体、等离子体气体类型和退火温度等工艺环境和条件的影响,表现出非常复杂和多样的趋势。因此,必须清楚理解这些元素,并能够适当地控制它们。如果能够解决这些技术难题,预计通过将SiCN应用于微间距3D互连,可以解决现有绝缘体键合领域所面临的问题。作者;Yeonju Kim, Sang Woo Park, Min Seong Jung, Ji Hun Kim, and Jong Kyung Park† Department of Semiconductor Engineering, 单位;Seoul National University of Science and Technology, 232, Gongneung-ro, Nowon-gu, Seoul, 01811, Korea