摘要:提出了一种超紧凑型隔离器,基于铝掺钴铁氧体薄膜与具有磁光活性的硅微环谐振器的集成。所采用的磁光材料具有强烈的剩余磁化强度,使得该设备可以在没有任何外部磁化元件的情况下工作,并且设备的占地面积仅为150 µm²。通过使用与绝缘体上硅平台兼容的常规工艺制造了原型芯片,并在1557.6 nm波长处实现了最大7 dB的隔离比。据我们所知,这是迄今为止演示的最紧凑的光学隔离器,适用于具有极高集成密度的全光电路。

1. 引言

隔离器是一种非互易元件,可防止光子集成电路 (PIC) 中因负载不匹配而产生的背向反射光。这些寄生反射可能会干扰信号源(如半导体激光器)的稳定运行,在最坏的情况下,可能会损坏电路中最敏感的元件 [1–5]。

隔离器的非互易特性通常与磁光 (MO) 材料在其设计中的使用所提供的时间反转对称性破坏有关。然而,典型的 MO 材料仅在磁化被外部磁体饱和时才会显示出有用的活性 [6–9]。此外,在传统半导体激光器中,TE 偏振光通常占主导地位,而且更容易实现 [10–13],而目前将 MO 材料集成到绝缘体上硅 (SOI) 衬底的技术有利于设计以 TM 模式运行的非互易器件 [14–16]。例如,[17, 18] 提出了在 1550 nm 波长下工作的 TM 模式隔离器。这些器件由 SOI 微环谐振器 (MRR) 组成,该谐振器与铈取代的钇铁石榴石 (Ce:YIG) 制成的 MO 层粘合在一起。Ce:YIG 薄膜的磁化被这些组件中的金微带线圈饱和,它们的占地面积在几千平方微米的范围内。[19] 提出了一种在 1550 nm 波长下工作的 TE 模式光隔离器。该器件由一个非对称 SOI 环形谐振器组成,Ce:YIG 层通过晶圆键合技术集成在该谐振器上。谐振器显示 TM 模式的非互易相移 (NRPS),两个内置 TE-TM 偏振旋转器可实现 TE 模式的隔离。该器件在单向磁场下工作,其占地面积估计为 130,000 µm2。[17–19] 中提出的隔离器设计中对外部磁铁的要求不利于紧凑性并引入了封装问题,因为这些元件通常很笨重。此外,电磁铁对光子隔离器的操作提出了额外的挑战,例如焦耳加热引起的波长失谐。关于 [17–19] 中提出的隔离器设计,需要偏振旋转器以便与支持 TE 模式的半导体激光器结合使用,以及 TM 模式在介电波导中的较低限制(与 TE 模式相比),也影响了这些设备的进一步小型化。此外,剩余的厚(Ca、Mg、Zr)取代的钆镓石榴石 (SGGG) 基板(其上生长 Ce:YIG 膜)对 [17–19] 中提出的隔离器设计提出了额外的挑战。在 [17, 18] 中介绍的情况下,需要额外的抛光工艺来减薄 SGGG 基板并减小 MRR 和电磁结构之间的距离。另一方面,[19] 中介绍的隔离器的 SGGG 层既没有变薄也没有被移除,这阻碍了组件的进一步小型化。

在本文中,我们介绍了一种新型隔离器,用于 1550 nm 波长的 TE 模式,其占用空间仅为 150 µm2,是目前报道过的最小光子隔离器。所提出的装置比 [17–19] 中提出的设计小两到三个数量级,其超紧凑尺寸主要归因于利用了由分子式为 CoAl0.57Fe1.43O4 (CAFO) 的铝取代钴铁氧体薄膜,即使没有任何偏置磁铁,它也显示出高 MO 活性。尽管也采用 CAFO 薄膜作为 MO 介质,但 [20] 中提出的 TM 模式隔离器的占用空间要大得多(3,053 µm2)。具体而言,TM 模式的较低光学限制需要具有更大弯曲半径的结构,因此,在这种情况下很难进一步减少占用空间。所提出的隔离器具有 TE 模式的本机操作(无需偏振旋转器),以及 MO 膜与隔离器结构单片集成而没有剩余厚基板,也有助于减小器件占用空间。

2. 隔离器设计和工作原理

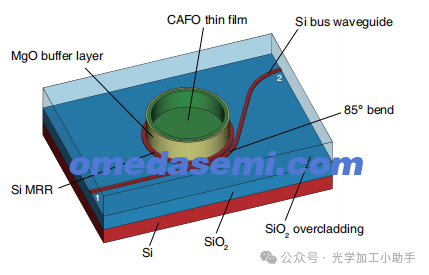

建议的无偏置光子隔离器基于 SOI 基板,其中图案化了 MRR 和总线波导。整个结构被二氧化硅 (SiO2) 覆盖,其中包含一个用于沉积 200 nm 厚的 CAFO 膜的窗口,如图 1 所示。沉积的 CAFO 薄膜的强剩磁确保了器件的无偏置操作,即无需任何外部磁体。[20] 中介绍了对 CAFO 薄膜的 MO 特性的全面研究,包括材料损失和磁滞回线的测量。

图 1. 无偏光子隔离器示意图:(a)透视图和(b)横截面图。

CAFO 薄膜的沉积由预沉积的 20 nm 厚的氧化镁 (MgO) 缓冲层辅助。

MgO 层降低了 CAFO 薄膜和 Si 基底之间的晶格失配,并允许沉积具有较低损耗的高度定向 CAFO 薄膜 [20, 21]。

MRR 的横截面尺寸为 480 nm × 220 nm,而总线波导的横截面尺寸为 400 nm × 220 nm。环形谐振器的半径为 5 µm,它支持 1550 nm 波长附近的两个反向旋转 TE 模式,由于沉积的 CAFO 薄膜引起的 NRPS 效应,其简并被消除。通过在其中一个 MRR 谐振波长下操作,可以实现 TE 模式的隔离。

时间耦合模式理论 (TCMT) 方程可用于分析器件操作。例如,[2] 中描述的非互易器件的 TCMT 方法允许人们推导出计算 S 参数 S21(ω) 和 S12(ω) 的公式。基于 TCMT 的器件分析在附录 A 中介绍。

考虑典型直总线波导的器件的初步计算模拟表明,总线波导和 MRR 之间的间隙 (g) 应为 15 nm,以最大化所提设计的隔离比 (IR)。然而,考虑到现有制造方法的限制,如此小的间隙是不可行的。

为了能够制造该器件并补偿由于间隙较大而导致的总线波导和 MRR 之间的较低耦合,可以考虑使用跑道谐振器,但代价是器件占用空间更大,自由光谱范围 (FSR) 更窄。或者,我们设计了一个弯曲角度为 θ 的波导弯曲,以解决这个问题,而不会进一步增加器件占用空间。我们进行了参数优化,以确定最大化器件 IR 水平的 θ 和 g 值,结果为 θ = 85◦ 和 g = 220 nm。

值得注意的是,CAFO 和其他 MO 材料(如 Ce:YIG)都可以诱导基于 MRR 的光子隔离器运行所需的 NRPS 效应。然而,CAFO 薄膜的吸引人的特征(例如其强大的剩磁和通过溅射技术直接集成到 SOI 基板上)使其更适合开发具有更小占用空间、更简单操作和更容易制造的光子隔离器。

3. 计算模拟

使用全波电磁求解器 CST Studio Suite 对隔离器设计进行了三维计算模拟,以确认设备的可行性并获得 IR 和插入损耗 (IL) 水平方面的最佳设计。

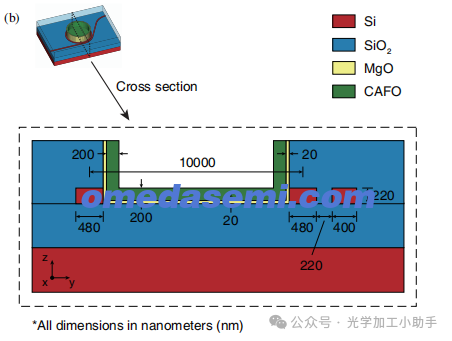

图 2. 通过计算模拟获得的隔离器的 S 参数。

我们在计算模拟中考虑到 Si、SiO2 和 MgO 的折射率依次为 3.46、1.45 和 1.72 [22–24]。此外,我们数值计算中的 CAFO 材料的折射率、消光系数和法拉第旋转系数分别等于 2.4、0.014 和 22,000 度/厘米 [20, 25]。计算出的 S 参数 S21(λ) 和 S12(λ) 如图 2 所示。在 1538.9 nm 波长处,IL 和 IR 水平分别为 5.6 dB 和 39.8 dB,波长分裂 (∆λ) 等于 0.32 nm。此外,计算出的 MRR 的 FSR 约为 18.5 nm,每个 MRR 谐振波长周围的设备带宽(定义为 10 dB IR 级别)为 23 GHz。

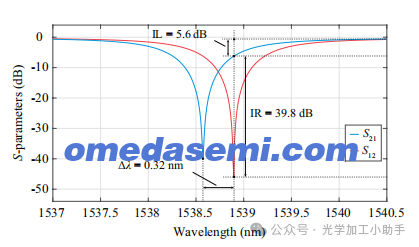

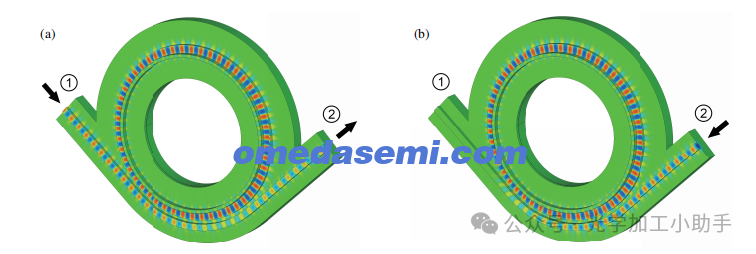

图 3. 输入信号在 1538.9 nm 波长下的 Hz 分布,输入信号施加到 (a) 端口 1 和 (b) 端口 2。

图 3 显示了 1538.9 nm 波长下的 Hz 分量分布。从图 3(a) 可以验证,施加到端口 1 的输入信号被传输到端口 2,因为在这种情况下,输入信号和 MRR 模式之间的耦合很弱。另一方面,如图 3(b) 所示,施加到端口 2 的输入信号与此波长下的 MRR 顺时针旋转模式强烈耦合,导致端口 1 的高隔离度。图 3 中省略了 SiO2 覆层,以便更好地可视化组件内的场分布。

4. 器件制造

图 4. 无偏光子隔离器的制造步骤。

图 4 给出了隔离器的制造工艺流程。原型芯片的制造使用了由 Si (220 nm)/SiO2/Si 层组成的 SOI 晶片,该晶片上预先沉积了 SiO2 掩模层。

首先,在 SOI 晶片上涂上 ZEP520A 电子束 (EB) 光刻胶,并执行 EB 光刻 (EBL) 步骤以对抗蚀剂进行图案化。随后,分别在 CF4 和 SF6 等离子体中通过反应离子蚀刻 (RIE) 对 SiO2 掩模层和 220 nm 厚的 Si 层进行图案化。

使用 HF 溶液去除剩余的 SiO2 掩模层并完成隔离器结构的图案化。

图 5. 通过光学显微镜获得的制造芯片的顶视图(CAFO 沉积之前)

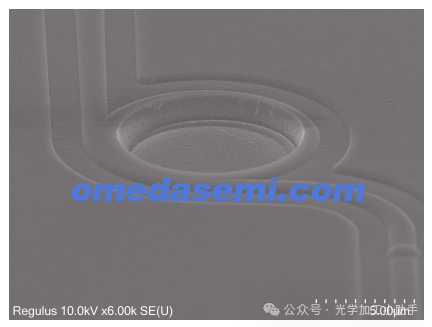

图 6. 制造的芯片的 SEM 透视图。

之后,我们采用等离子体增强化学气相沉积 (PECVD) 在图案化晶片上沉积 1 µm 厚的 SiO2 包层。使用 AZ5218E 抗蚀剂和 CF4 等离子体中的 RIE,通过无掩模光刻 (PL) 在包层上蚀刻出用于沉积 CAFO 薄膜的窗口。最后,按照 [20] 中描述的程序,通过 RF 磁控溅射在窗口内沉积 20 nm 厚的 MgO 缓冲层和 200 nm 厚的 CAFO 薄膜。图 5 和图 6 分别显示了通过光学显微镜获得的制造芯片的顶视图和使用扫描电子显微镜 (SEM) 捕获的透视图。这些图像一起提供了该设备关键元素的清晰概述。

5. 器件特性

通过将来自透镜光纤的 TE 偏振光耦合到 Si 总线波导的两侧,测量器件的透射光谱,以测量器件在前向和后向传播方向上的透射率。我们采用了端射耦合方案,并辅以自动对准系统,并使用切割锯创建光纤-芯片-光纤耦合的面 [26]。

此外,在透射率测量之前,每个芯片碎片都已通过产生 15 kOe 平面外磁场的电磁铁磁化约 1 分钟,以使 CAFO 薄膜的磁化饱和。CAFO 的剩磁促进了

MRR 反向旋转谐振之间的波长分裂,并确保设备的无偏差操作。

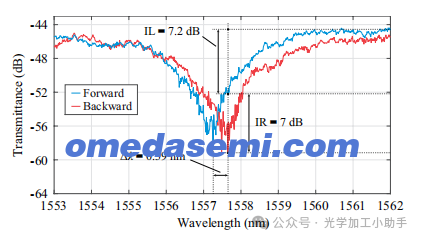

图 7. 制造的隔离器的透射光谱。

图 7 显示了两个传播方向的 TE 模式测量透射光谱。在 1557.6 nm 波长下,IL 和 IR 水平分别为 7.2 dB 和 7 dB。谐振器 FSR 约为 18.2 nm,∆λ 参数为 0.39 nm。必须强调的是,图 7 中显示的透射光谱对应于原型芯片中包含的几个样品中 IR 水平最高的样品。

6. 讨论

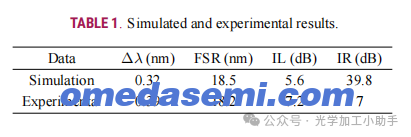

为了进行比较,表 1 总结了从计算模拟和实验测量中获得的结果。尽管模拟结果和实验结果显示 ∆λ、FSR 和 IL 参数具有良好的一致性,但制造的隔离器的 IR 水平明显低于器件模拟预测的值。这种差异可能与沉积的 CAFO 薄膜的高吸收损耗以及制造的芯片的结构缺陷有关

在 1550 nm 波长处,CAFO 的吸收损耗为 dB/µm 数量级 [20],远大于 Ce:YIG 的吸收损耗,后者为 dB/cm 数量级 [17]。一般而言,损耗越高,MO MRR 结构的谐振重叠度越高,IR 水平越低。

然而,Ce:YIG 的法拉第旋转系数在 1550 nm 波长处要小得多(约 4,500 deg/cm)[17]。

此外,生长 Ce:YIG 薄膜的厚 SGGG 基板占用面积相对较大,需要额外的键合后制造工艺,而 CAFO 薄膜可使用缓冲层(例如 MgO 或 ZnO)直接沉积在 SOI 基板上 [20],从而减小器件占用空间并降低制造复杂性。最后,与 CAFO 薄膜不同,Ce:YIG 薄膜需要外部磁体才能表现出显著的 MO 活性。

因此,在设计非互易光子器件时,使用 Ce:YIG 和使用 CAFO 薄膜之间存在权衡。我们之所以选择 CAFO 材料,是因为它可以实现更紧凑、更易于制造的隔离器设计。

至于隔离器的制造,SiO2 覆层中蚀刻的窗口与 MRR 的对齐非常具有挑战性,微小的偏差就会降低 NRPS 效应的幅度。此外,Si 元件的表面粗糙度会导致不必要的光散射,从而导致性能下降 [27, 28]。

虽然它没有达到 20 到 30 dB 范围内的 IR 水平,就像 [17–19] 中介绍的隔离器一样,但建议的隔离器的紧凑性提高了两到三个数量级。此外,通过元素替代 [29] 和使用不同的缓冲层 [30] 进一步改善 CAFO 薄膜的质量,以及优化制造工艺条件,可以潜在地提高器件性能。

本文未涉及的一些问题,例如 CAFO 特性的温度依赖性和所提出的器件的长期稳定性,可以在未来的研究中进行探索。

7. 结论

总之,已经展示了一种基于将 CAFO 薄膜单片集成到硅 MRR 结构的新型 TE 模式光子隔离器。通过利用与 SOI 平台兼容的制造工艺,我们制造了一个原型芯片,在 1557.6 nm 波长处测得的隔离率为 7 dB。

沉积的 CAFO 薄膜的高剩磁使建议的光子隔离器的无偏置操作成为可能。消除偏置磁铁、采用 TE 模式的原生操作(无需偏振旋转器)以及 CAFO 层的单片集成(没有剩余基板)使隔离器设计更简单,占用空间更小。与需要外部磁铁的传统隔离器设计相比,所提出的光子隔离器的占用空间(约 150 µm2)要小两到三个数量级。据我们所知,这是迄今为止展示的最紧凑的隔离器,大规模光子集成电路可以从中受益。

文章名:Ultra-Compact Photonic Isolator Based on Bias-Free Magneto-Optical Thin Films

作者:Gianni Portela1, 2, *, Yisheng Ni1, Kotaro Sato1, Yuya Shoji1, and Hugo E. Hernandez-Figueroa2 1

单位:Department of Electrical and Electronic Engineering, School of Engineering, Institute of Science Tokyo

2-12-1, Ookayama, Meguro-ku, Tokyo 152-8550, Japan 2

School of Electrical and Computer Engineering, University of Campinas, Campinas, SP 13083-852, Brazil